目录

一、实验要求

数字上变频芯片/数字下变频芯片功能软件仿真和验证;基于 Matlab 或其他编程语言(例如 C 或者 C++)实现 GC4016 或 AD9852 芯片中信号处理部分的功能仿真;如果用 RTL 语言完成功能实现,可加分;

二、应用背景

在超外差接收机中,通常需要将射频信号通过一次或几次模拟下变频转换到中频上,在中频对信号进行数字化,然后再进行数字下变频。

数字下变频(Digital down converter,DDC)指的是接收机中经过混频后得到的中频信号比原始信号的频率低的一种混频方式,中频信号转换为基带信号。

为什么说数字下变频是软件无线电(SDR)的核心技术之一?不妨作此假设,如果有一个ADC接收到一个高频信号,而所需信号以某种复杂的方式调制在该高频信号中,假如直接采样,DSP处理器的采样频率需与ADC匹配,常规DSP难以承受;但如果利用 DDC对ADC接受的高频信号进行下变频,则可以大大降低采样率同时得到有用信号,数字下变频以较少的采样率得到有用的信号,在软件无线电中起着十分重要的作用。

三、基本原理

3.1 任务分析

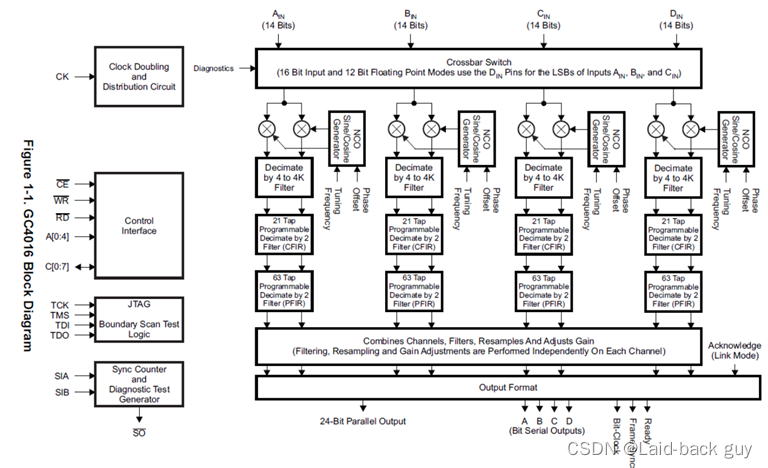

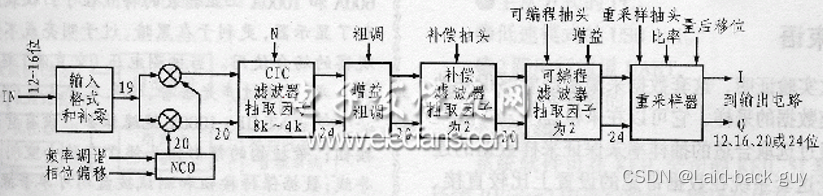

本次实验拟对数字下变频芯片功能软件仿真和验证。上图为数字下变频器GC4016的原理框图,其中四个数字下变频通道中每一个通道的数字信号处理原理框图如下图所示

观察GC4016芯片中信号处理部分,其主要操作包括采样、混频、数字滤波、抽取

3.2 基本原理

DDC即在数字系统中对信号进行下变频,实现从中频信号到基带信号的转变。用本振信号与输入的中频信号混频,得到一个高频信号与低频信号,用一个低通滤波器对信号进行滤波即可将信号解调出来。

数字下变频主要操作包括采样、混频、数字滤波、抽取,其主要由数字控制振荡器(NCO)、混频器(mixer)、滤波器(filter)等部分组成。

以上几部分分为两个基本模块数控振荡器NCO混频模块和抽取滤波模块。其中NEO模块用于产生本地振荡信号并于输入信号相乘,完成混频操作。

抽取滤波模块常用的结构是积分梳妆抽取滤波器(CIC)级联后再与多级半带滤波器(HBF)级联,完成抽取滤波操作。如果信号带宽较宽,抽取倍数不大,可以直接采用FIR低通滤波器。

数字下变频(DDC)的结构简图如图所示:

图片来源:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?