`timescale 1ns/10ps

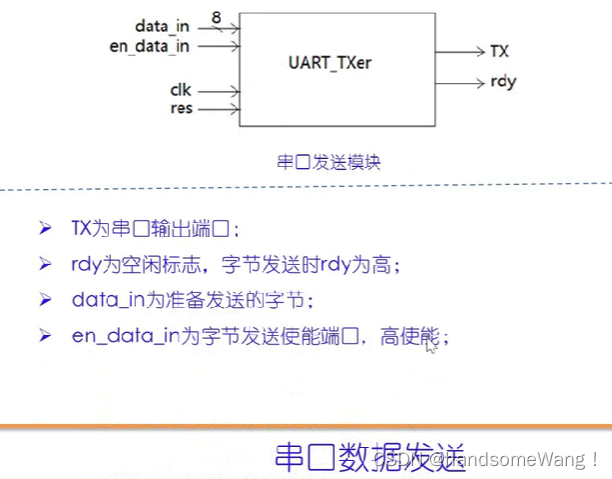

module uart_txer(

clk,

res,

data_in,

en_data_in,

TX,

rdy

);

input clk,res;

input[7:0] data_in;

input en_data_in;

output TX;

output rdy; //读使能

reg rdy;

reg[3:0] state;//状态位

reg[9:0] send_buf;

reg[9:0] send_flag;

reg[12:0] con;//数据间隔计数器

assign TX=send_buf[0];//发送位

always@(posedge clk or negedge res) begin

if(~res) begin//复位

state<=0;

send_buf<=1;

con<=0;

send_flag<=10'b10_0000_0000;

rdy<=0;

end

else begin

case(state)

0: begin//状态0,初始状态

if(en_data_in) begin

send_buf<={1'b1,data_in,1'b0};

send_flag<=10'b10_0000_0000;

rdy<=1;

state<=1;

end

end

1: begin//状态2,循环八次将,将send_buf中的数据法中出去

if(con==5000-1) begin

con<=0;

end

else begin

con<=con+1;

end

if(con==5000-1) begin

send_buf[8:0]<=send_buf[9:1];//sned_buf与send_flag同步循环

send_flag[8:0]<=send_flag[9:1];

end

if(send_flag[0]) begin//send_flag第0位为1,此时说明send_buf数据按位循环结束

state<=0;

rdy<=0;

end

end

endcase

end

end

endmodule

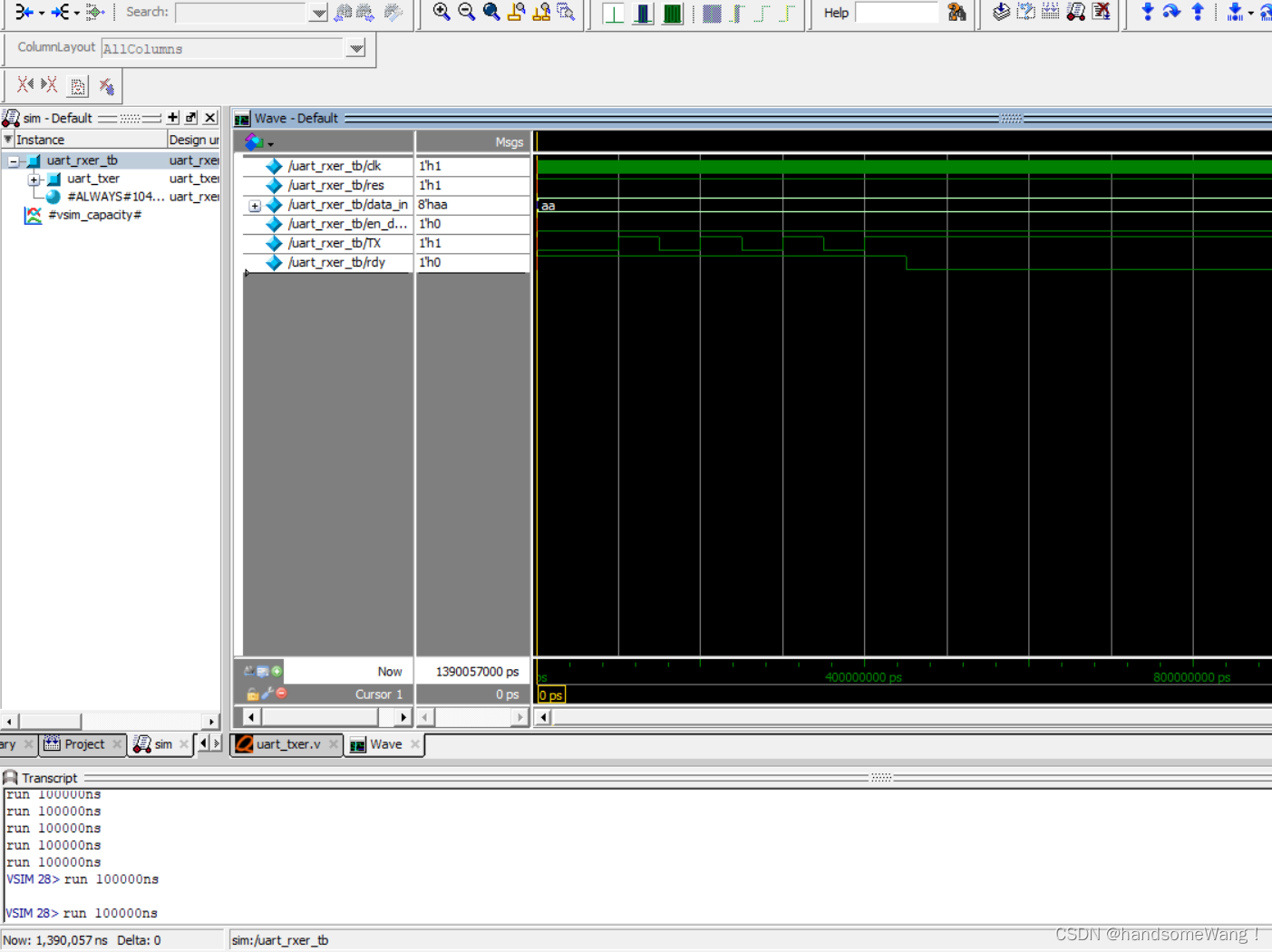

测试平台

module uart_rxer_tb;

reg clk,res;

reg[7:0] data_in;

reg en_data_in;

wire TX;

wire rdy;

uart_txer uart_txer(

clk,

res,

data_in,

en_data_in,

TX,

rdy

);

initial begin

clk<=0;res<=0;data_in<=8'haa;en_data_in<=0;//初始化数据

#17 res<=1;

#30 en_data_in<=1;//开启一下使能位

#10 en_data_in<=0;

#80000 $stop;

end

always #5 clk<=~clk;

endmodule

仿真结果:(多跑一些时间)

2378

2378

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?