1. FIFO IP核的概念

FIFO 的英文全称是 First In First Out,即先进先出。是一种先进先出数据存储、缓冲器,我们知道一般的存储器是用外部的读写地址来进行读写,而FIFO这种存储器的结构并不需要外部的读写地址而是通过自动的加一操作来控制读写,这也就决定了FIFO只能顺序的读写数据

1.1 FIFO IP的用途

常被用于数据的缓存,或者高速异步数据的交互,即跨时钟域信号传递。

1.2 同步FIFO和异步FIFO

同步FIFO:读和写属于同一个时钟。一般作为数据的一个缓冲,相当于一个buffer。

异步FIFO:读写属于不同的时钟,有两个作用,一个是实现跨时钟域数据传递,另一个作用是实现不同数据宽度的数据接口。

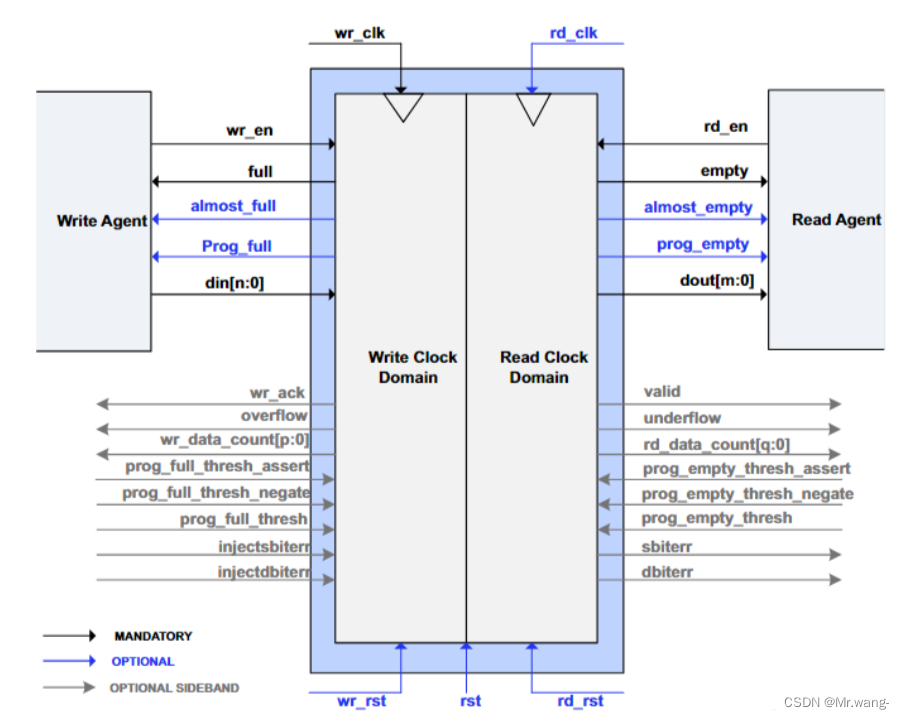

1.3 FIFO IP核的结构

1.4 主要参数

| 写数据参数: | 读数据参数: |

| wr_en:写使能 | rd_en:读使能 |

| wr_clk:写时钟 | rd_clk:读时钟 |

| wr_rst:写复位 | rd_rst:读复位 |

| full:写满 | empty:读空 |

| almost_full:提醒即将满 | almost_empty:提醒即将读空 |

| prog_full:可编程满信号。可以和上面一个将满做个对比,这个信号的存在允许我们设置一个阈值来判断FIFO还有多少空间,它在FIFO剩余空间大于等于生效阈值时生效,小于等于失效阈值时失效 | prog_empty:可编程空信号。当FIFO中的数据小于等于生效阈值时,该信号就会生效。超过阈值时,就会失效。 |

| din:数据输入 | dout:数据读出 |

FIFO 的宽度:FIFO存储的数据宽度,一次读写操作的数据位数N bit。

FIFO 的深度:FIFO 能存储多少个数据,即存储多少个宽度为 N bit 位的数据。

空标志:empty。FIFO 已空时由 FIFO 的状态电路发出的一个信号,以阻止 FIFO 的读操作继续从 FIFO中读出数据而造成无效数据的读出,当FIFO为空的时候将不能进行数据的读出。

满标志:full。FIFO 已满或将要写满时由 FIFO 的状态电路发出的一个信号,以阻止 FIFO 的写操作继续向 FIFO 中写数据而造成溢出,当FIFO中的数据满了以后将不再能进行数据的写入。

读时钟:读 FIFO 时所遵循的时钟,在每个时钟的上升沿触发。

写时钟:写 FIFO 时所遵循的时钟,在每个时钟的上升沿触发。

2. 两种场景

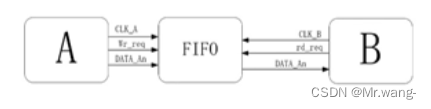

2.1 跨时钟域

设备A的时钟(100MHz)和设备B的时钟(50MHz)不同,此时先将设备A的数据写到FIFO中,然后设备B从FIFO中读取数据。

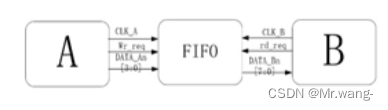

2.2 数据位宽不一致

设备A的数据宽度为[7:0],一共8位。设备B的数据宽度为[15:0],一共16位。此时存储器A的数据不能直接写到设备B。此时先将设备A的数据写到FIFO中,然后设备B从FIFO中读取数据。

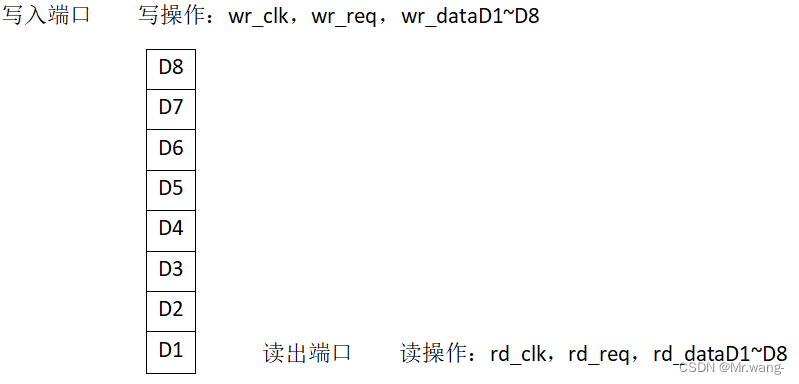

3. 先入先出

写数据时,第一个数据D0占据地址1,第二个数据D1占据地址2,… ,第N个数据D11占据地址N(N=12)。写数据需要的输入信号有:①写时钟:wr_clk;②写使能:wr_req;③写数据:wr_data,D0_D11。

读数据时,首先读地址1的数据D0,此时D1进入地址1,其余的数据的地址也减1。第二次读取数据时,首先读地址1的数据D1,其余的数据的地址减1。读数据需要的信号有:①读时钟:rd_clk;②读使能:rd_req。输出为读出的数据: data_out。

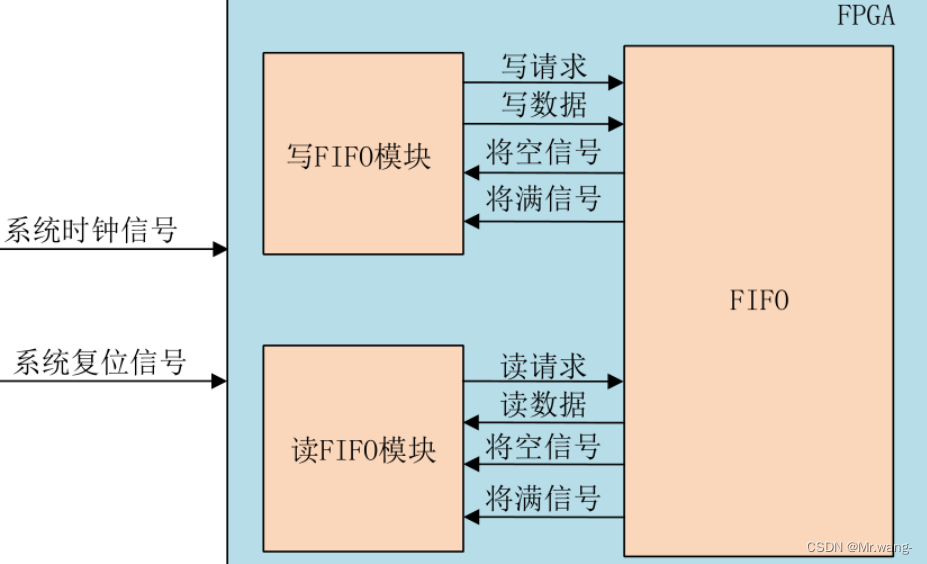

4. 模块框图

模块框图分别包含 FIFO IP 模块、写 FIFO 模块、读 FIFO 模块以及顶层模块四部分,写 FIFO 模块依次往 FIFO 中写数据,FIFO 会反馈出空信号和将满信号,同样的读 FIFO 模块也是这样。

3. 时序

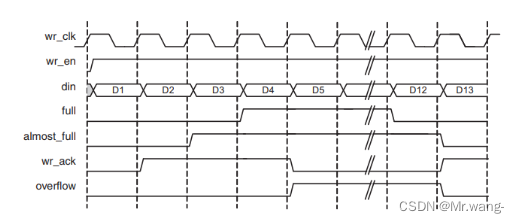

写时序:

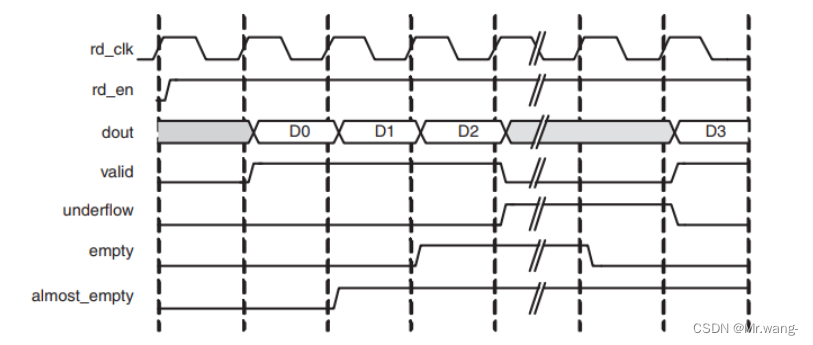

读时序:

6736

6736

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?