- 设计调试需求:当设计从仿真转向硬件实现时,用户对系统状态的控制和理解能力大幅下降,因此硬件内置良好的调试支持至关重要。虽然在有健壮操作系统(OS)运行时,软件可处理许多调试任务,但在很多场景中,硬件支持仍是必不可少的。

- 平台:由一个或多个组件组成的单个集成电路,这些组件可能是 RISC-V 核心或其他功能模块,通常都连接到单个系统总线。单个 RISC-V 核心包含一个或多个硬件线程(harts)。

- DXLEN:一个 hart 支持的最宽 XLEN

Feature

介绍一种调试接口所支持的功能特性,下面用大白话给你解释:

- 寄存器读写:所有硬件线程(hart)的寄存器(包括控制状态寄存器 CSRs),都能随便读和写。

- 内存访问方式:访问内存有两种选择,要么从硬件线程的 “视角” 去访问,要么直接通过系统总线去访问,也可以两种方式一起用。

- 支持多种 RISC - V 类型:不管是 32 位(RV32)、64 位(RV64),还是未来可能出的 128 位(RV128)的 RISC - V,这个调试接口都能支持。

- 独立调试每个硬件线程:平台里的任何一个硬件线程(hart),都可以单独进行调试,互相不干扰。

- 调试器自动发现信息:调试器自己就能找到几乎所有它需要知道的东西,不需要用户去手动配置。

- 从第一条指令开始调试:每个硬件线程(hart)从执行第一条指令的时候,就可以开始调试了,一开始就能 “盯着” 它。

- 软件断点暂停:当执行到软件断点指令时,硬件线程(hart)能停下来。

- 硬件单步执行:可以一次只执行一条指令,慢慢走,方便观察每一步的情况。

- 调试功能与传输方式无关:不管用什么方式来传输调试相关的数据,调试功能都能正常用。

- 调试器无需了解内部结构:调试器不需要知道它正在调试的硬件线程(hart)内部的复杂构造

下面带 (Optional) 是可选特性,不是必须有的:

11. 任意硬件线程同时停 / 恢复:可以让任意几个硬件线程(hart)同时停下来或者恢复运行。

12. 停了的硬件线程执行任意指令:硬件线程(hart)停下来后,可以让它执行任意指令。只要有办法把相关状态移到通用寄存器(GPRs),就算核心有额外或自定义指令 / 状态,也不需要新的调试功能。

13. 不暂停访问寄存器:不用让硬件线程(hart)停下来,就能访问它的寄存器。

14. 运行时执行短指令序列:正在运行的硬件线程(hart),可以被指挥去执行一小段指令,而且这么做不会太 “麻烦”(开销小)。

15. 系统总线主设备访问内存:有个系统总线主设备,能直接访问内存,不用经过任何硬件线程(hart)。

16. 触发条件暂停:当触发条件(比如程序计数器 PC、读写地址 / 数据、指令操作码)满足时,硬件线程(hart)能停下来。

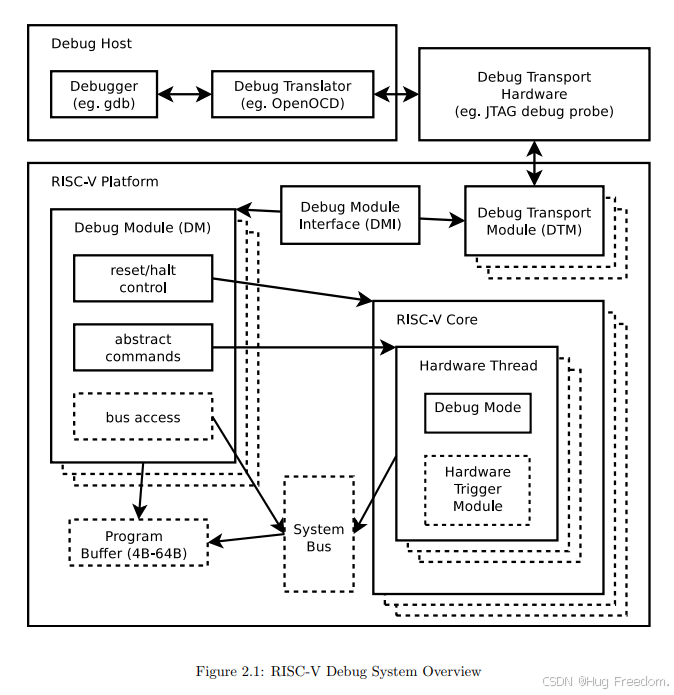

system overview

外部调试支持的组成图,虚线部分可有可无。用户用运行调试器(如 gdb)的笔记本(调试主机)。调试器通过调试翻译器(如 OpenOCD,带硬件驱动)和调试传输硬件(如特定适配器)连接到平台的调试传输模块(DTM)。DTM 用 DMI 接口连调试模块(DM)。每个 hart 由一个 DM 管,hart 可以不一样,通常一个核心的 hart 被同一个 DM 控制,多数平台一个 DM 管所有 hart。DM 控制 hart 运行,用抽象命令访问通用寄存器,其他寄存器可通过命令或给程序缓冲区写程序访问。程序缓冲区能让调试器在 hart 执行任意指令,也能访问内存。还有个可选的系统总线访问块,不通过 hart 就能访问内存。每个 hart 还可能有触发模块,满足条件就停下并告诉调试模块。

-

整体连接关系:

你就像一个 “指挥官”,通过一台笔记本电脑(调试主机,比如它运行着调试器软件 gdb)来发起调试操作。调试器会和一个 “翻译官”(调试翻译器,例如 OpenOCD,它可能还包含硬件驱动)沟通,这个 “翻译官” 再和一个 “硬件桥梁”(调试传输硬件,比如 Olimex USB - JTAG 适配器这种硬件)交流。最后,这个 “硬件桥梁” 把笔记本电脑和平台里的 “调试传输模块”(DTM)连起来。DTM 呢,又能通过 “调试模块接口”(DMI)去访问一个或多个 “调试模块”(DM)。 -

调试模块(DM)与硬件线程(hart)的关系:

平台里的每个 “硬件线程”(hart,可理解为芯片里的一个 “工作单元”)都由且只由一个 DM 控制。这些 hart 可以是 “不一样的”(异构)。虽然对 hart 和 DM 怎么配对没太多死规定,但一般来说,同一个核心里的 hart 会被同一个 DM 控制。大多数平台里,往往就一个 DM 来控制平台里所有的 hart。 -

DM 的功能:

DM 能对它控制的 hart 进行 “运行控制”(比如让 hart 开始、停止运行)。通过 “抽象命令” 可以访问通用寄存器(GPRs,好比是 hart 的 “小笔记本”,用来临时记数据)。其他额外的寄存器呢,要么也通过 “抽象命令” 访问,要么给一个 “程序缓冲区”(可选的,相当于一个临时的 “指令小仓库”)写程序来访问。 -

程序缓冲区与系统总线访问:

“程序缓冲区” 很有用,它允许调试器让 hart 执行任意指令,就像给 hart 下任意的小任务。这个机制还能用来访问内存。另外,有个 “可选的系统总线访问块”(相当于一个特殊通道),它允许不通过 RISC - V 的 hart 去访问内存,绕开 hart 直接操作内存。 -

触发模块:

每个 RISC - V 的 hart 还可以有一个 “触发模块”。打个比方,它就像一个 “门卫”,当满足特定条件(比如特定的指令、地址操作等)时,hart 就会停下来,并且告诉调试模块 “我停下啦”。

这样一整套机制,就构成了从外部电脑通过各种桥梁和模块,对芯片里的 hart 进行调试的能力。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?