基于MATLAB的HDL代码生成及FPGA综合

本示例展示了如何创建HDL Coder项目,为您的MATLAB设计生成代码,并合成HDL代码,以滤波器为例。在这个例子中,你将学会:

1、创建一个MATLAB HDL编码器项目。

2、将设计和测试台文件添加到项目中。

3、启动HDL Workflow Advisor进行MATLAB设计。

4、执行定点转换和生成HDL代码。

5、从MATLAB测试台生成HDL测试台(Test Bench)。

6、使用HDL模拟器验证生成的HDL代码。本例使用ModelSim作为工具。

7、使用合成工具对生成的HDL代码进行合成。本例使用Xilinx Vivado作为工具。

一、MATLAB滤波器设计、测试以及HDL Coder工程创建

关于本节内容在上一篇文章中已经做了详细介绍,请参考:基于Matlab设计生成HDL/Verilog代码,此处不做过多赘述,本章内容继续延用上一篇文章的工程。

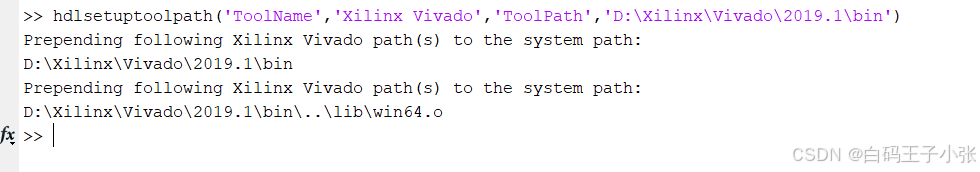

设置HDL模拟器和综合工具路径:

如果要合成生成的HDL代码,在使用HDL Coder生成代码之前,请设置合成工具路径。要设置合成工具的路径,请使用hdlsetuptoolpath函数。例如,如果您的合成工具是Xilinx Vivado:

您必须已经安装了Xilinx Vivado。要检查Xilinx Vivado合成工具设置,运行以下命令启动该工具:

如果要使用HDL测试台模拟生成的HDL代码,可以使用HDL模拟器,如ModelSim。您必须已经安装了HDL模拟器。

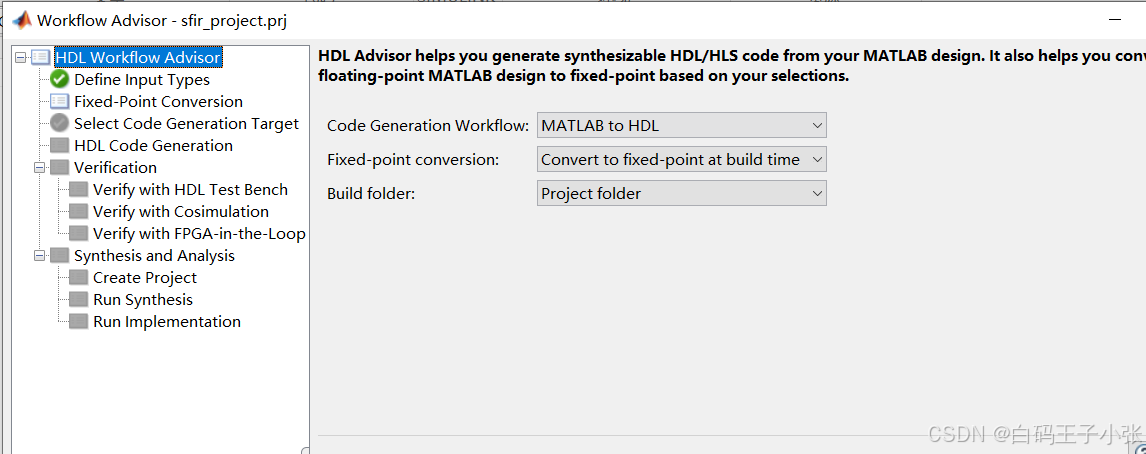

二、创建算法和测试台的定点版本

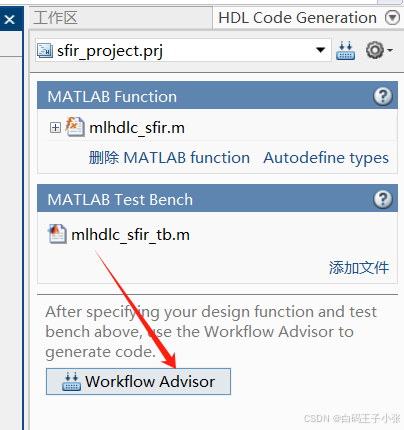

1、单击Workflow Advisor按钮打开Workflow Advisor。您可以看到,Define Input T types任务已经通过。

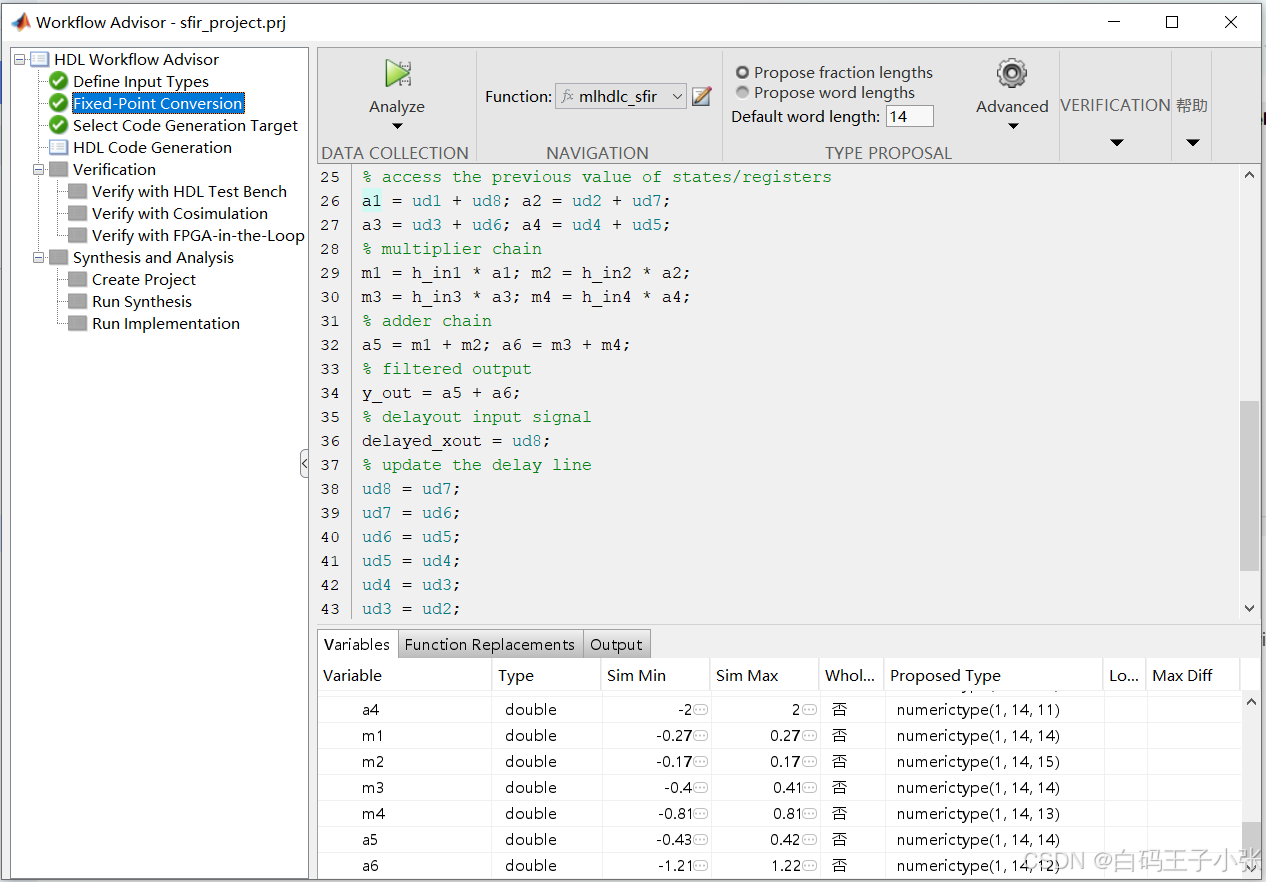

2、执行定点转换任务。在右窗格中打开定点转换工具。

当运行定点转换时,为浮点数据类型建议分数长度,HDL Coder使用Default word length。在本教程中,Default word length是14。advisor提供了一个默认的安全边际模拟最小/最大(Safety Margin for Simulation Min/Max)为0%。advisor根据这个安全系数调整数据的范围。例如,值4指定您想要一个至少大4%的范围。参见“Floating-Point to Fixed-Point Conversion”。

三、选择“Code Generation Option”和“Generate HDL Code”

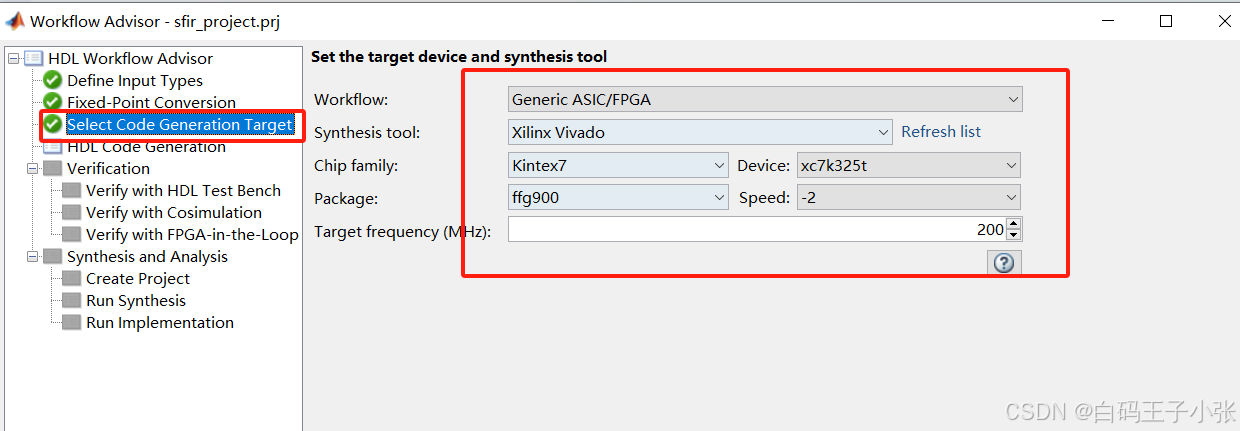

在生成HDL代码之前,如果希望将代码部署到目标平台上,请指定合成工具。在Code Generation Target任务中,将Workflow保留为Generic ASIC/FPGA,并指定Xilinx Vivado作为合成工具。如果没有看到合成工具,请单击“刷新列表”。运行此任务。

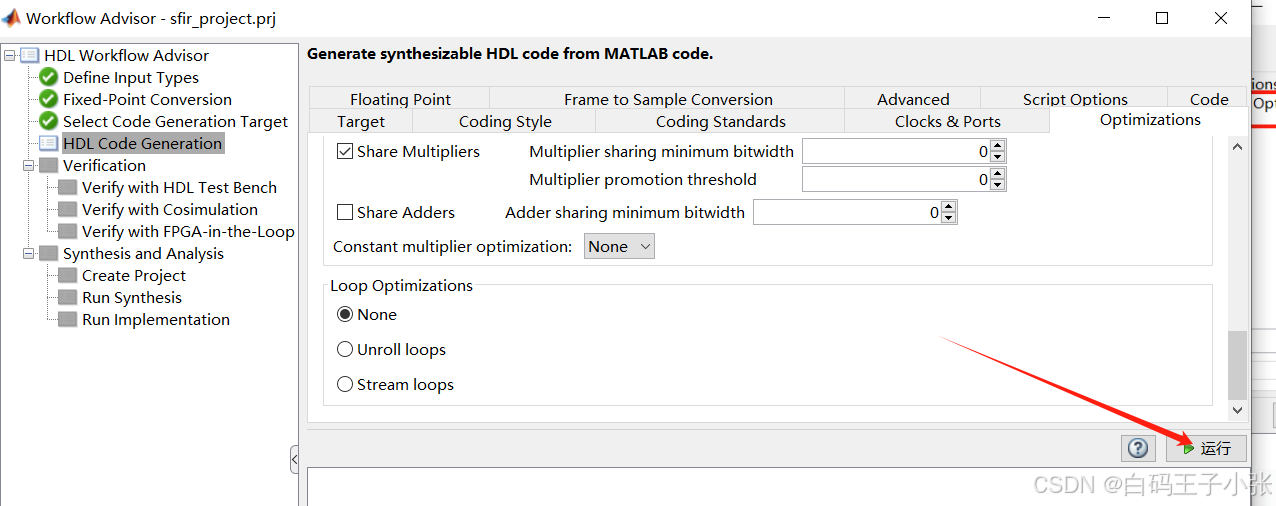

在HDL Code Generation任务中,通过使用该任务右侧的选项卡,您可以指定其他代码生成选项。

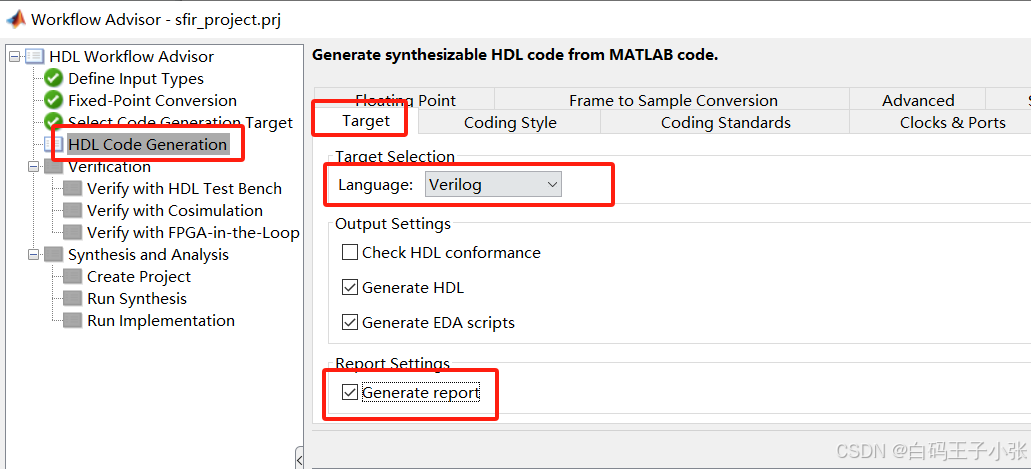

1、默认情况下,HDL Coder生成VHDL代码。要生成Verilog或SystemVerilog代码,请在Target选项卡中选择Verilog或SystemVerilog作为语言。

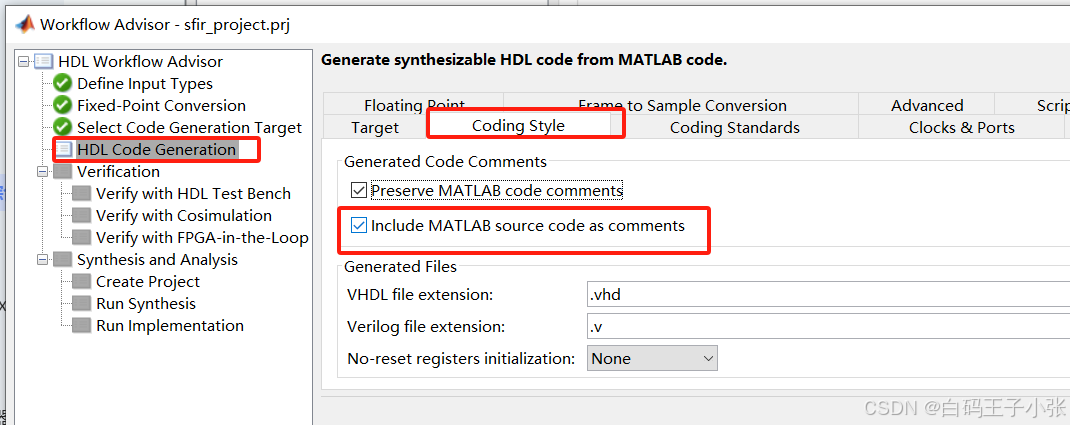

2、要生成带有注释和可追溯性链接的代码生成报告,在Coding style选项卡中,选择Include MATLAB源代码作为注释和Generate Report。

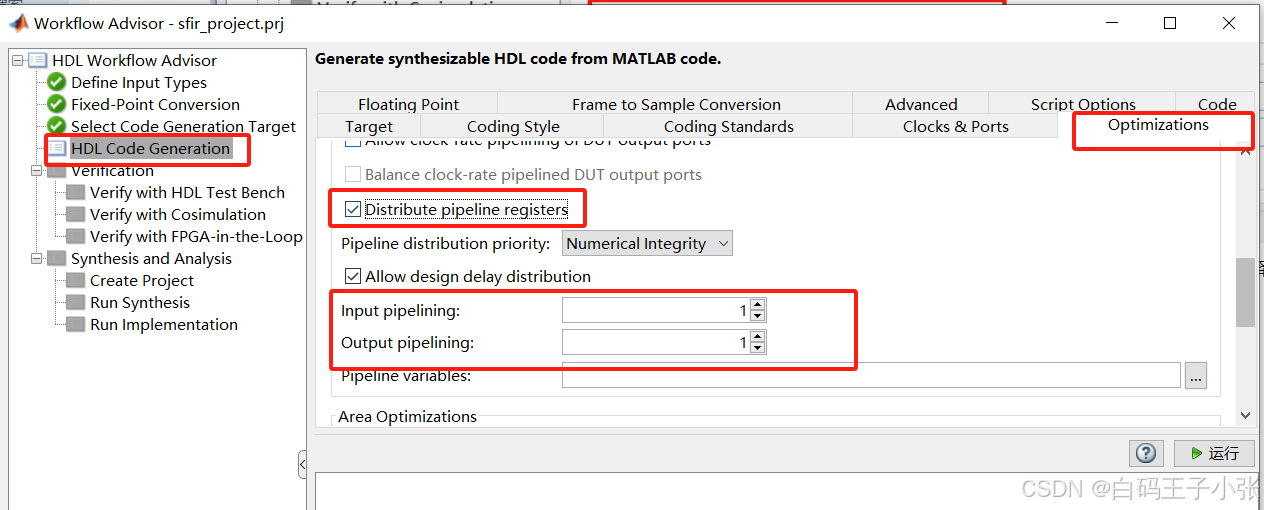

3、为了优化您的设计,您可以使用分布式流水线优化。在Optimizations选项卡中,为Input pipelining和Output pipelining指定1,然后选择Distribute pipeline寄存器。

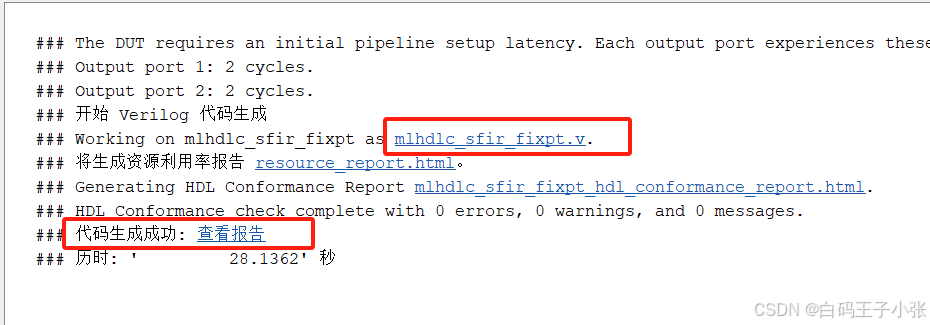

4、单击“Run”,生成Verilog或SystemVerilog代码。

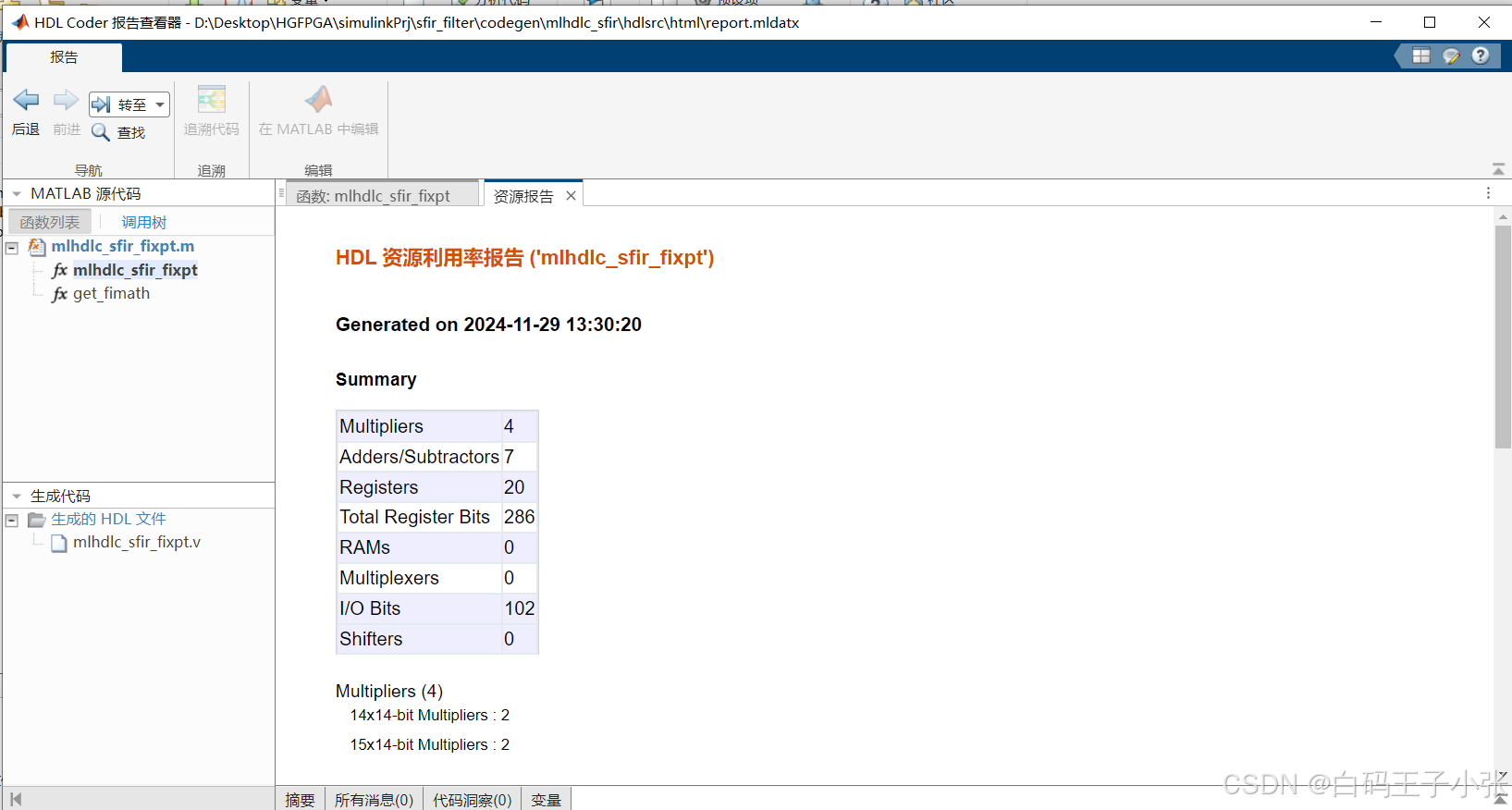

检查日志窗口并单击链接以查看生成的代码和报告。

四、生成HDL 测试台并仿真生成的代码

HDL Coder生成HDL测试台,利用HDL模拟器运行HDL测试台,并验证HDL仿真是否与定点MATLAB仿真的数值和时延相匹配。

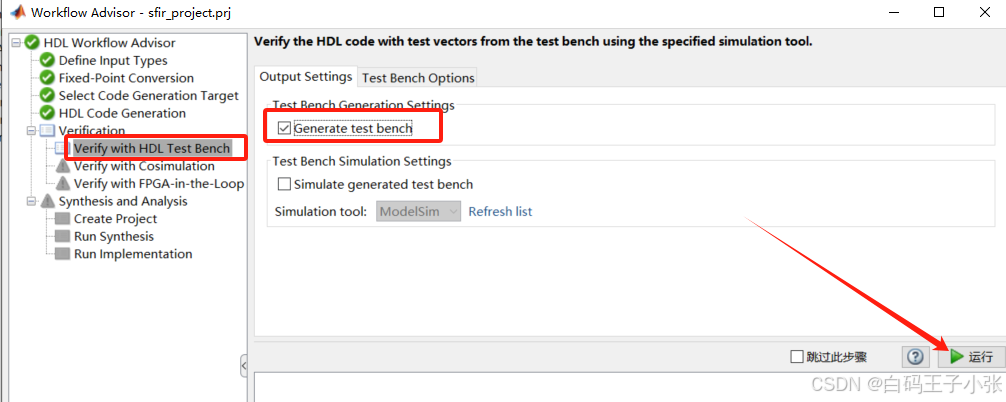

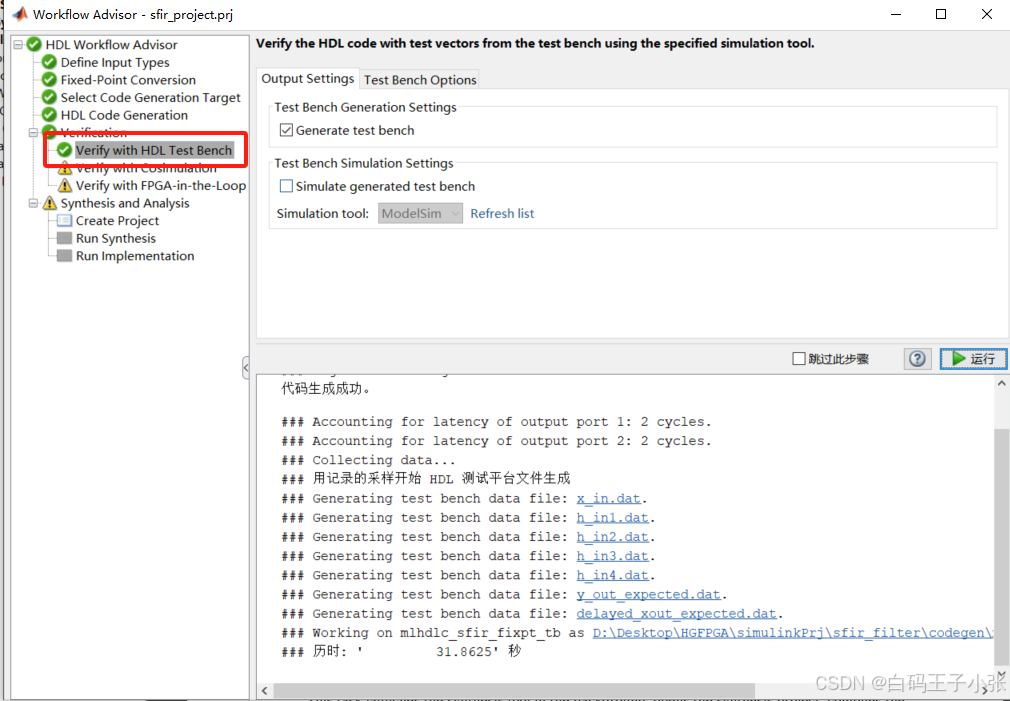

生成HDL测试台并模拟生成的代码,在HDL Verification > Verifywith HDL T est Bench任务中:

1、在Output Settings选项卡中,选择Generate HDL test bench。

2、要模拟生成的测试台,请将仿真工具设置为ModelSim。您必须已经安装了ModelSim。

3、要指定在单独的文件中生成HDL测试台代码和测试台数据,请在Test Bench Options选项卡中选择Multi-file Test Bench。

4、点击“Run”按钮。

该任务生成一个HDL测试台,然后使用选定的仿真工具对定点设计进行仿真,并生成编译报告和仿真报告。

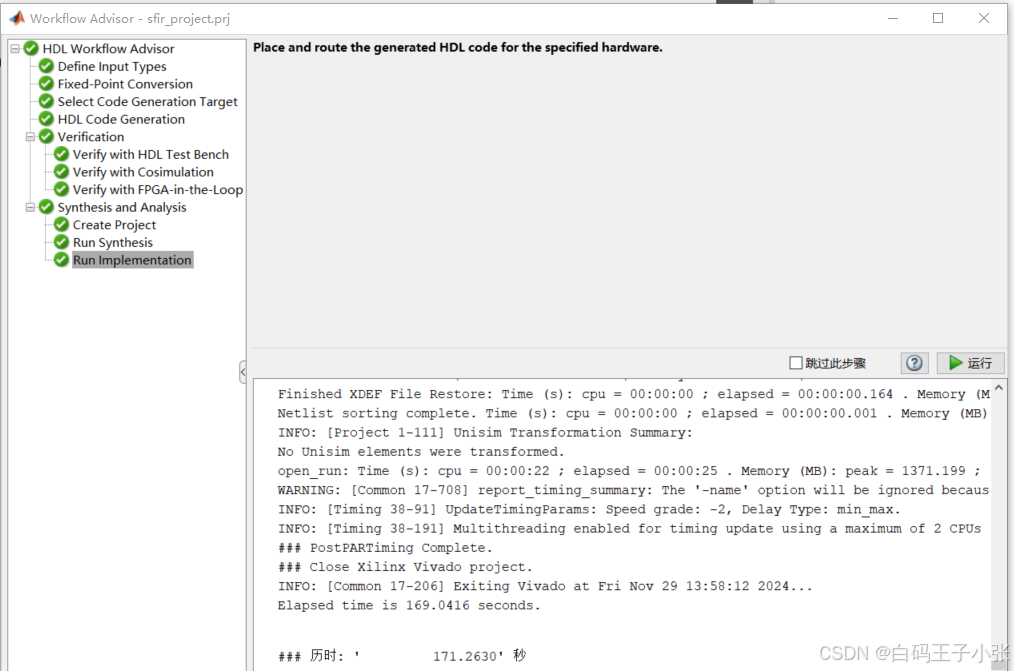

五、综合生成的HDL代码

HDL Coder在目标平台上综合HDL代码,并根据您指定的目标设备为您的设计生成面积和时间报告。

综合生成的HDL代码:

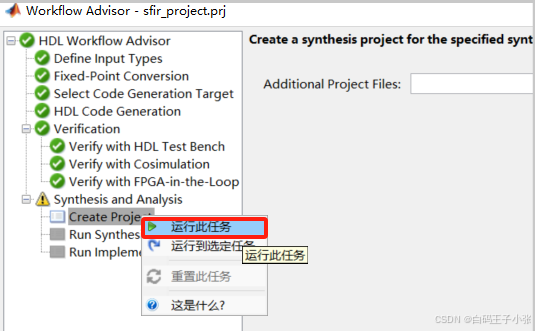

1、运行Create Project任务。

此任务为HDL代码创建一个Xilinx Vivado综合项目。HDL Coder在本任务的下一个任务中进行综合设计。

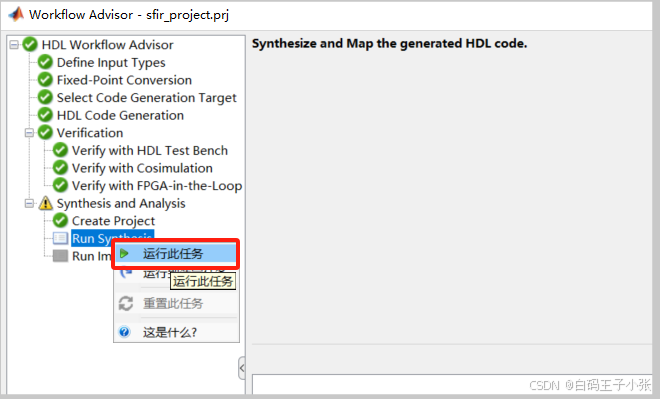

2、选择并运行Run Synthesis任务。

本任务在后台启动综合工具,打开综合项目,编译HDL代码,综合设计,生成网表和面积、时间报表。

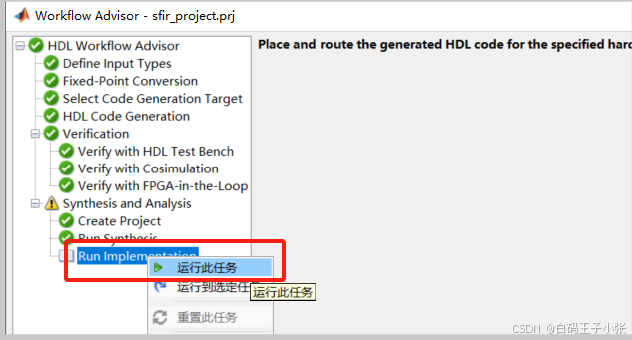

3、选择并运行Run Implementation任务。

此任务在后台启动综合工具,在设计上运行布局布线,并生成布线前后的时序信息,用于关键路径分析和源模型的反向注释。

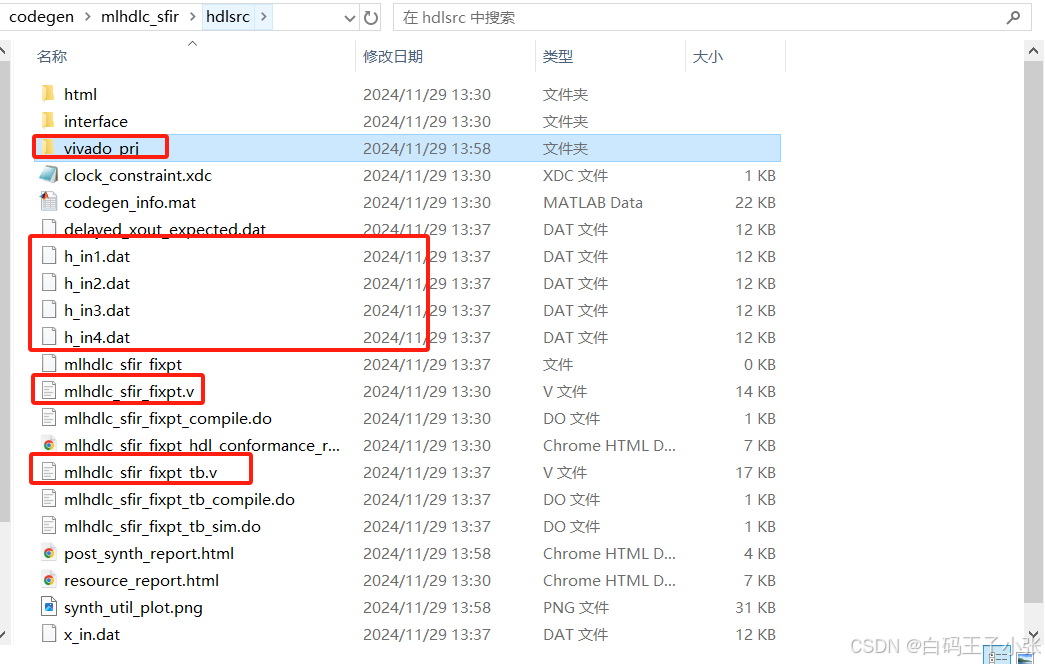

生成的Vivado工程及文件:

可以运行仿真文件查看仿真波形。

关于仿真请参考:Matlab Simulink HDL Coder开发流程(三)— 验证从Simulink模型生成的HDL代码

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?