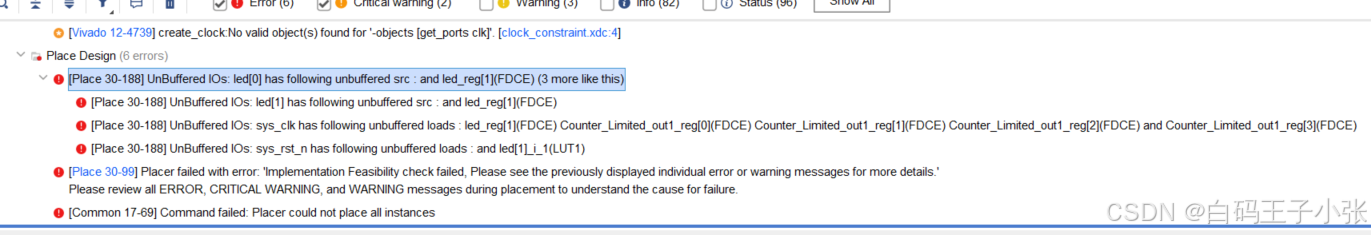

这里我将Simulink HDL Coder综合生成的Vivado工程的信号连接到LED引脚验证设计是否正常工作,Vivado布局布线时出现如下错误:

[Place 30-188] UnBuffered IOs: led[0] has following unbuffered src : and led_reg1

[Place 30-99] Placer failed with error: ‘Implementation Feasibility check failed, Please see the previously displayed individual error or warning messages for more details.’

Please review all ERROR, CRITICAL WARNING, and WARNING messages during placement to understand the cause for failure.

[Common 17-69] Command failed: Placer could not place all instances

[Place 30-188] UnBuffered IOs: led[1] has following unbuffered src : and led_reg1

[Place 30-188] UnBuffered IOs: sys_clk has following unbuffered loads : led_reg1 Counter_Limited_out1_reg0 Counter_Limited_out1_reg1 Counter_Limited_out1_reg2 and Counter_Limited_out1_reg3

[Place 30-188] UnBuffered IOs: sys_rst_n has following unbuffered loads : and led[1]_i_1(LUT1)

解决方法:

重新创建一个Vivado工程,将Simulink生成的Verilog文件添加进工程再分析综合上板。

2804

2804

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?