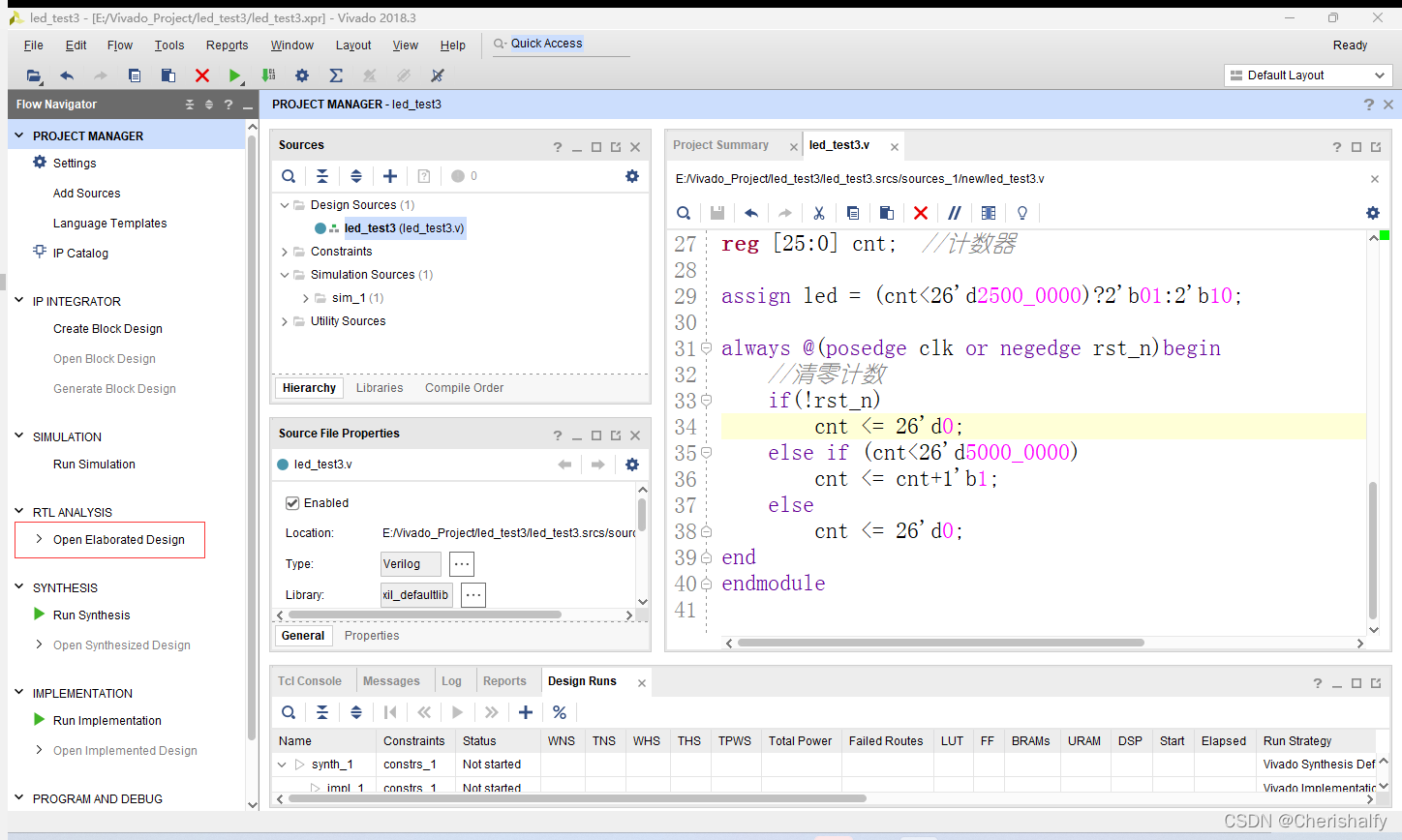

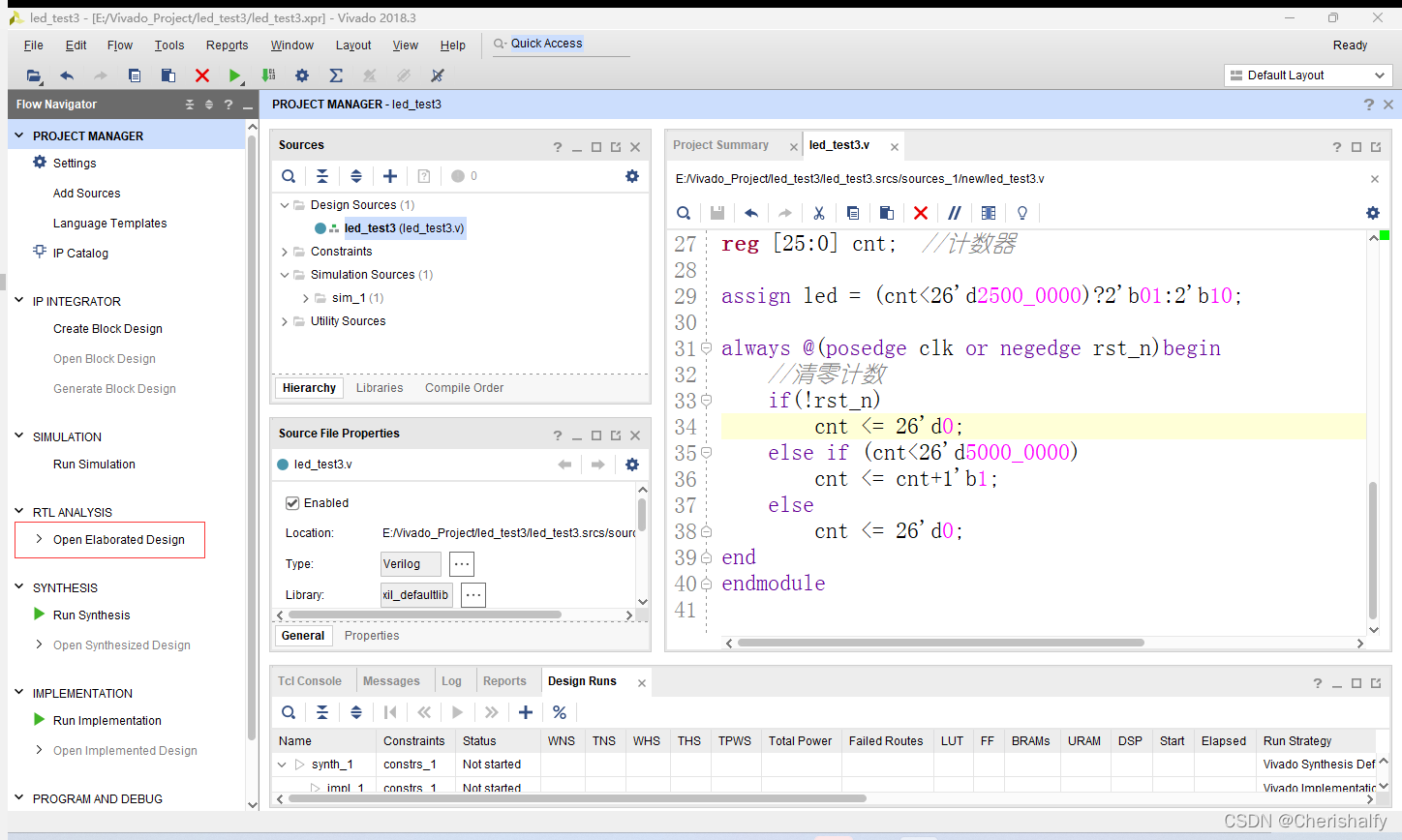

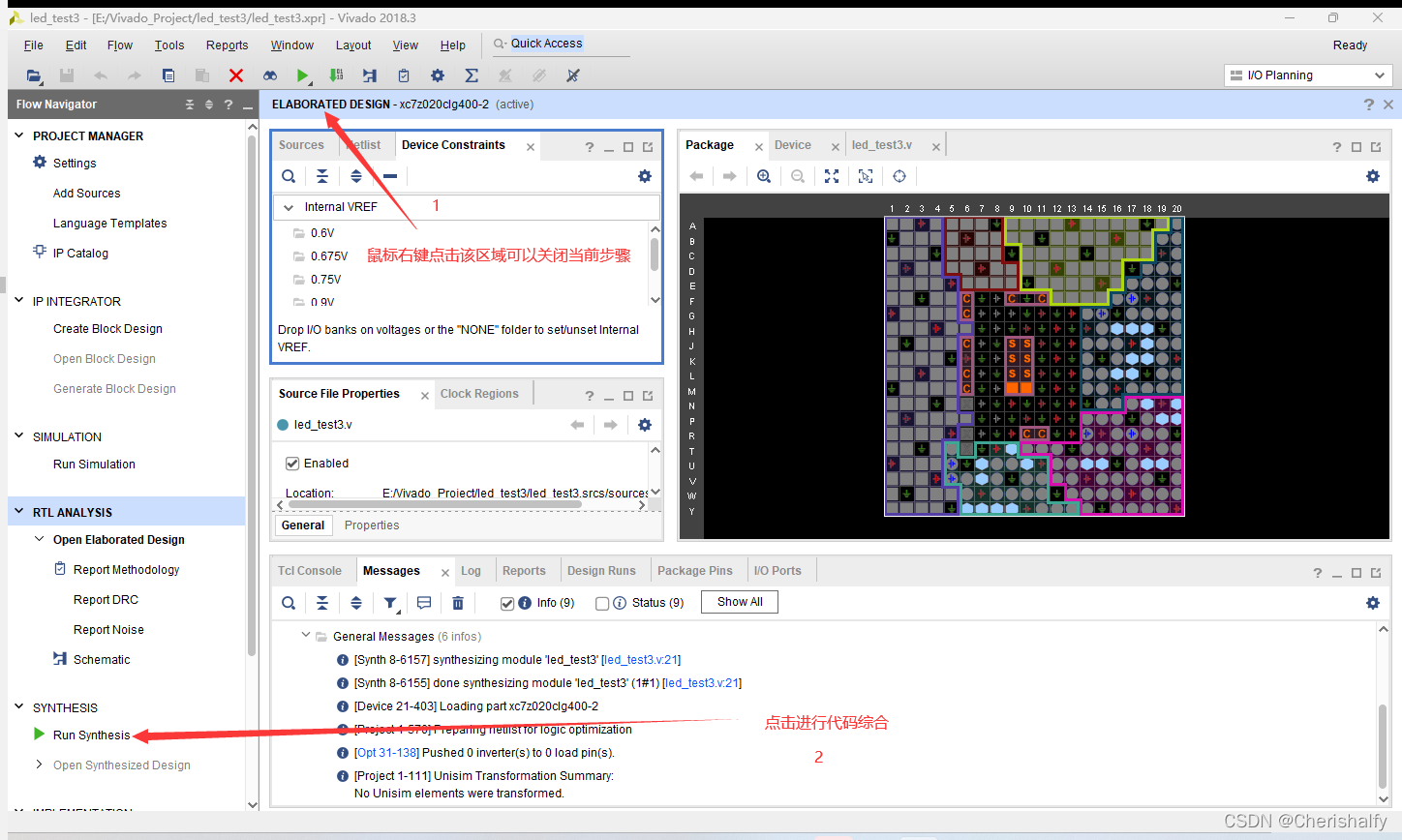

别写好Verilog代码之后点击RTL ANALYSIS目录下的Open Elaborated Design按钮生成模块的RTL图

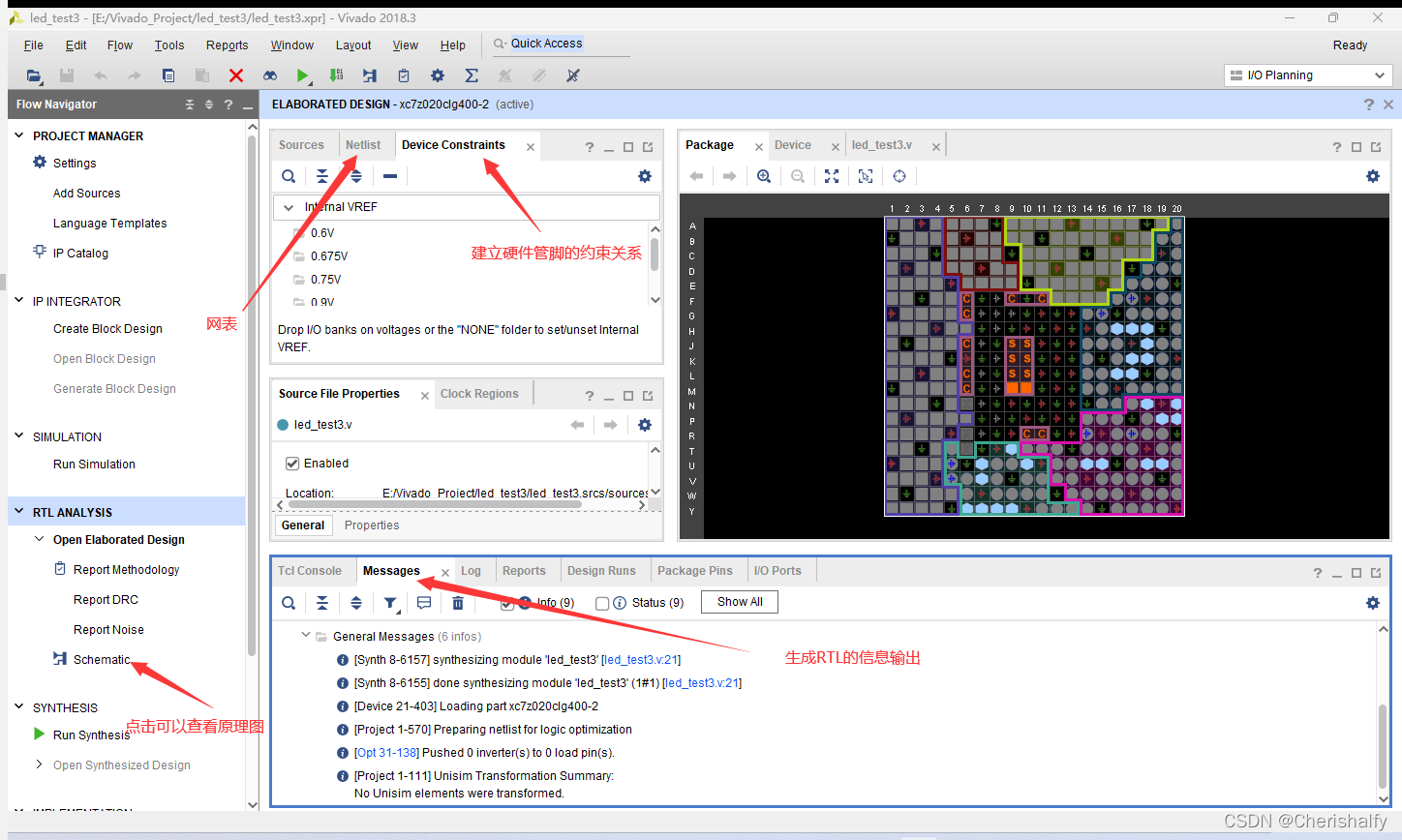

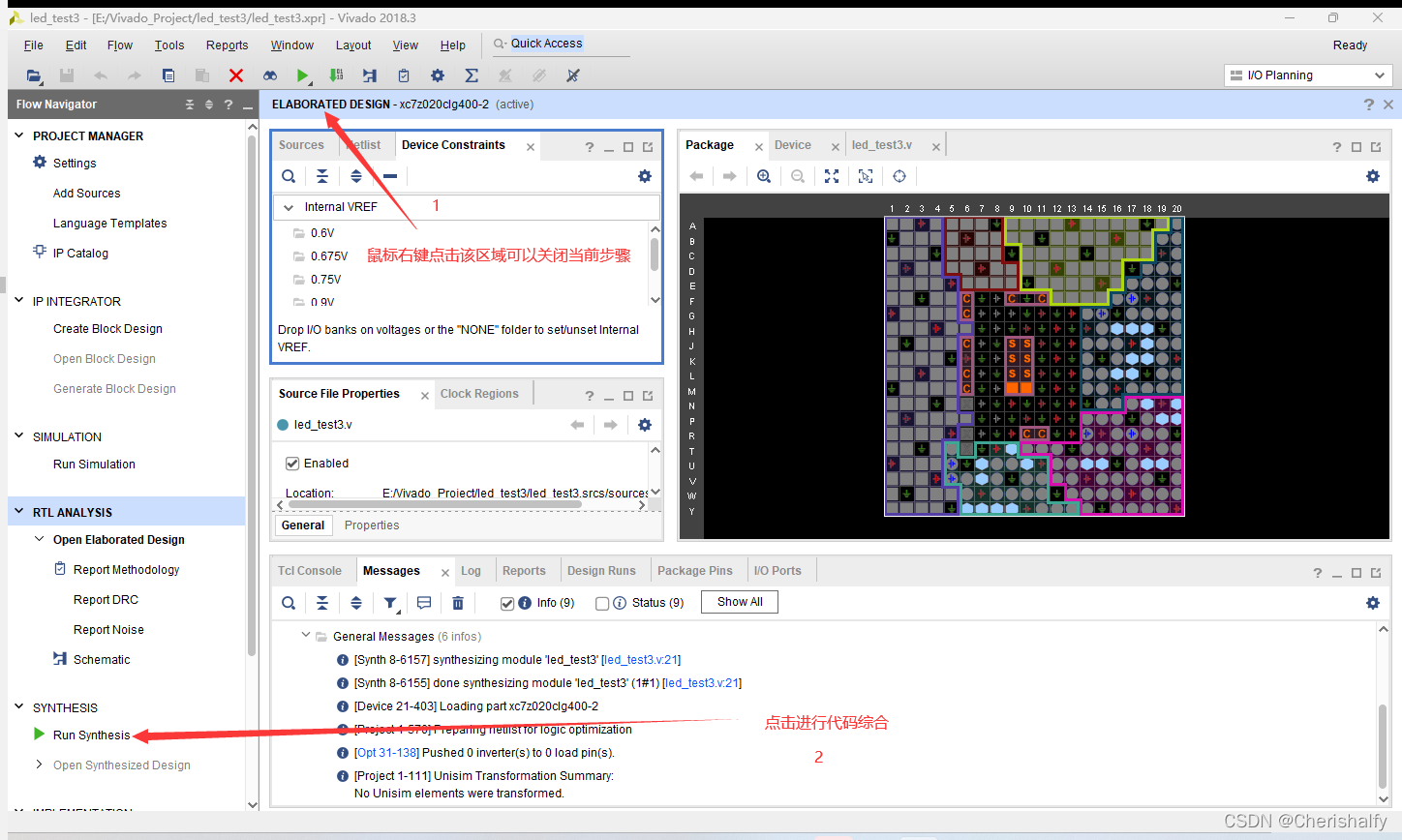

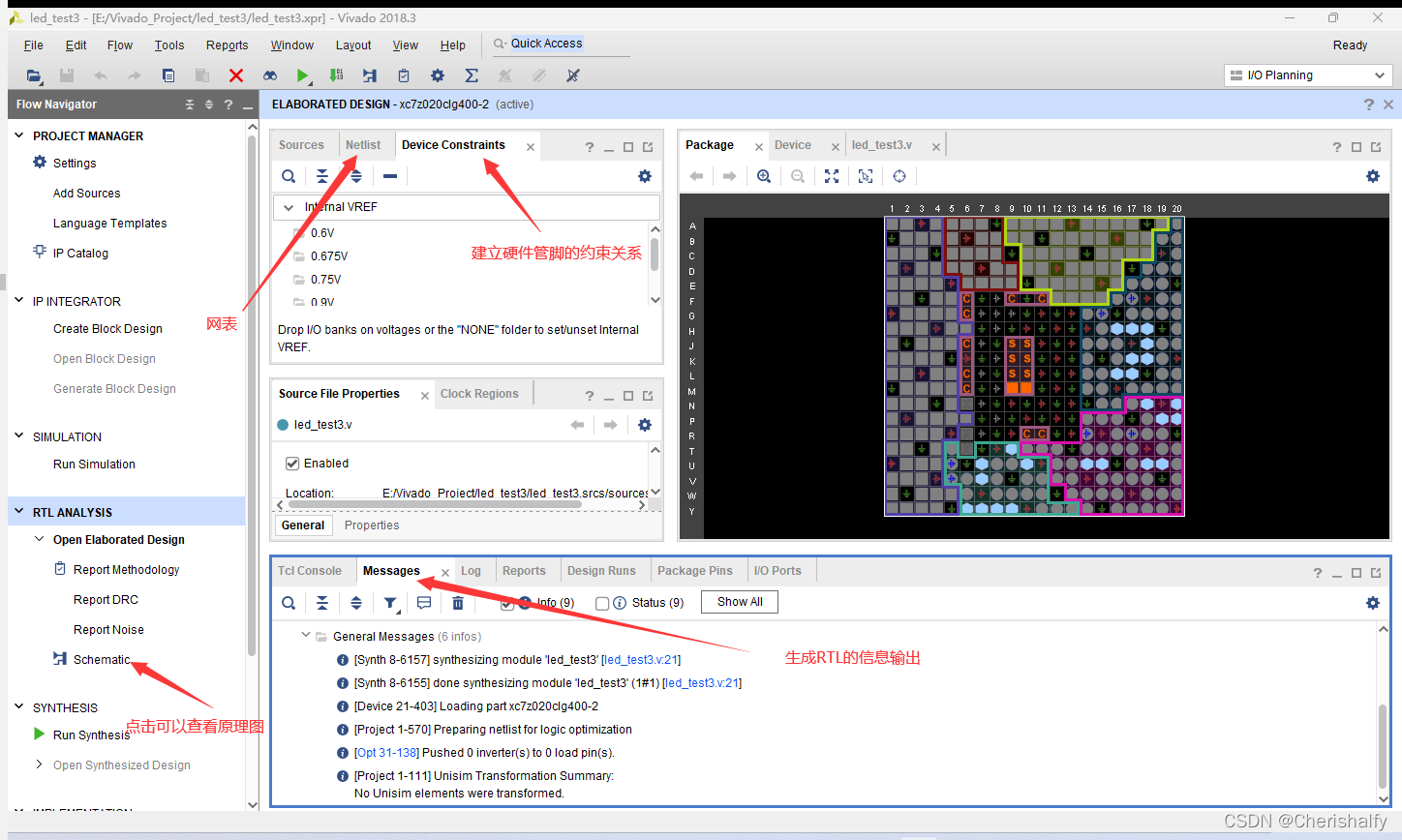

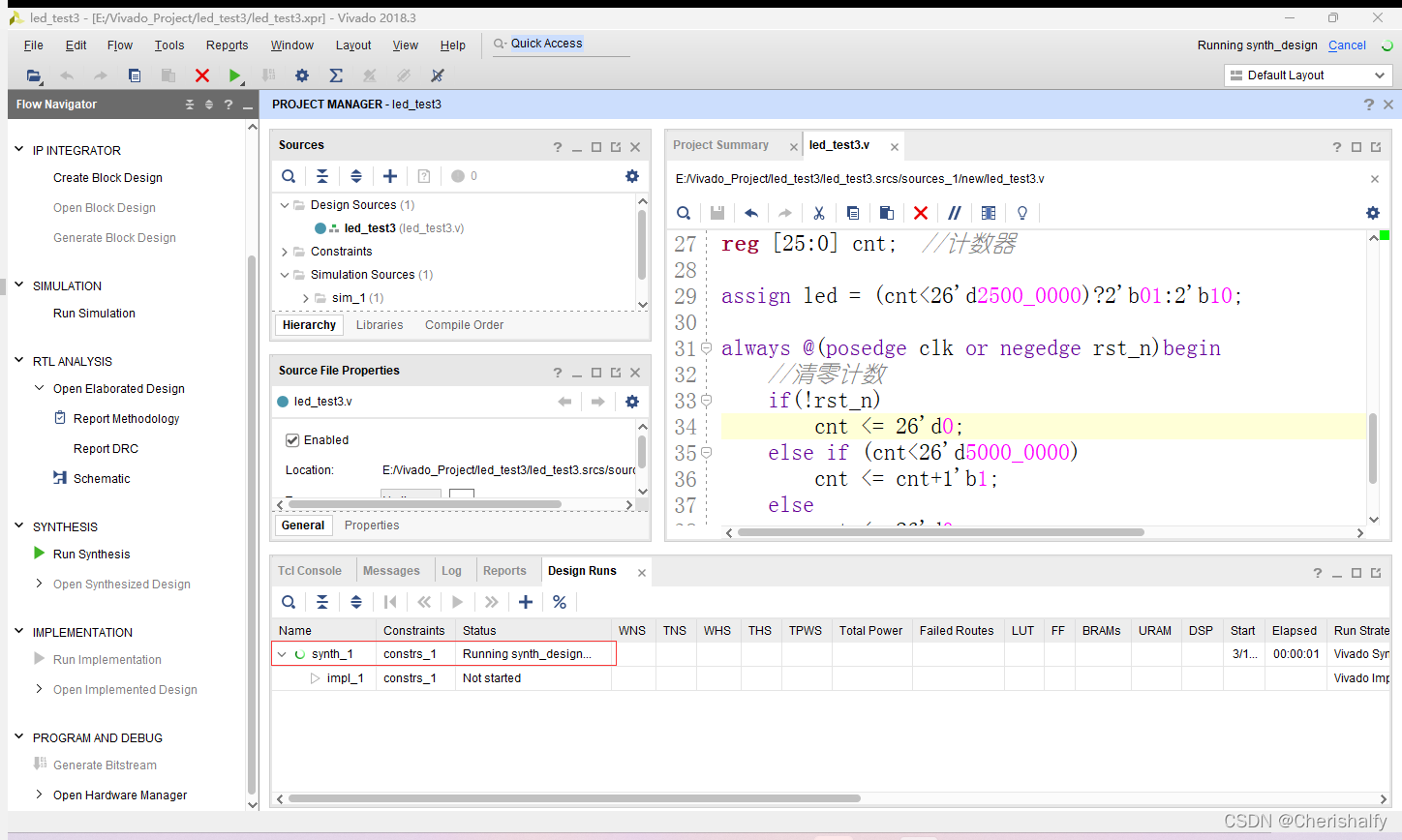

产生RTL之后软件界面变化如下

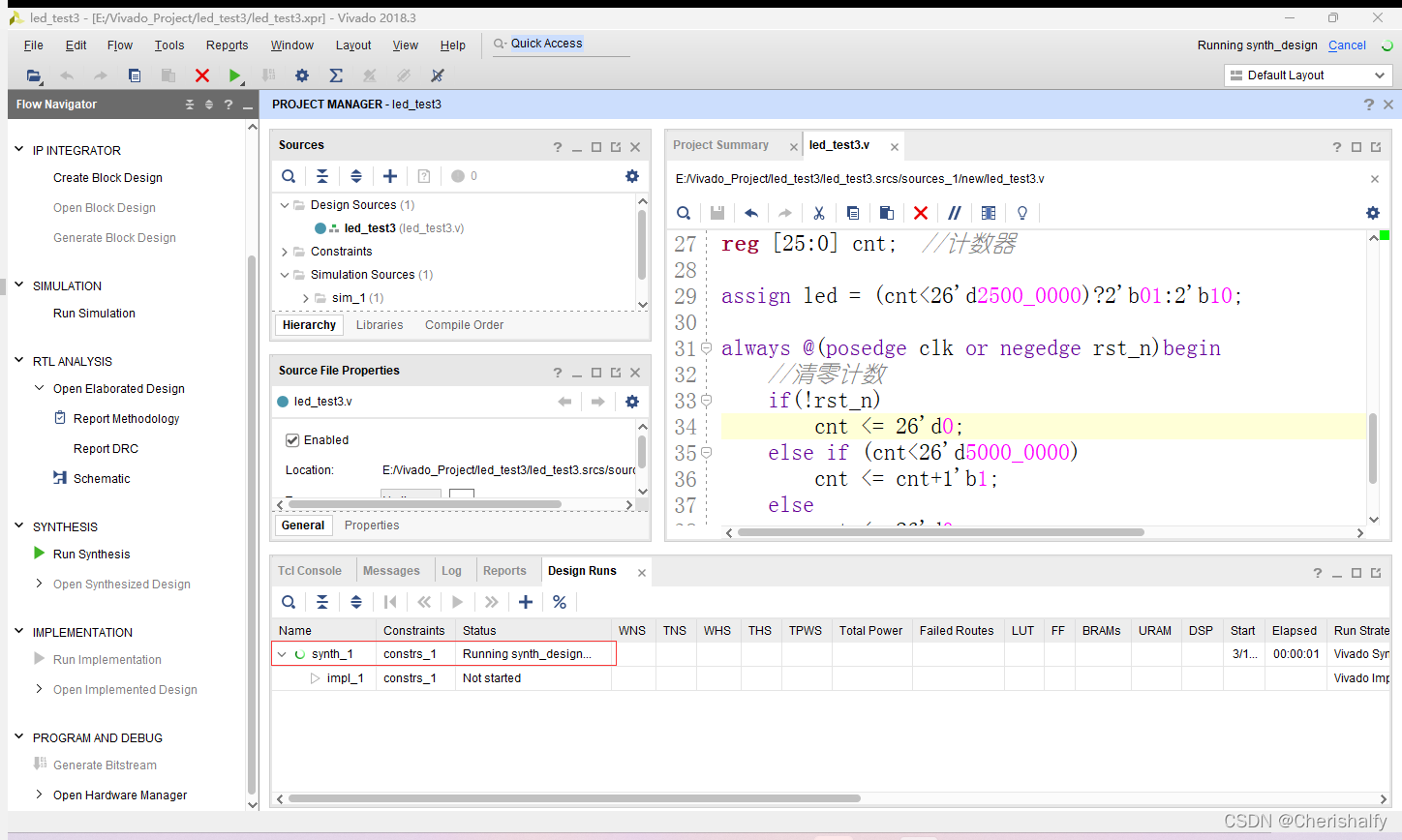

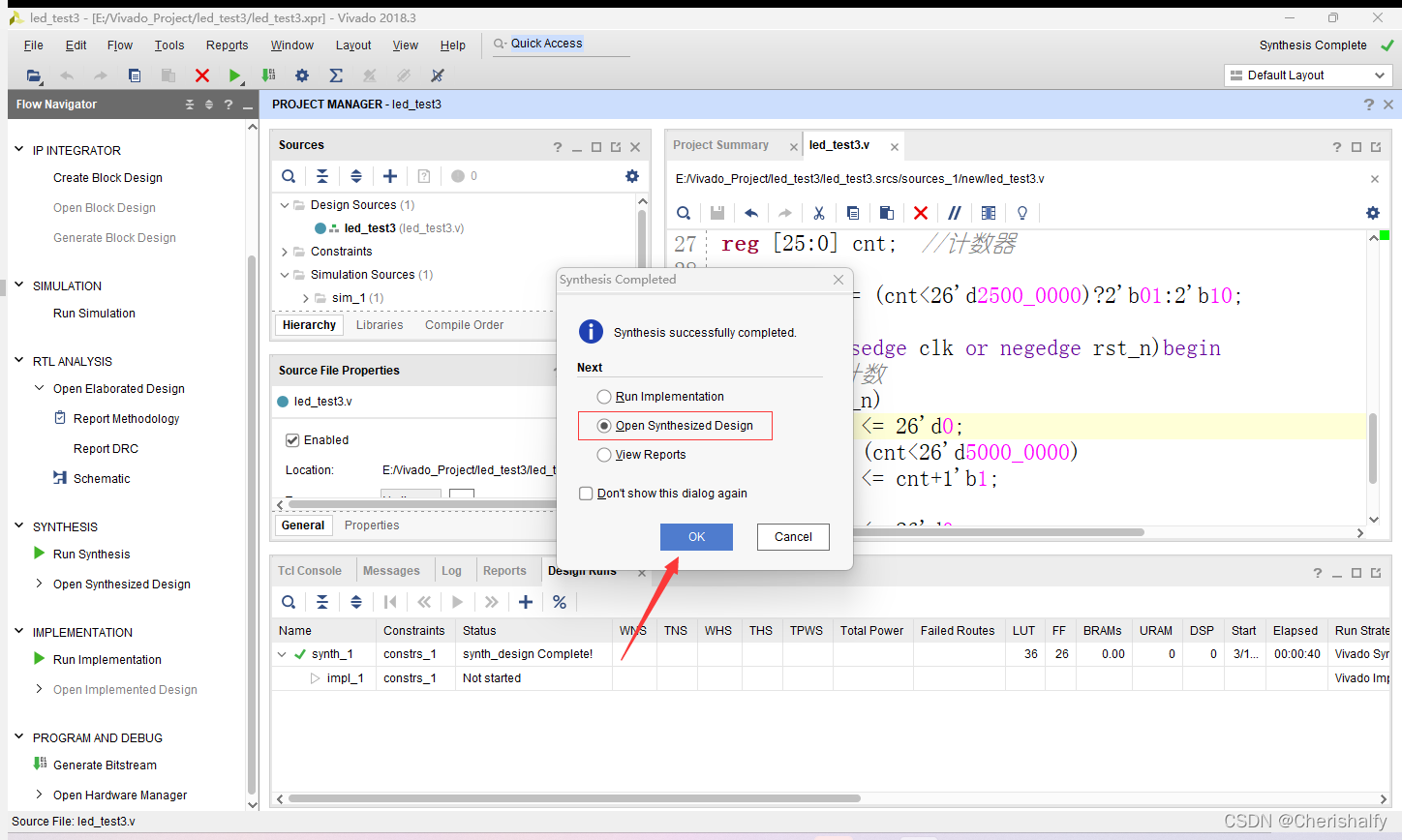

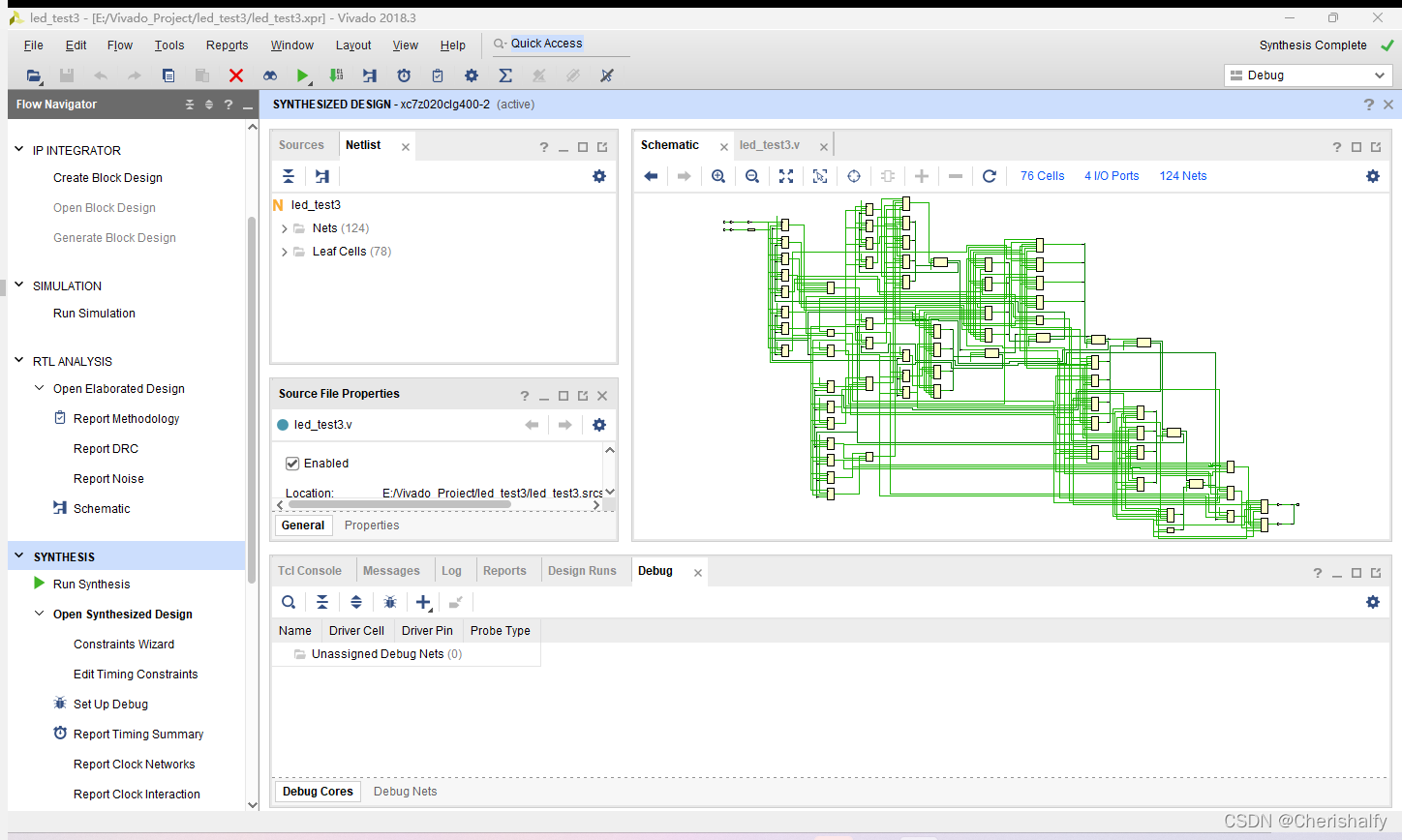

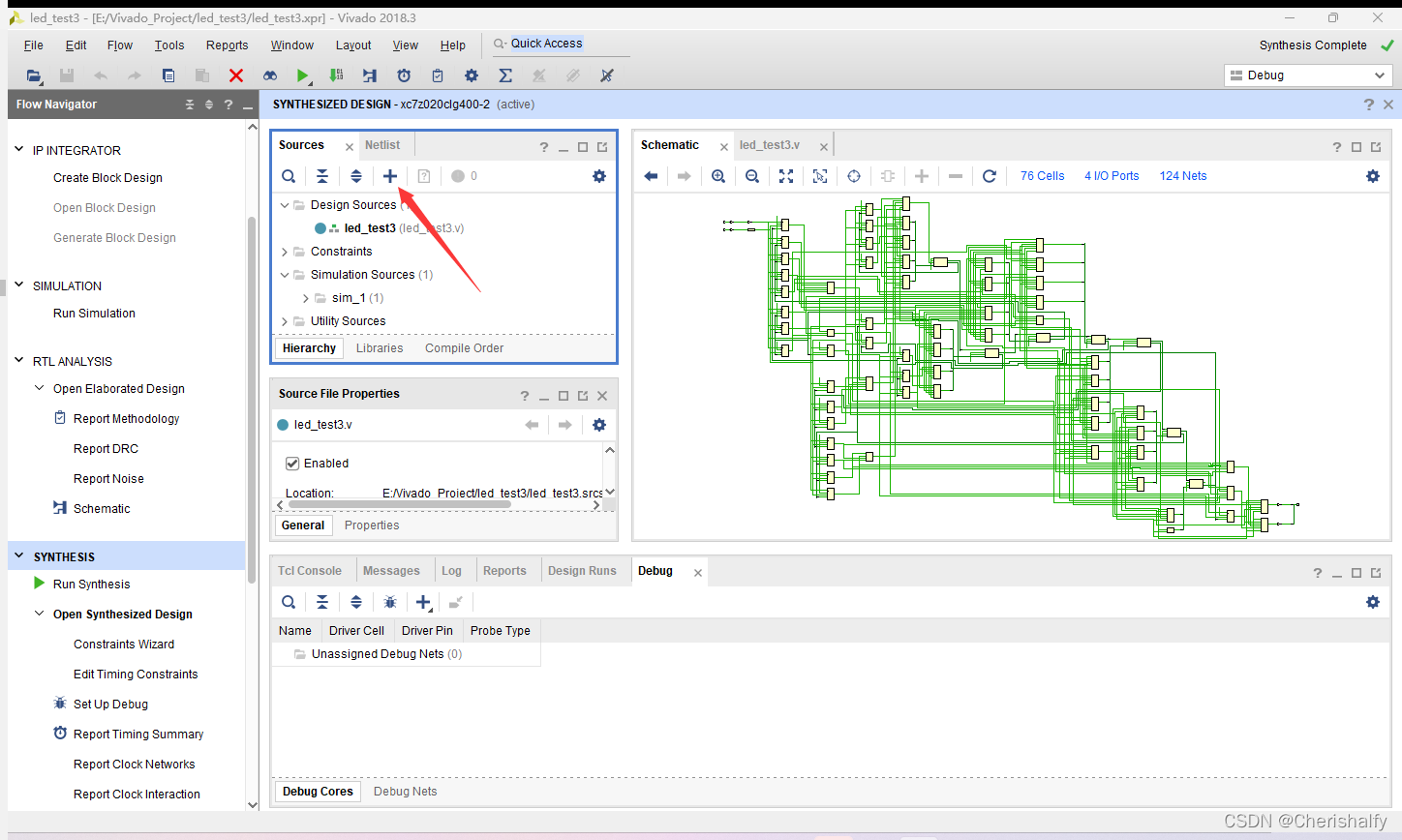

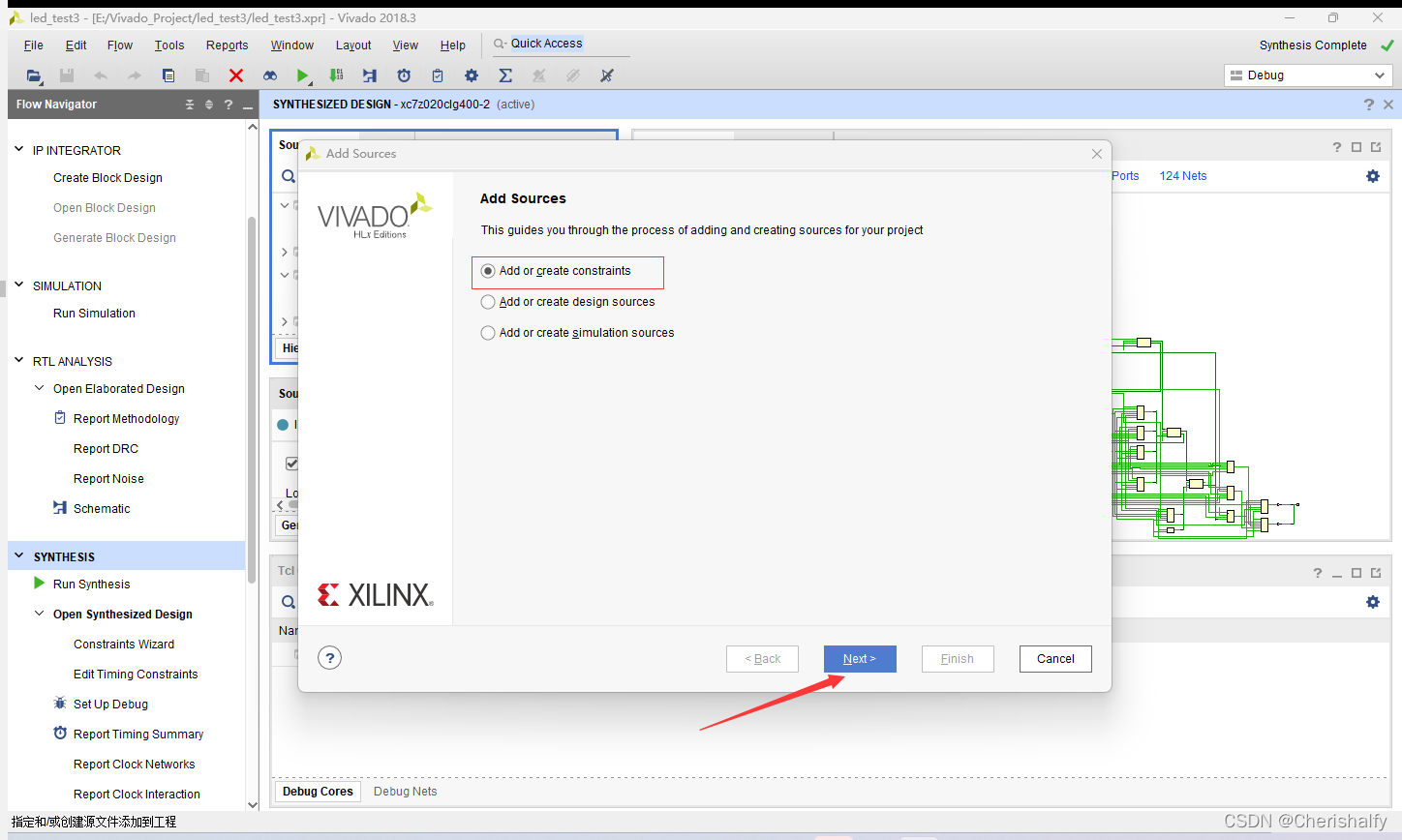

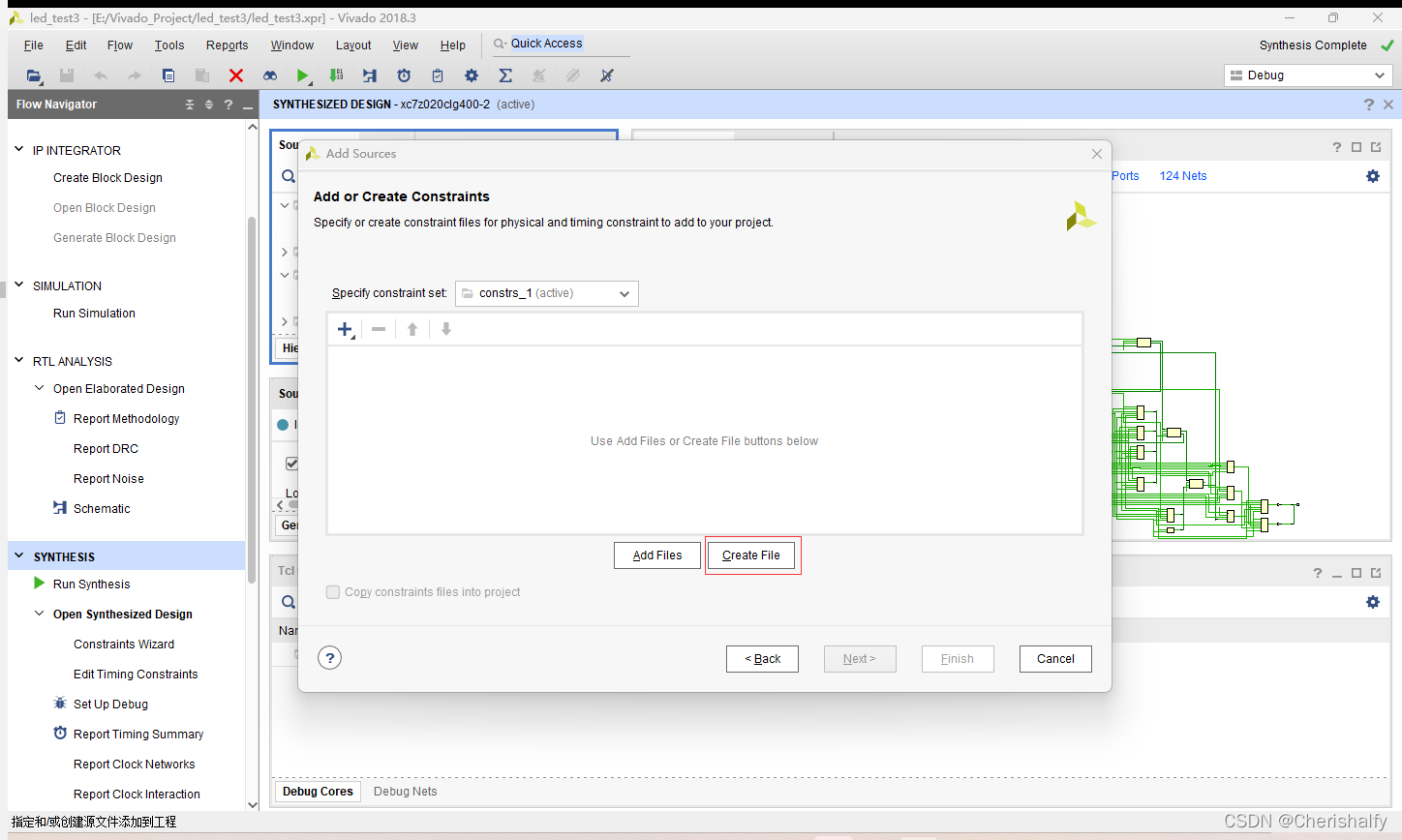

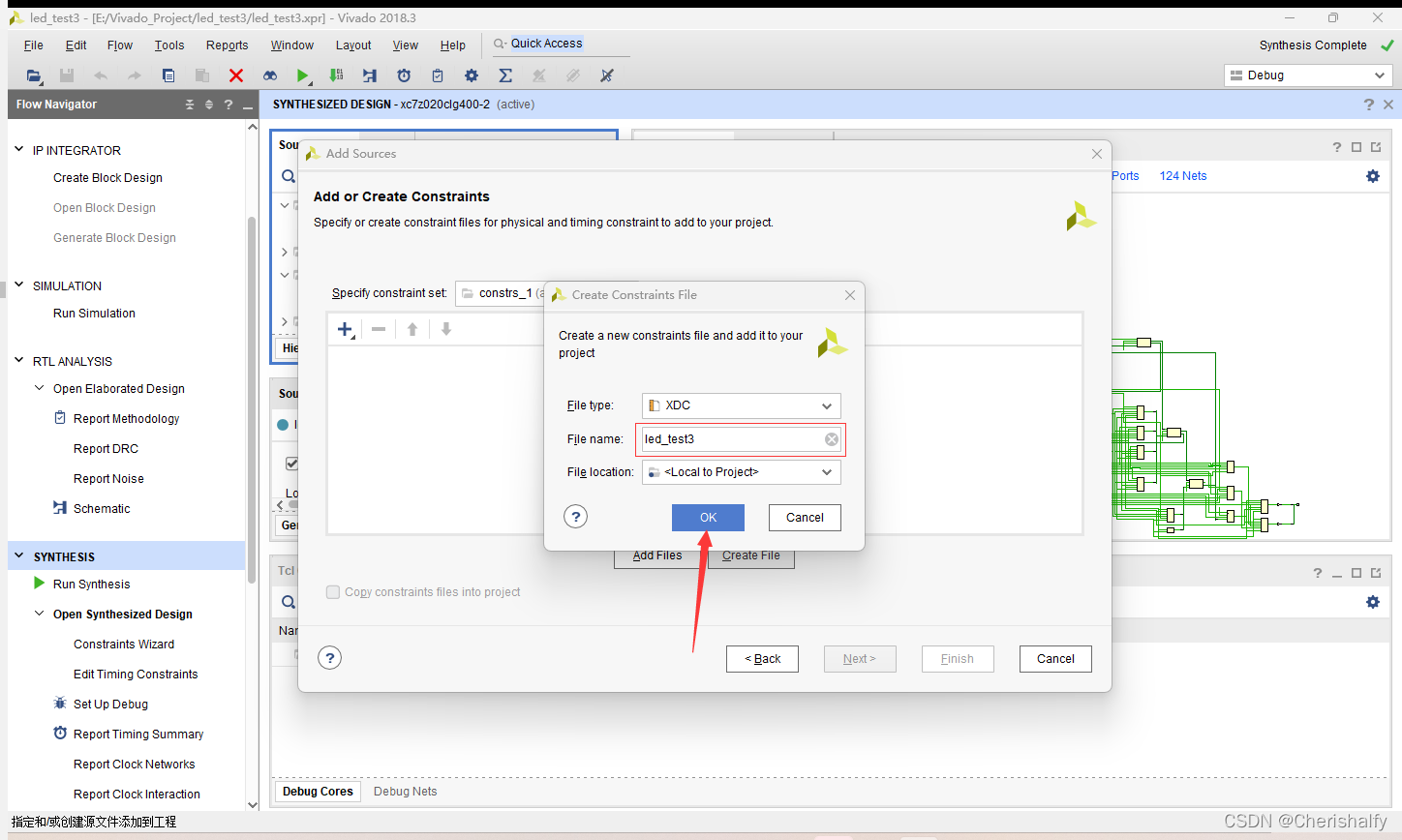

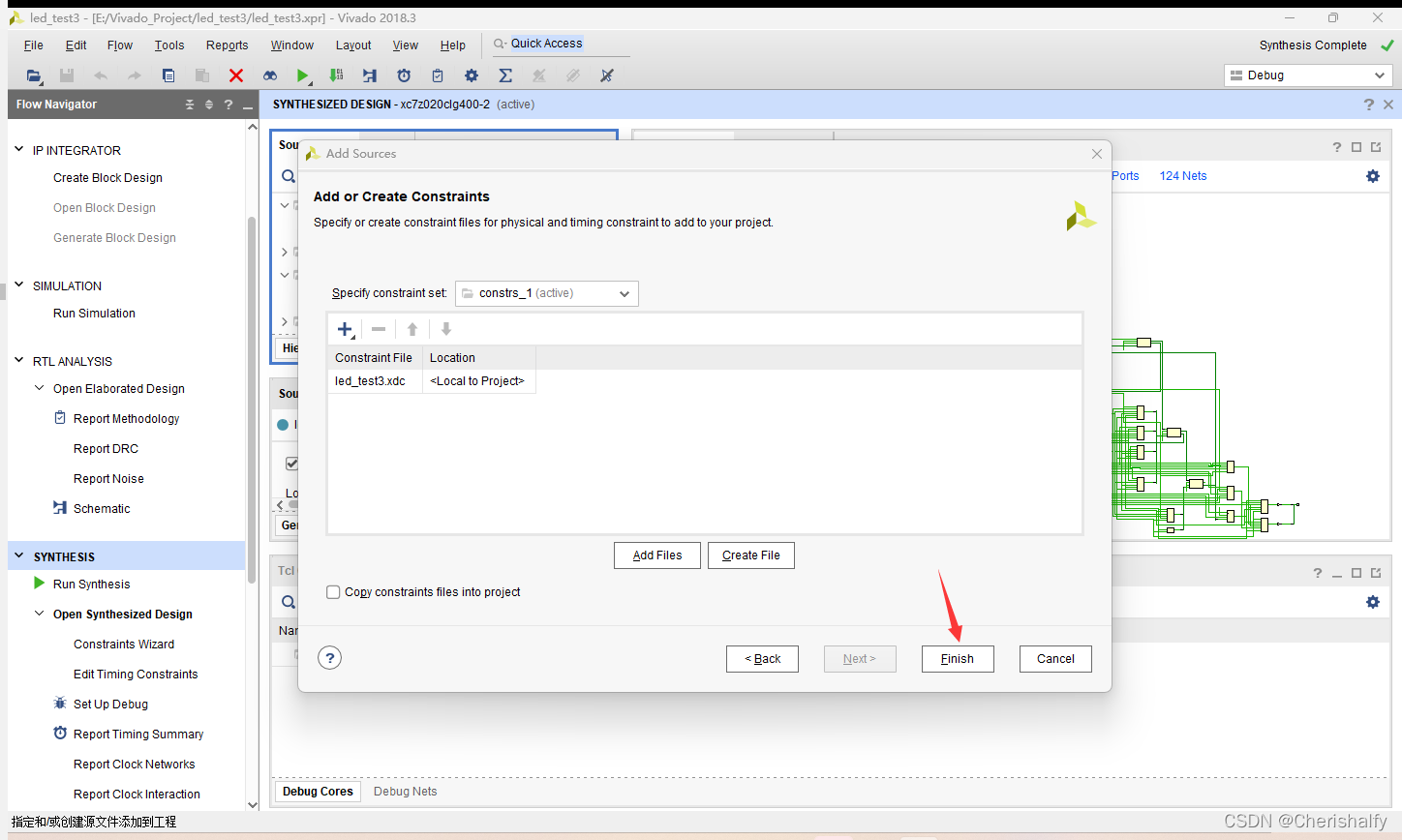

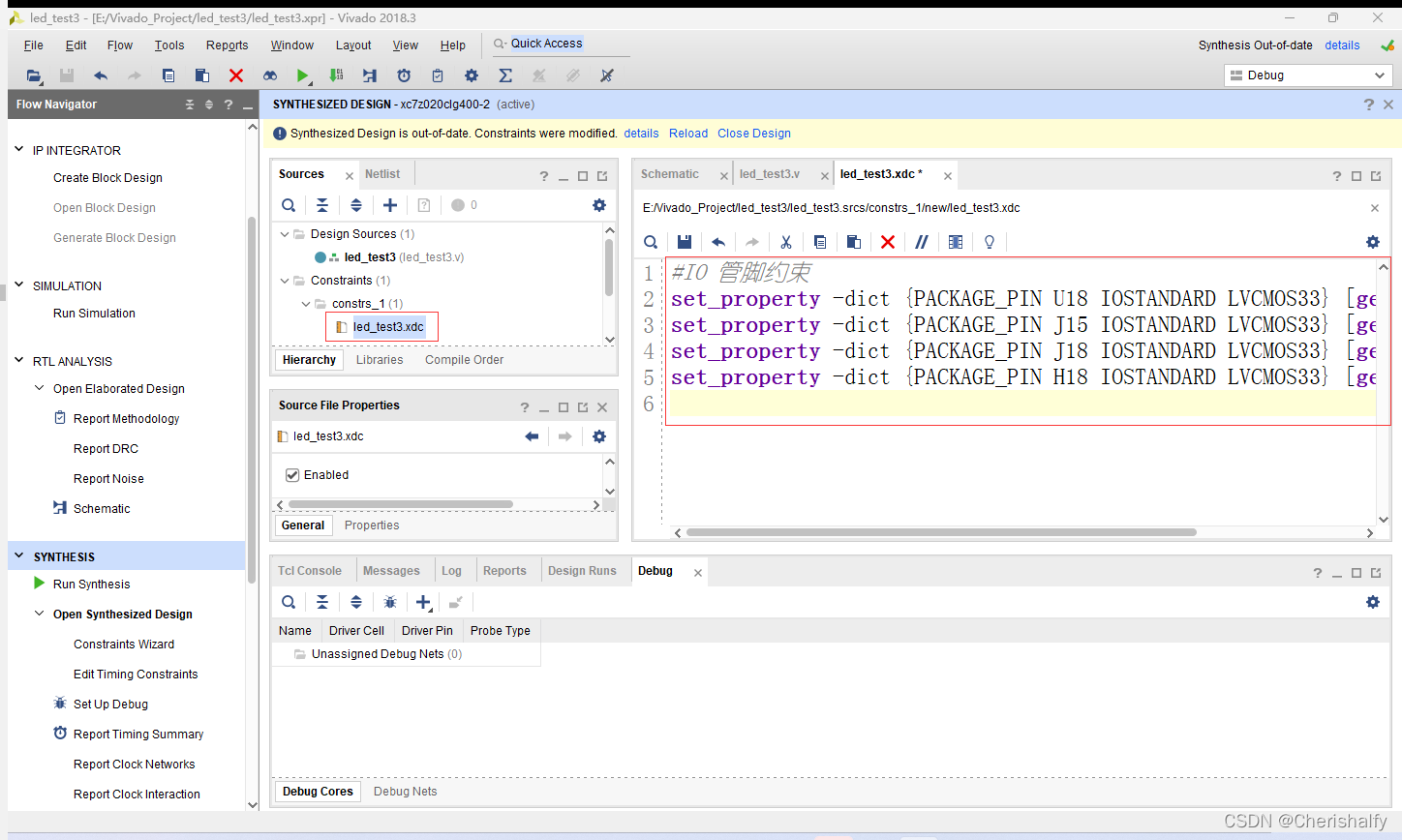

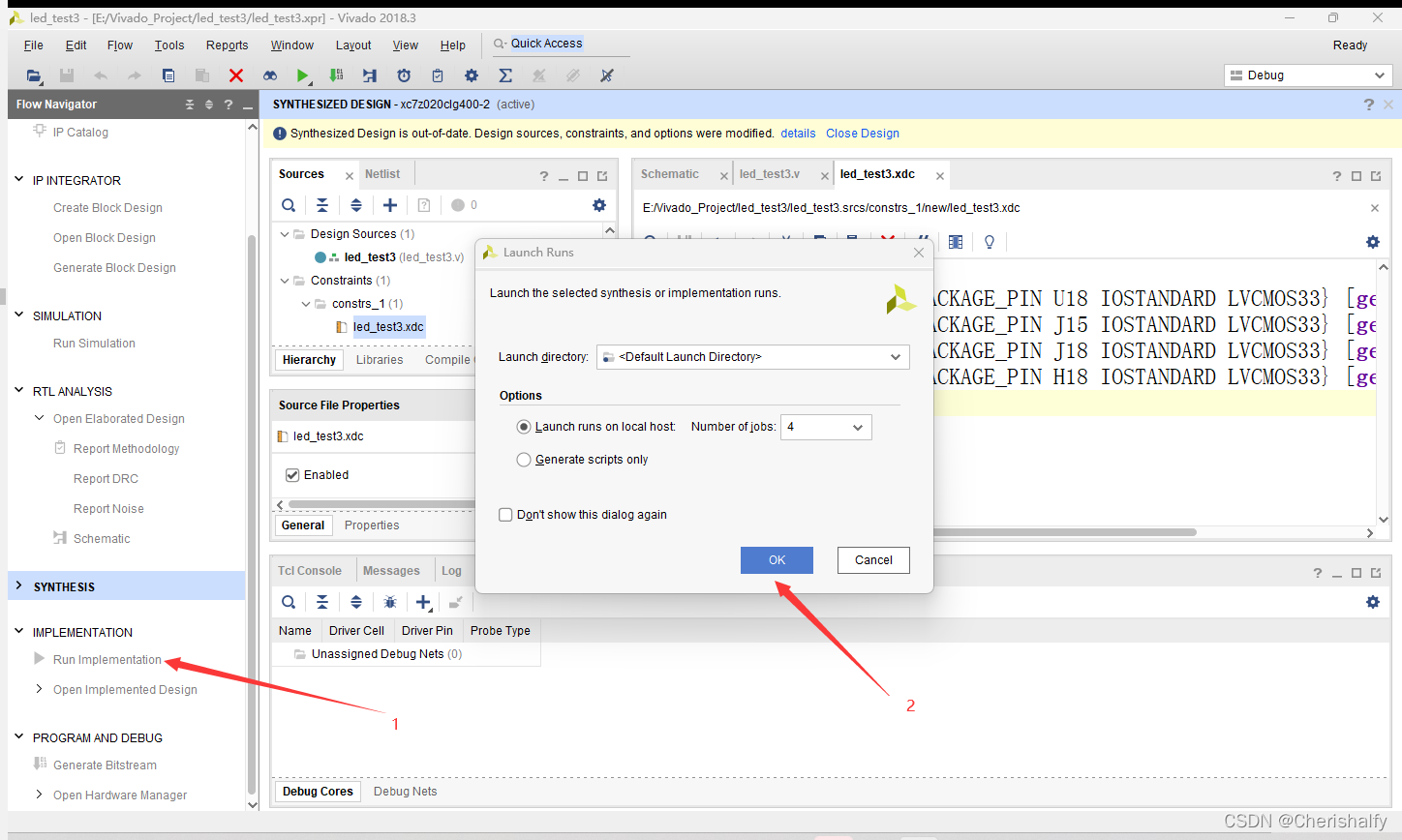

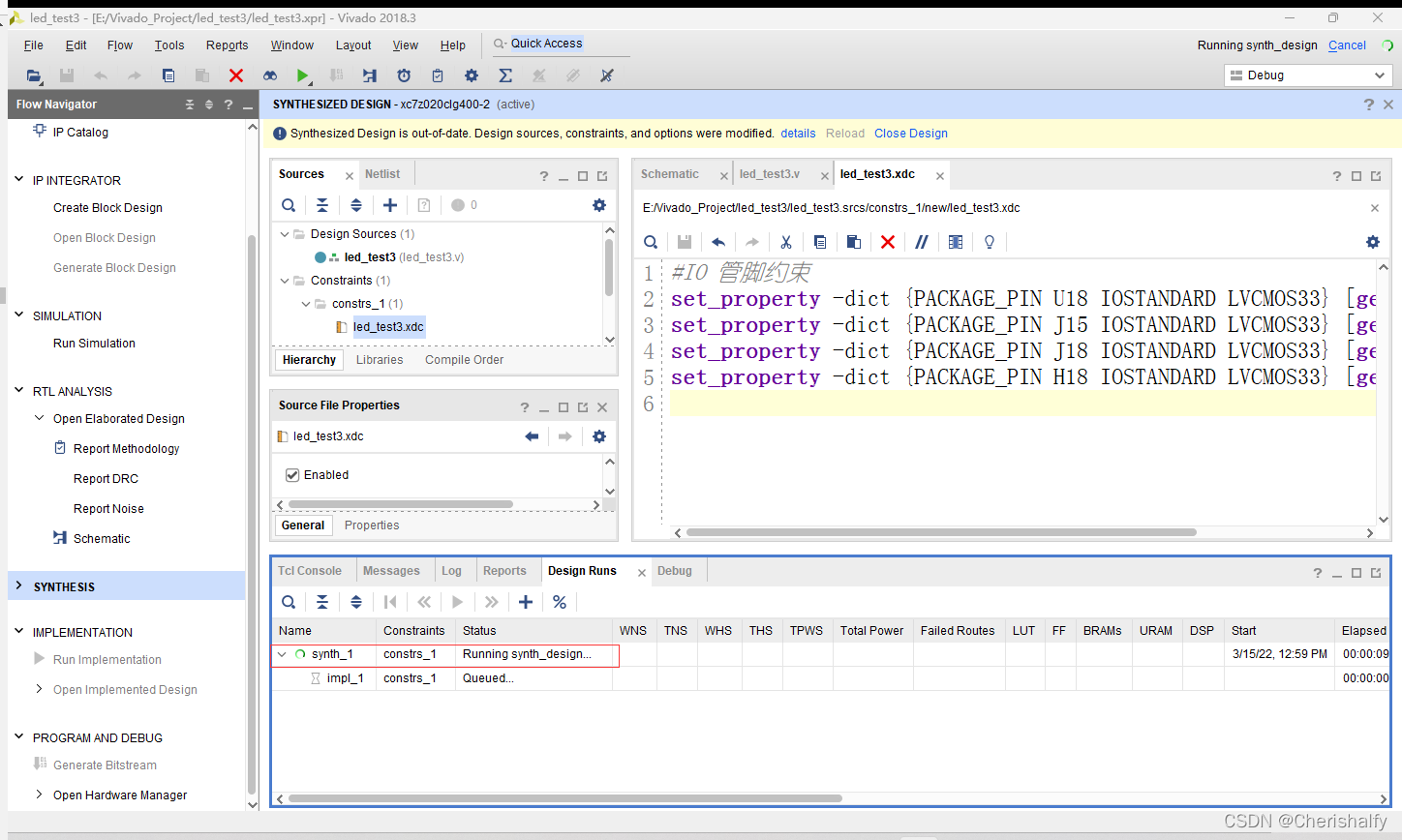

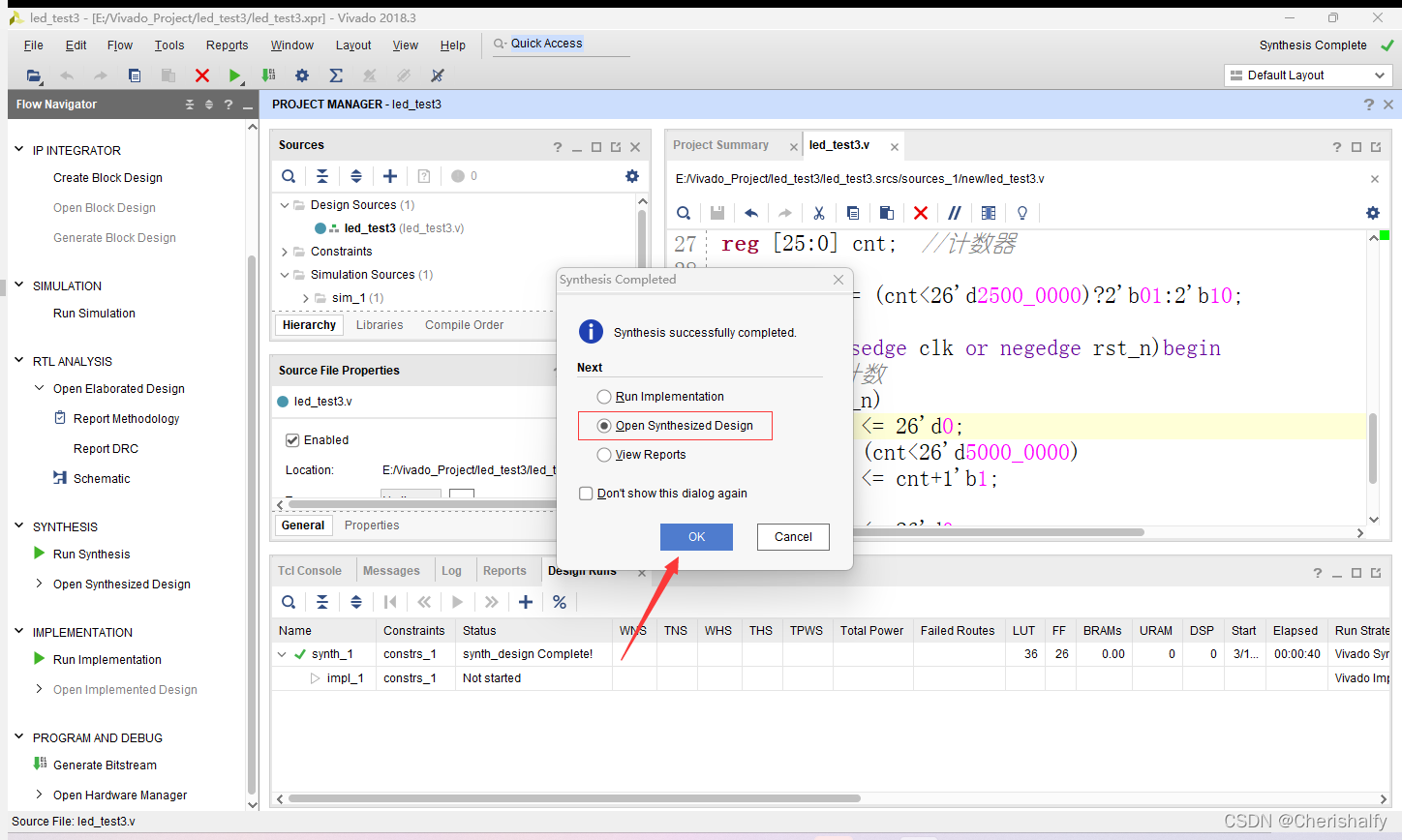

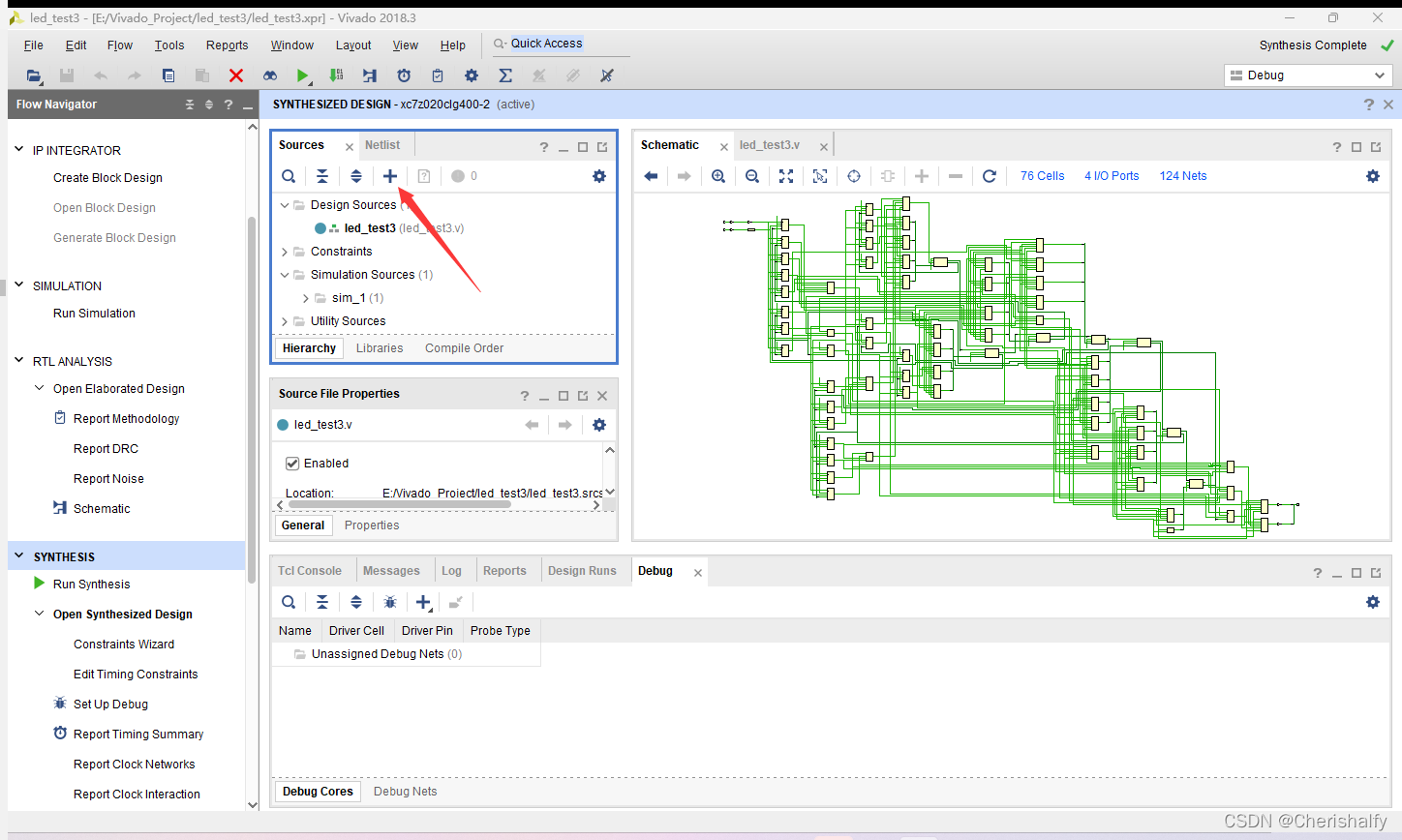

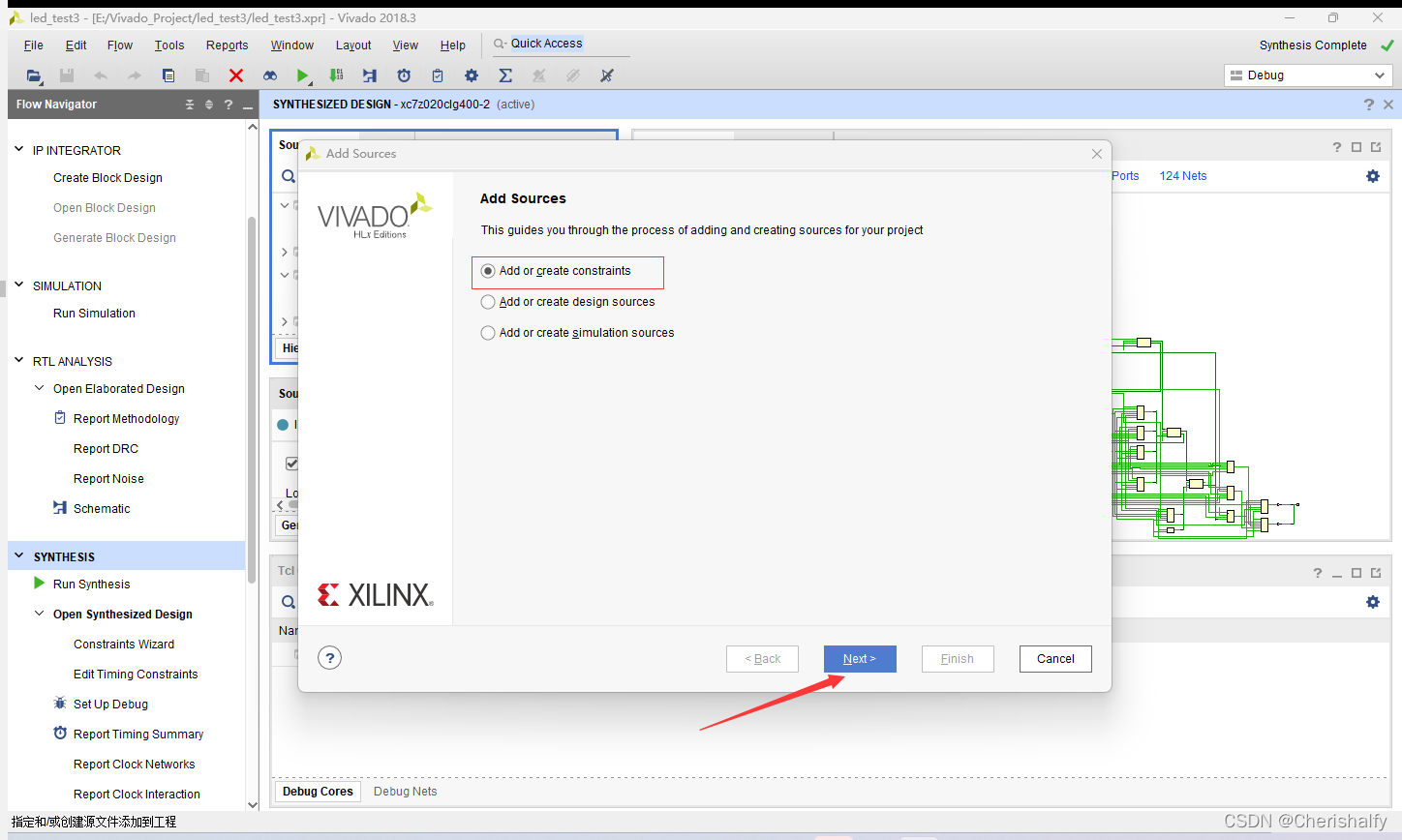

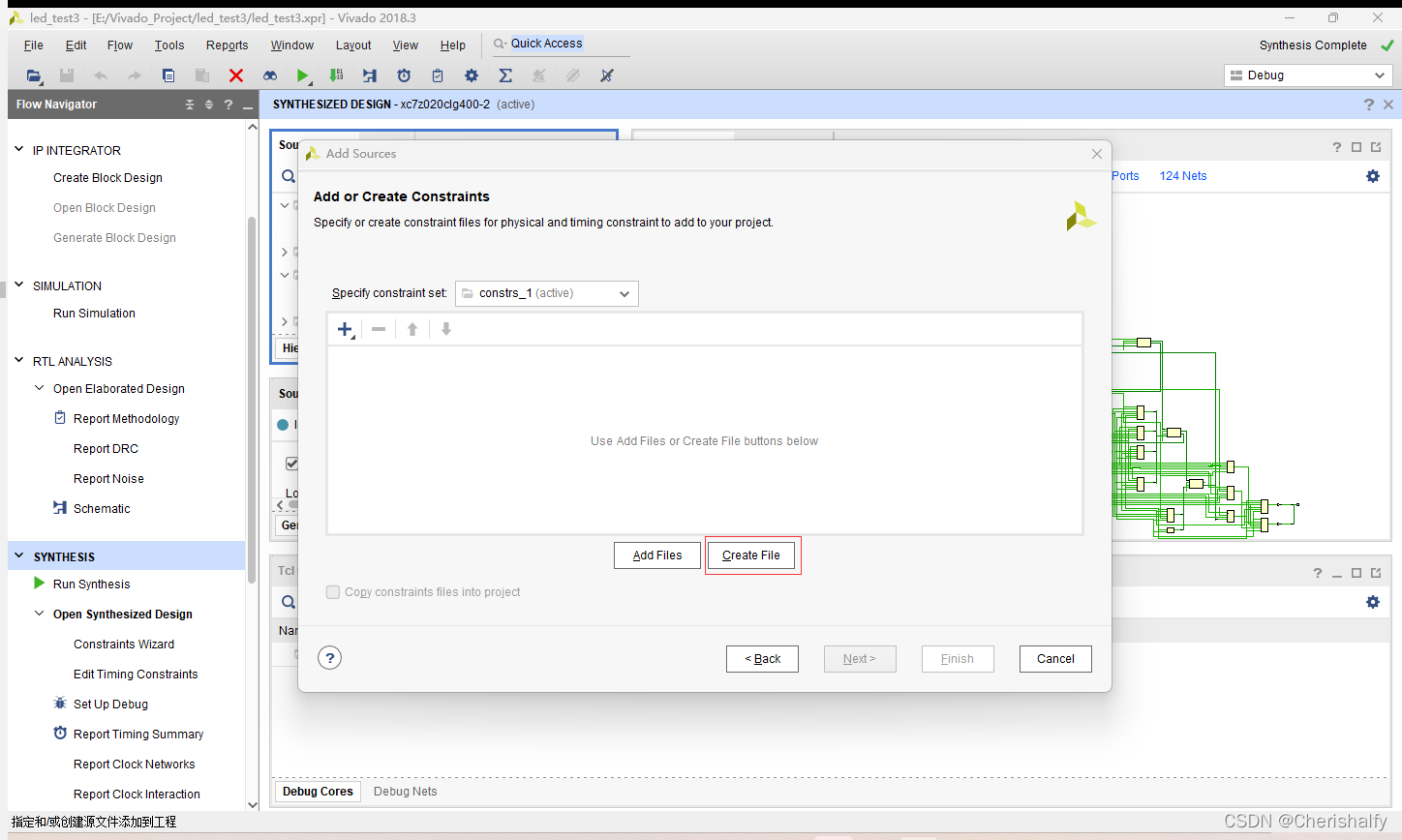

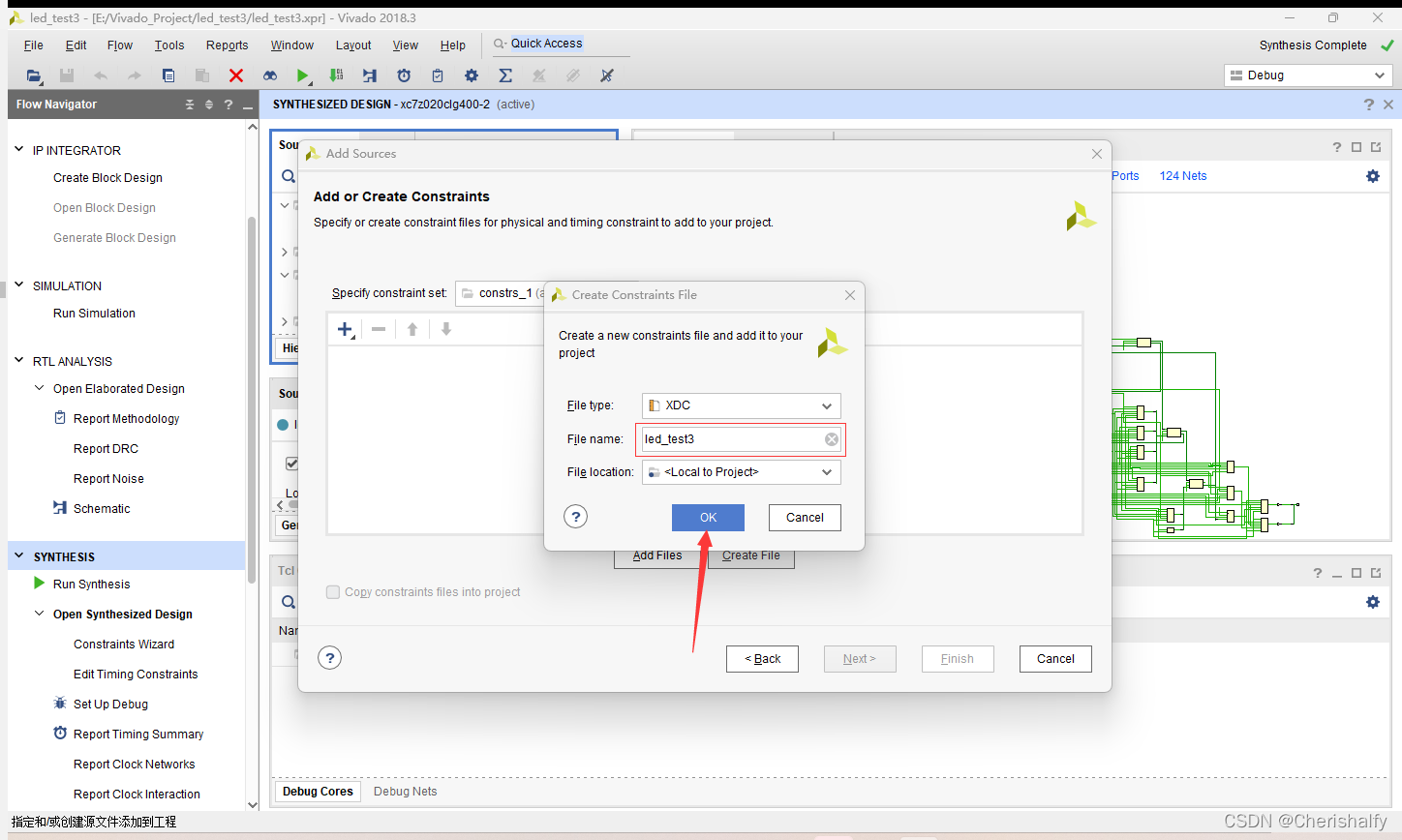

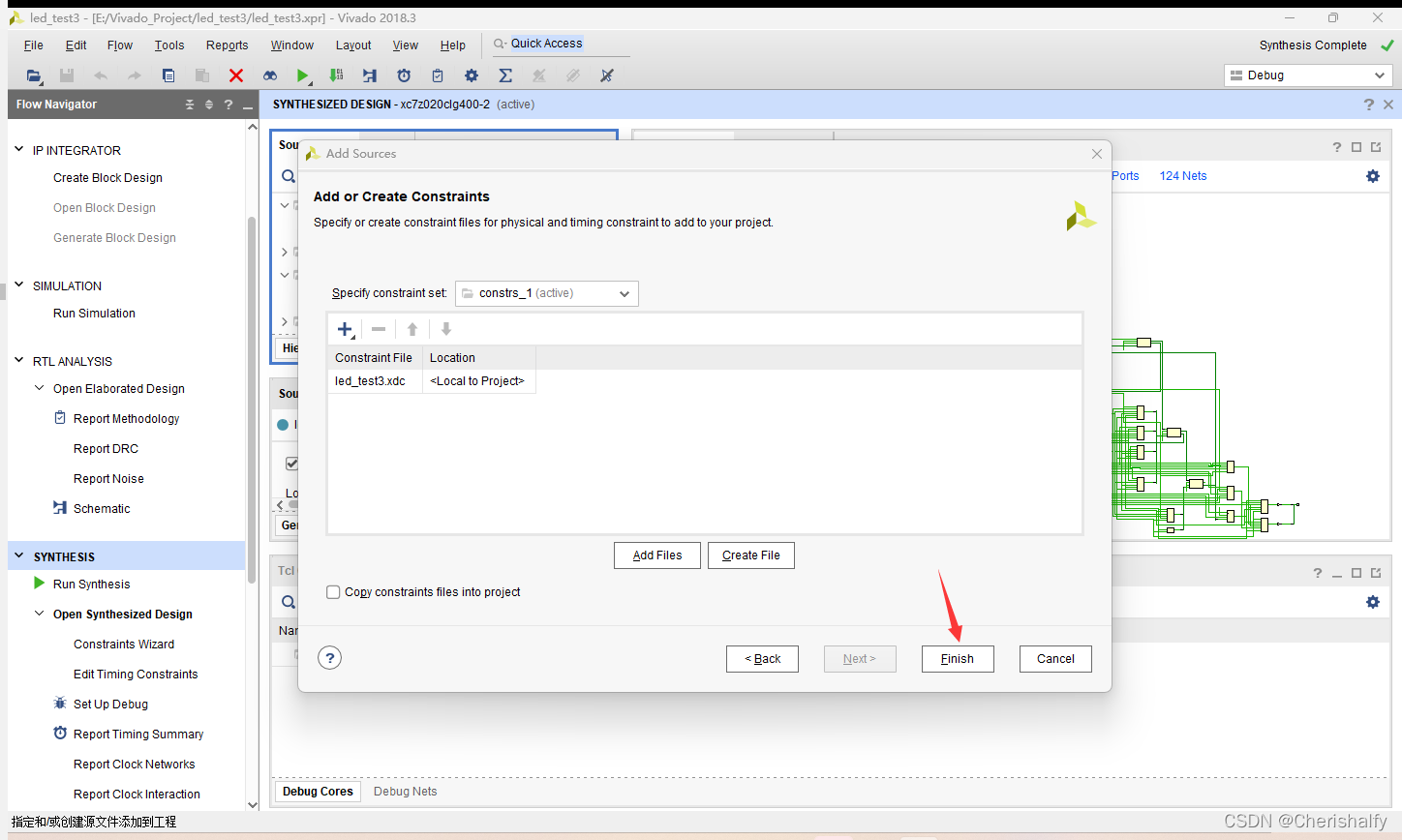

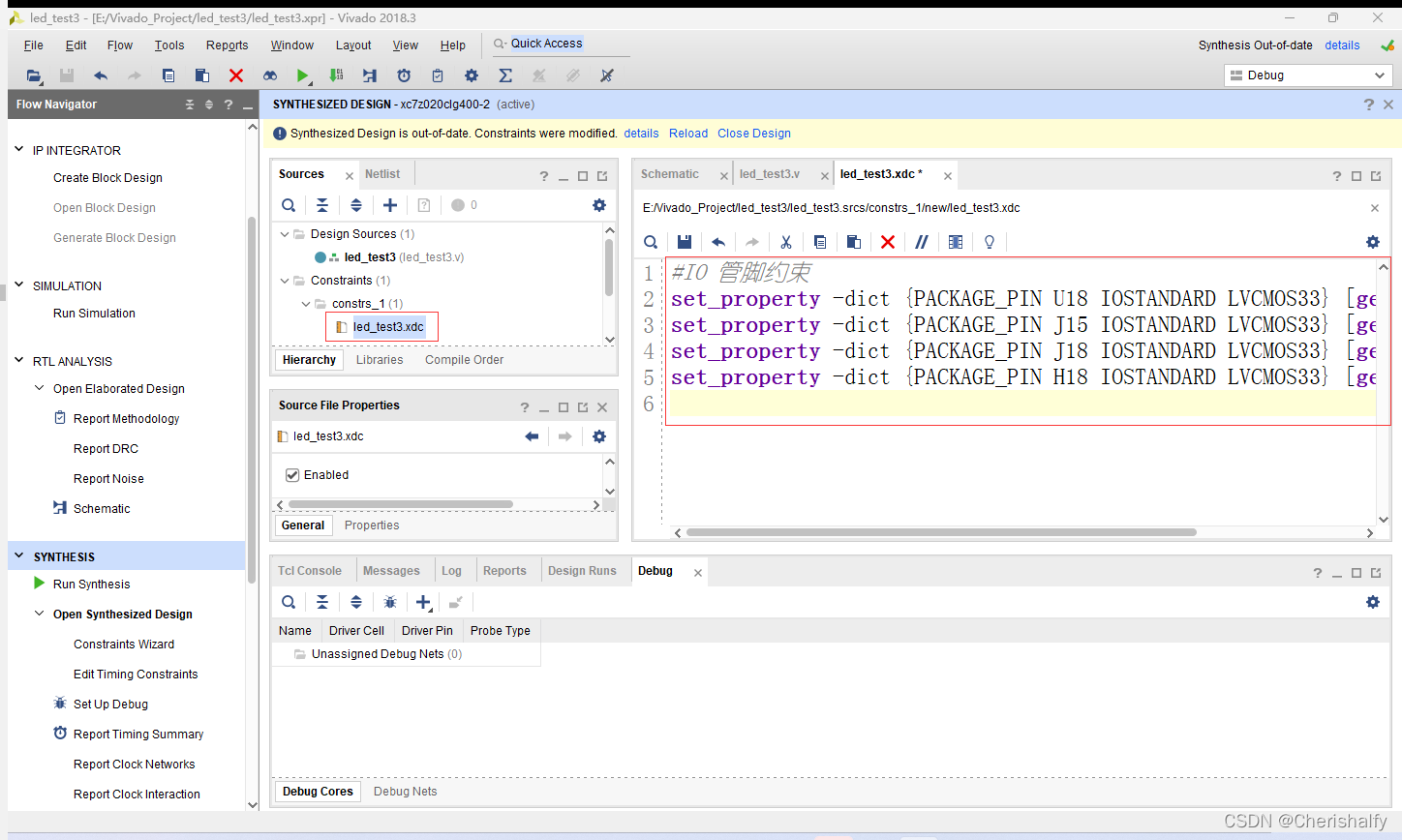

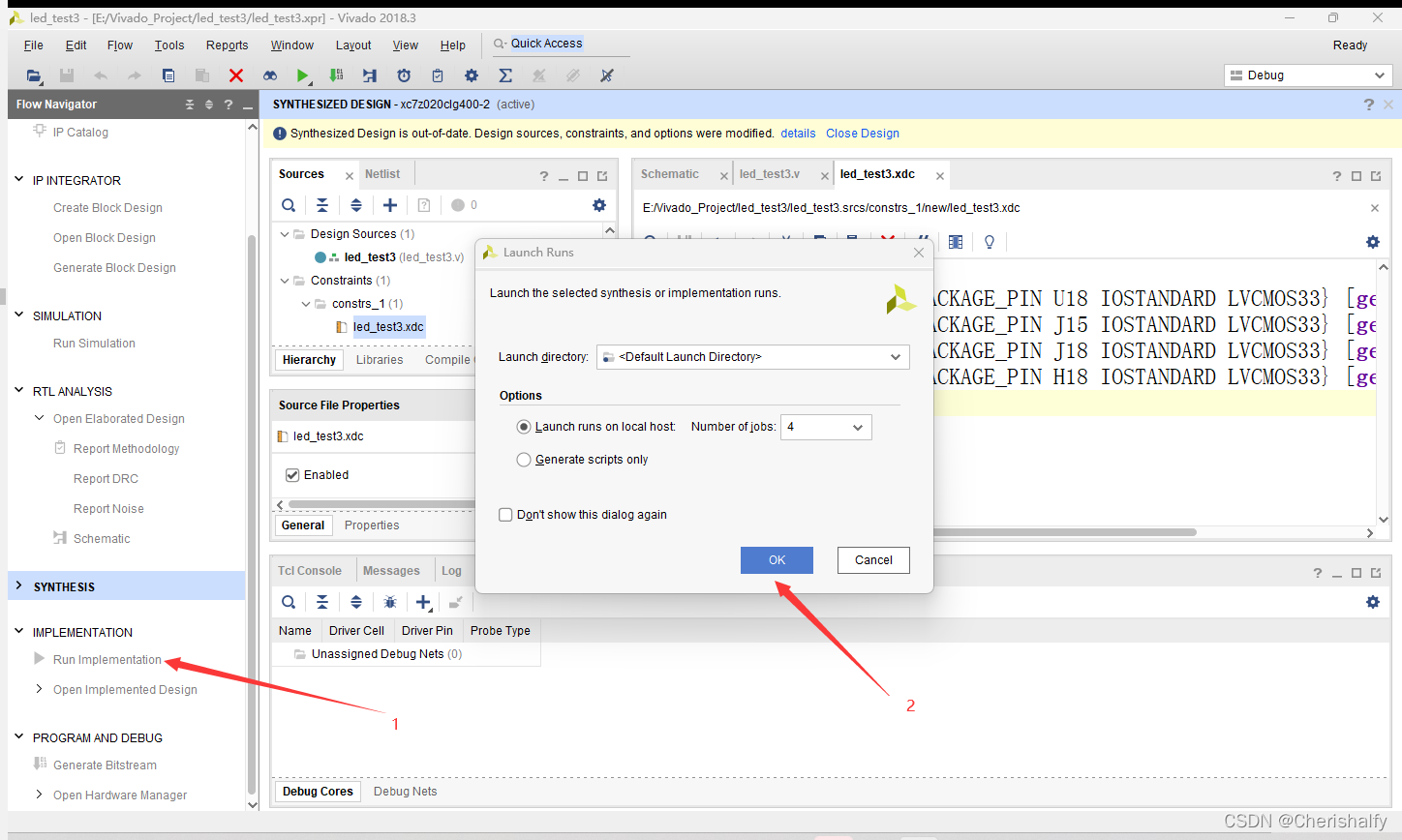

综合仿真之后就是进行设计于实现

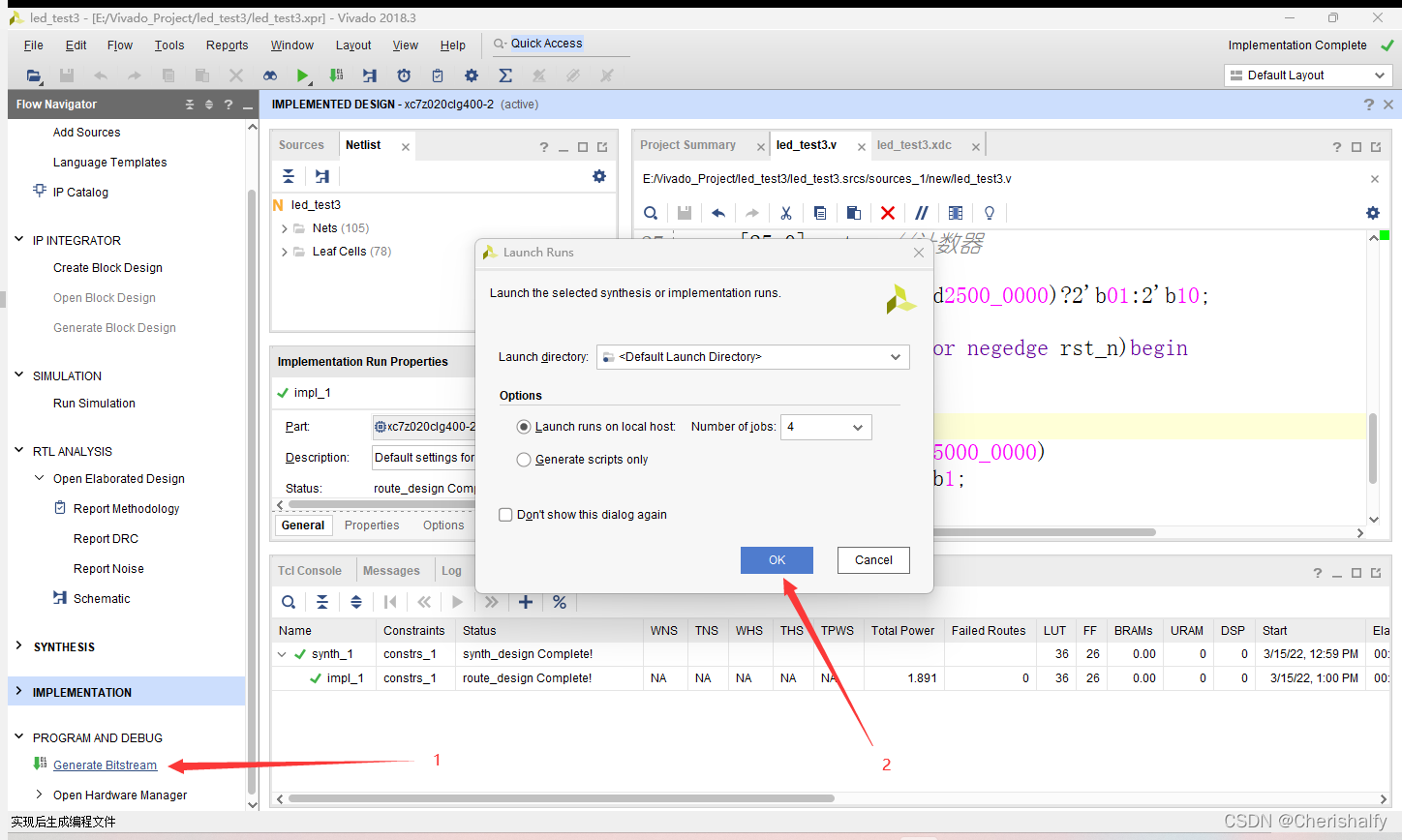

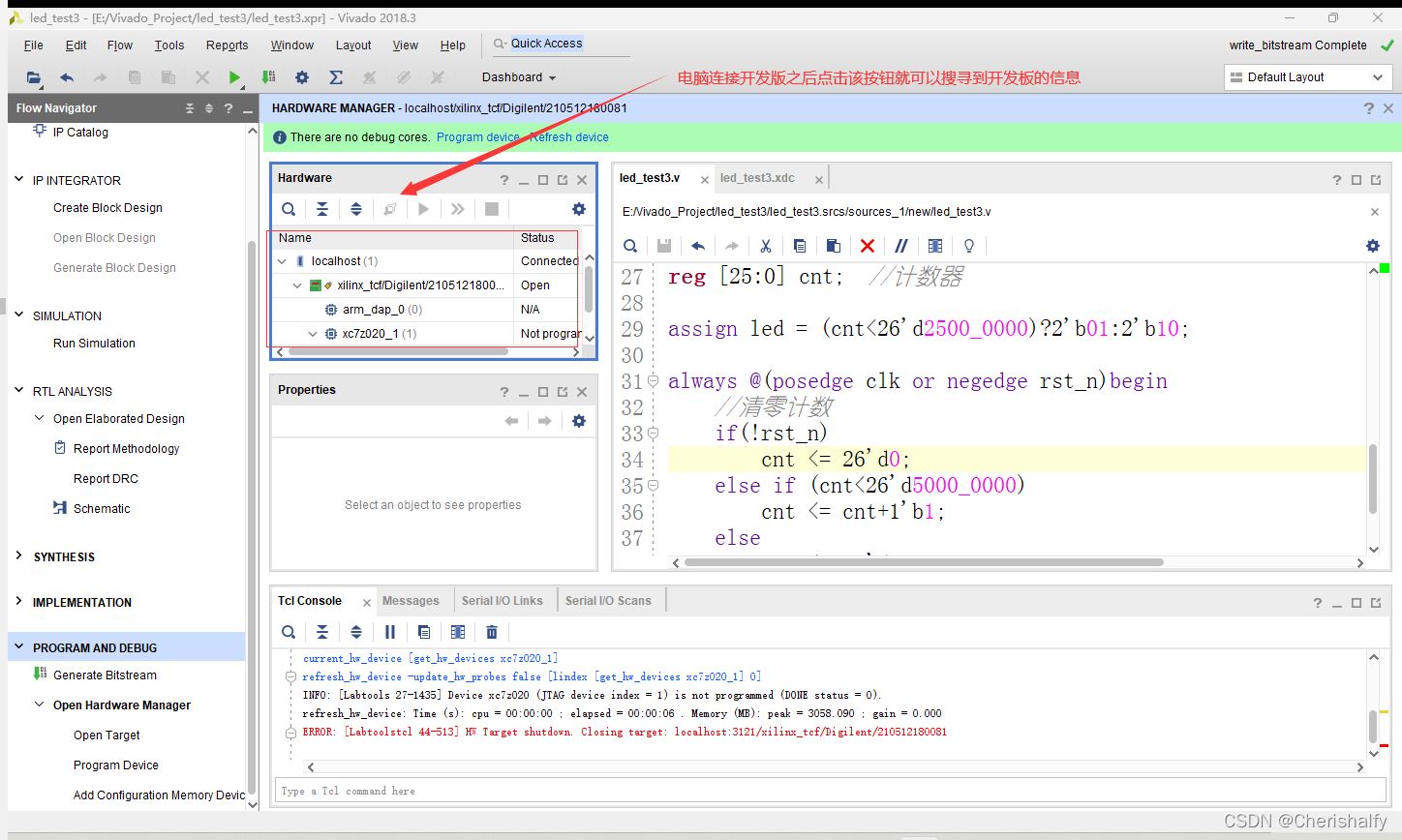

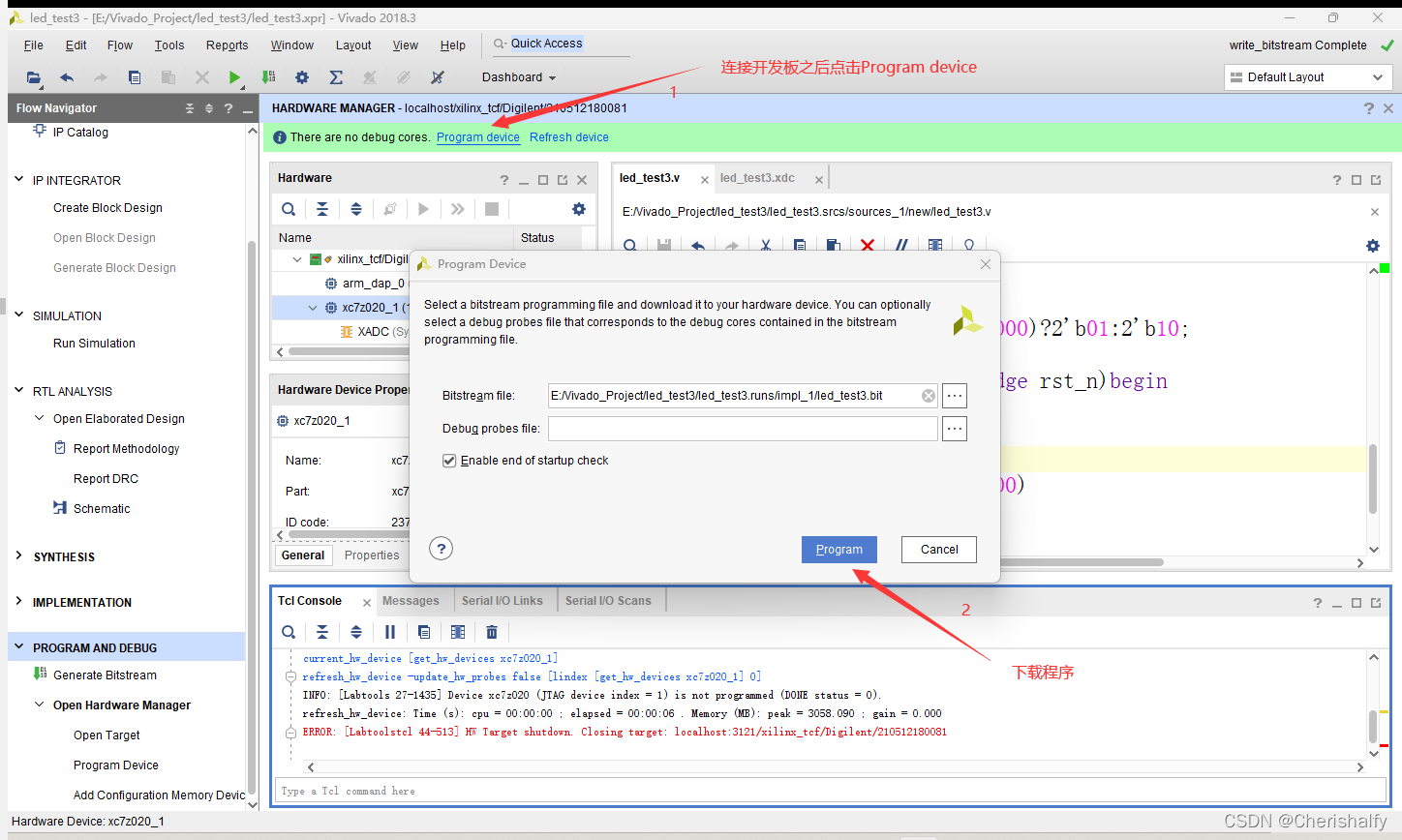

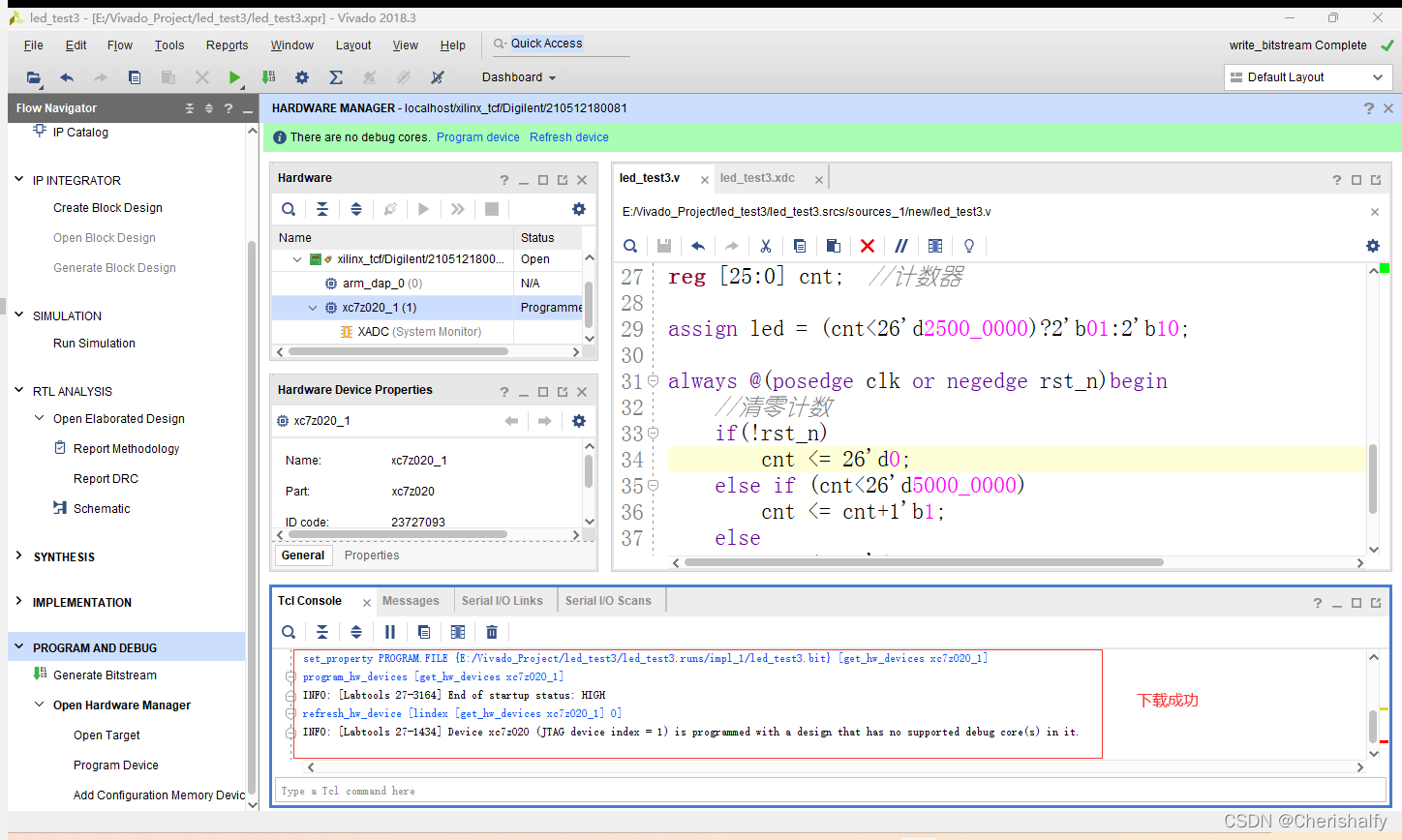

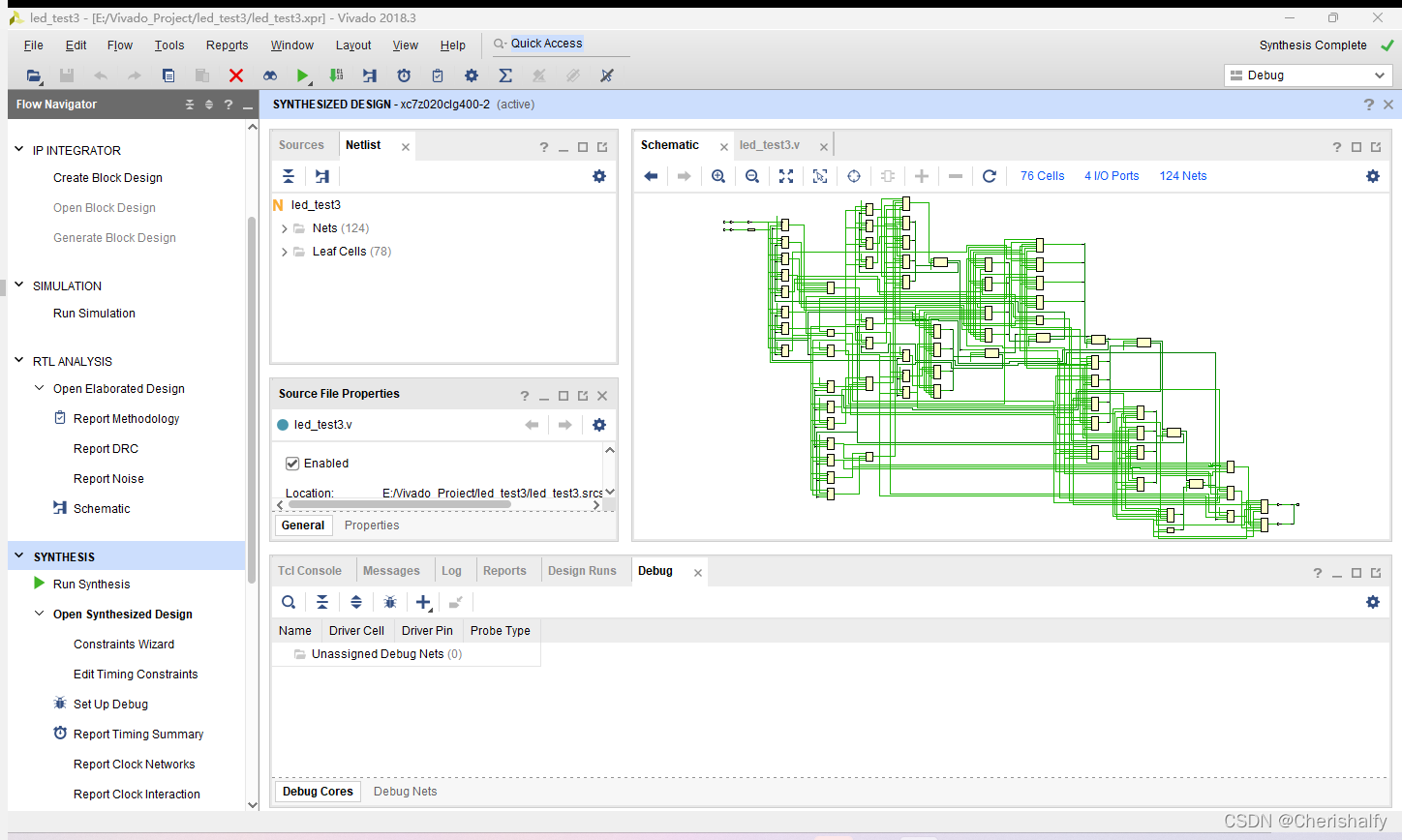

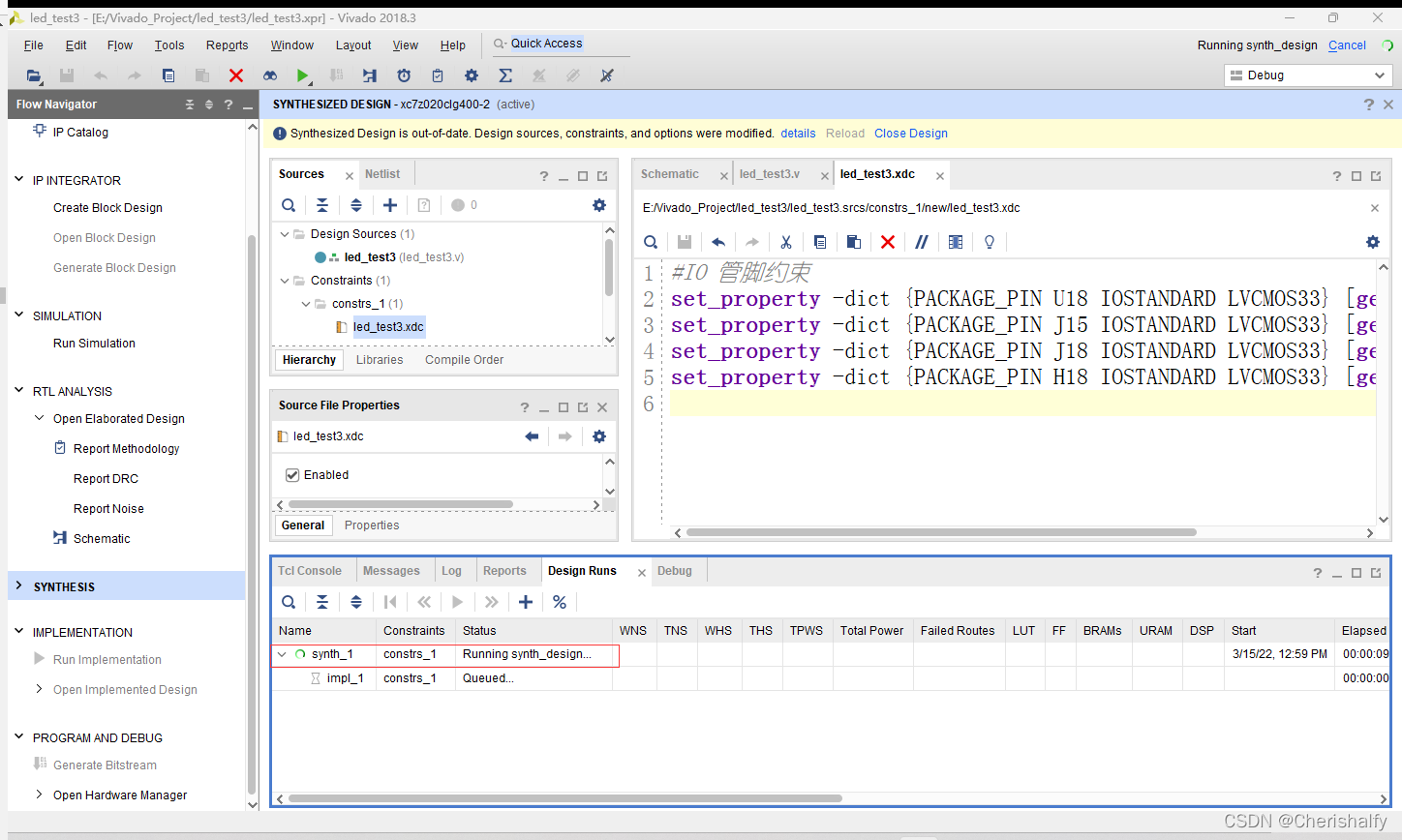

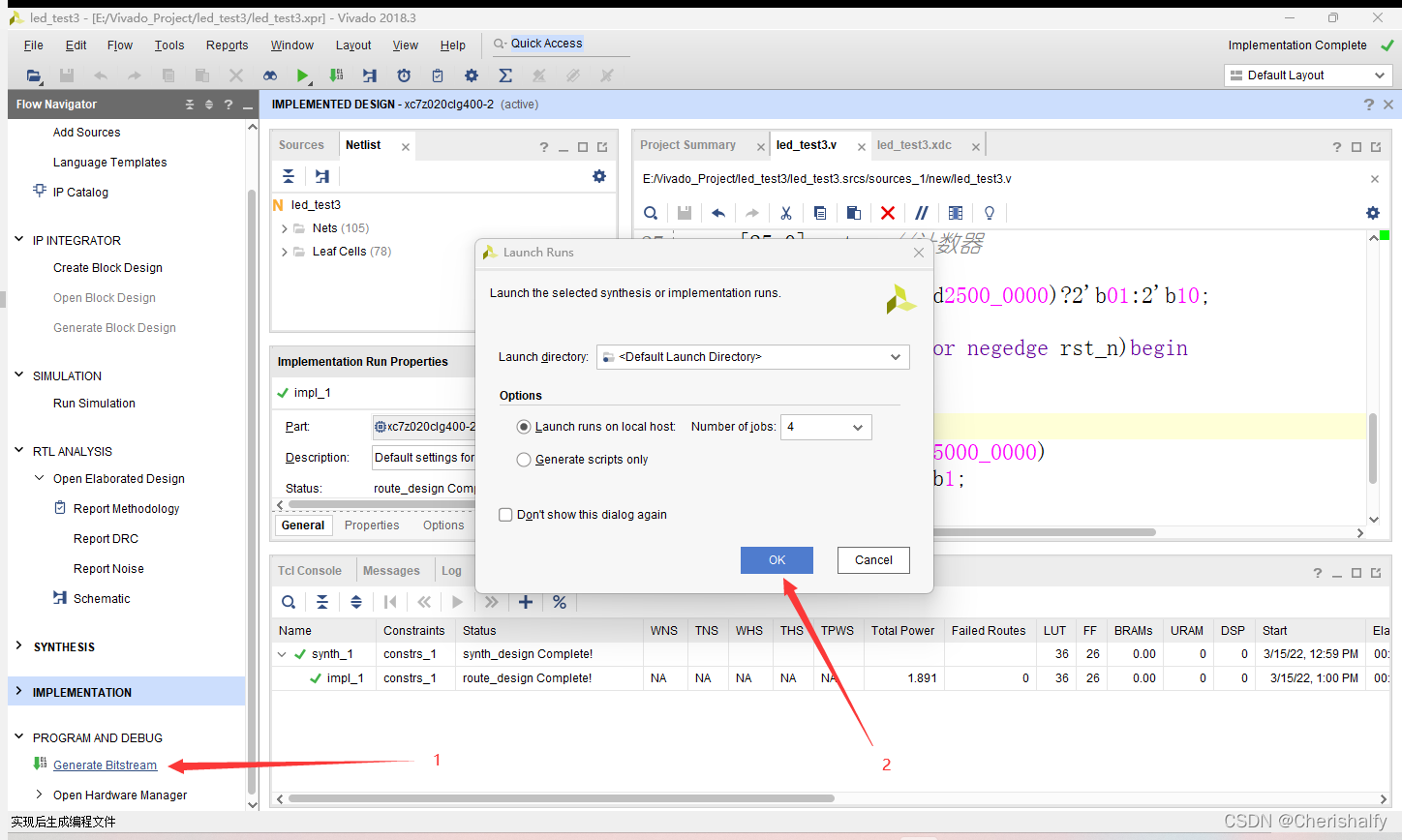

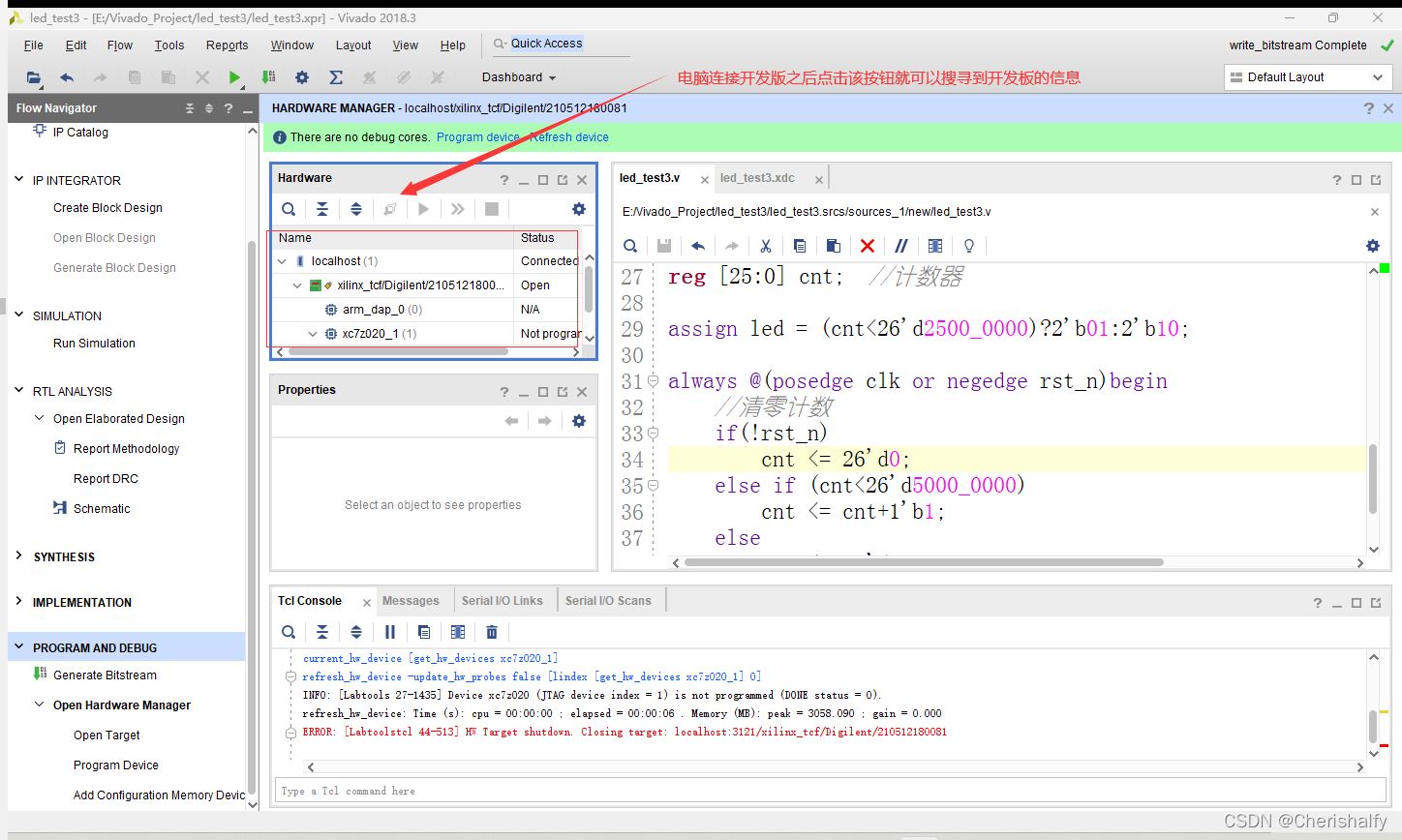

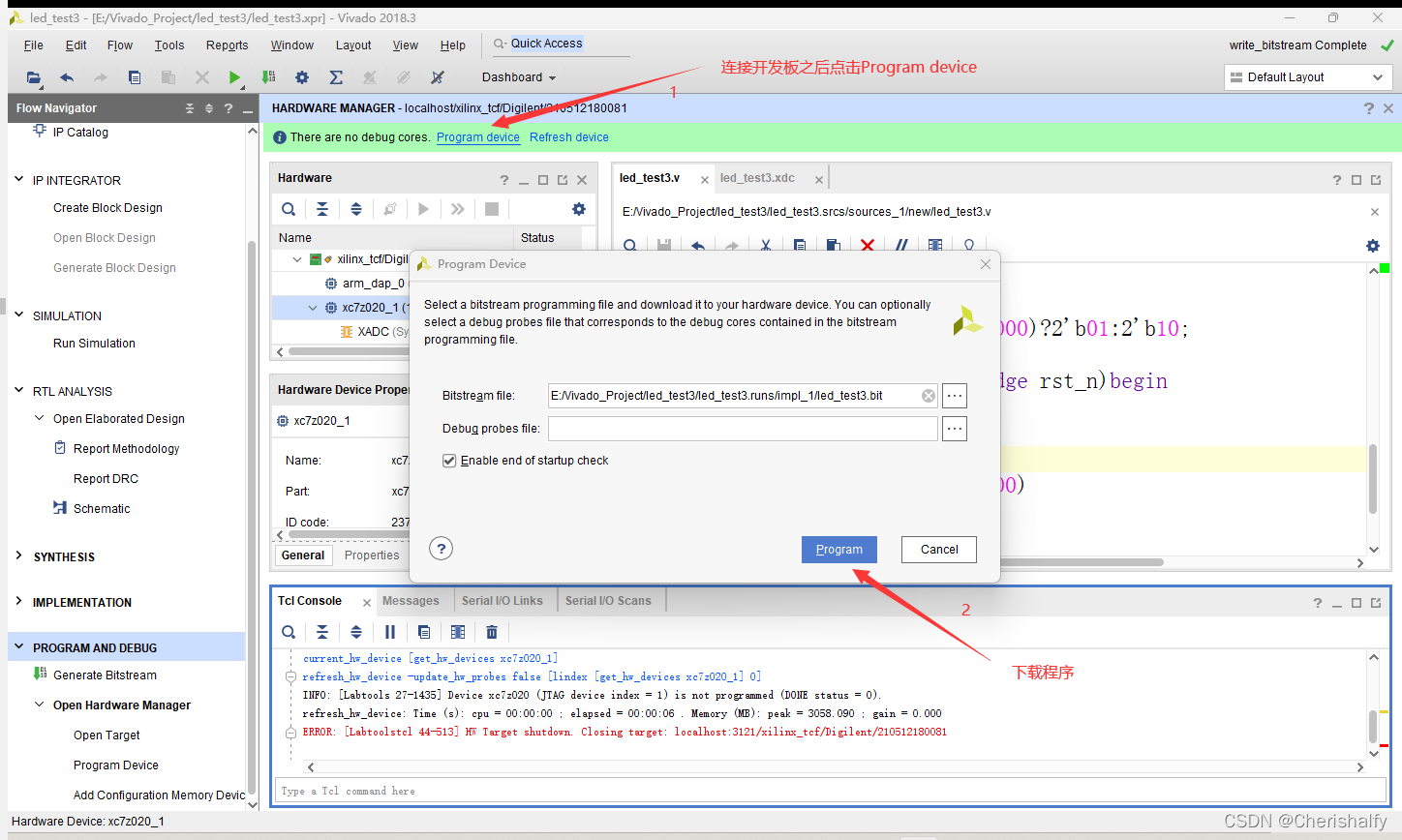

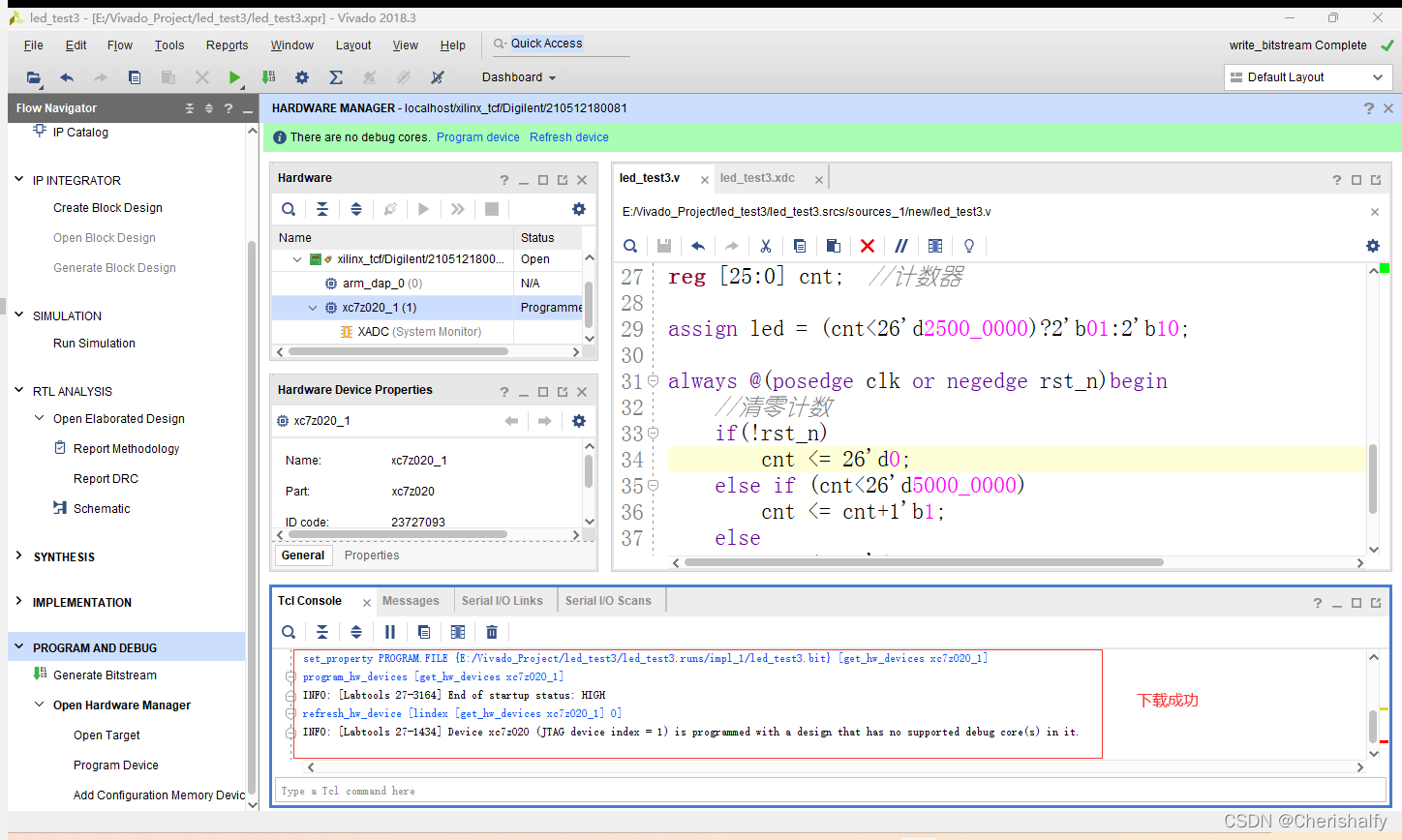

等待接收之后就是生成比特流以及下载

别写好Verilog代码之后点击RTL ANALYSIS目录下的Open Elaborated Design按钮生成模块的RTL图

产生RTL之后软件界面变化如下

综合仿真之后就是进行设计于实现

等待接收之后就是生成比特流以及下载

7633

7633

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?