FIFO的配置过程介绍

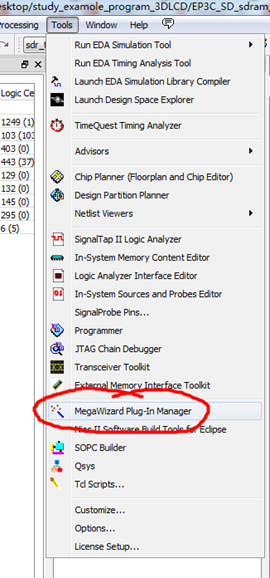

1、建立FIFO

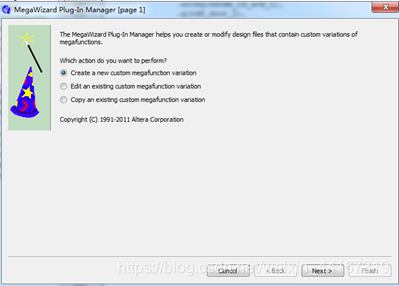

2、建立一个新的

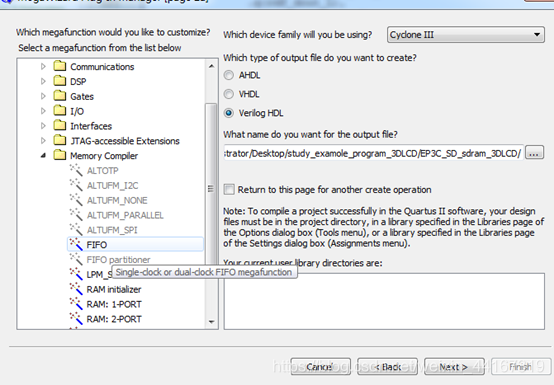

3、找到FIFO

选择Verilog hdl 并命名。

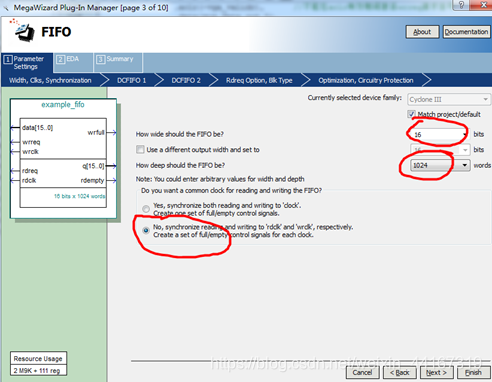

4、然后到了设置界面

这里包括:位宽设置为16,深度设置为1024,选择输入时钟与输出时钟不同。

然后,选择默认

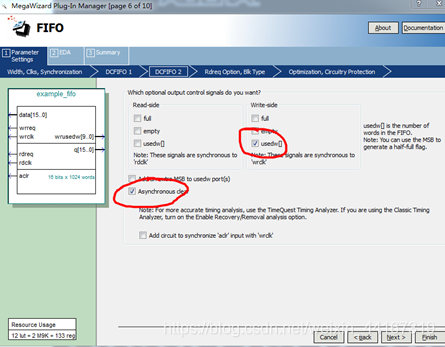

5、然后选择输出的信号

第三页(第二页默认),因为这是同步FIFO即读写频率一致,所以不需要考虑是否处在数据溢出或者空的情况,只需要设置足够的FIFO深度即可。另外在设置一个清除信号,因为需要设置图片的切换,这里需要将FIFO中的数据进行清除。

后面两页默认,EDA默认

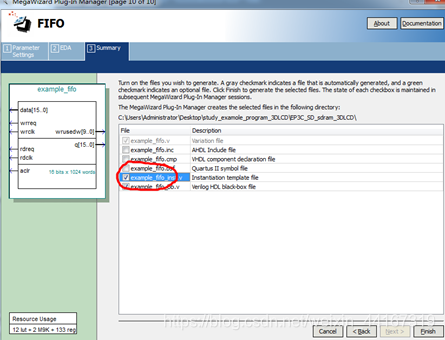

6、进行输出文件的选择

这里多勾选一个——inst文件。

然后按FINISH,完成

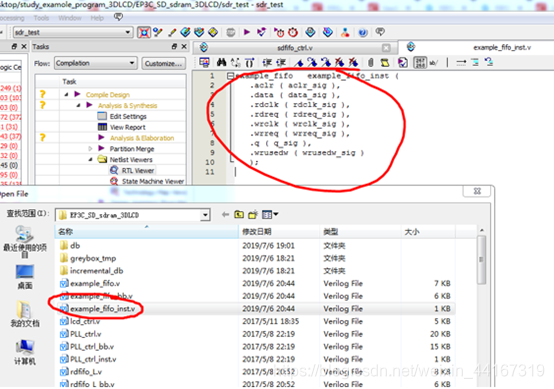

7、然后添加到工程文件

这里会弹出一个询问窗口。(没有截图到)我觉得这里应该勾选自动生成生什么的。

如果没有,勾选那就用软件打开上面生成的INST文件,并修改各个端口接入。然后进行编译就能让FIFO自动生成在文件目录下了。

本文详细介绍使用Verilog HDL配置FIFO的过程,包括建立、参数设置、信号选择及输出文件等步骤,强调同步FIFO设计中深度设定与清除信号的重要性。

本文详细介绍使用Verilog HDL配置FIFO的过程,包括建立、参数设置、信号选择及输出文件等步骤,强调同步FIFO设计中深度设定与清除信号的重要性。

5740

5740

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?