FDCE:异步复位触发器

Single Data Rate D Flip-Flop with Asynchronous Clear and Clock Enable (posedge clk)

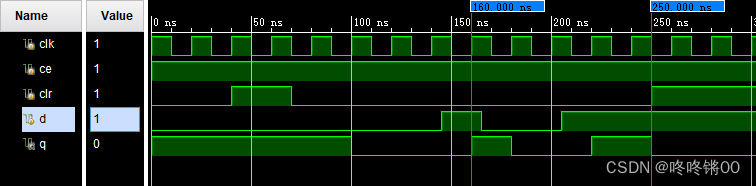

注:前100 ns 为初值保持时间,此时操作无效

Templates:

FDCE #(

.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)

) FDCE_inst (

.Q(Q), // 1-bit Data output

.C(C), // 1-bit Clock input

.CE(CE), // 1-bit Clock enable input

.CLR(CLR), // 1-bit Asynchronous clear input

.D(D) // 1-bit Data input

);等效代码:

always @(posedge clk or posedge clr)

begin

if(clr)

q <= #1 1'b0;

else

q <= #1 d;

end

FDPE :异步置位触发器

Single Data Rate D Flip-Flop with Asynchronous Preset and Clock Enable (p

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?