1、USB2.0代码分析

1.1 介绍

以opencores平台提供的usb2.0 IP进行代码分析,以温习usb2.0的协议。

支持以下的规格

- 全速和高速模式,最高480Mb/s;

- 支持wishbone接口,UTMI接口;

- 设备最多支持16个端点,缓冲区支持512、1024、1536、2048等字节大小;

- 支持小端模式;

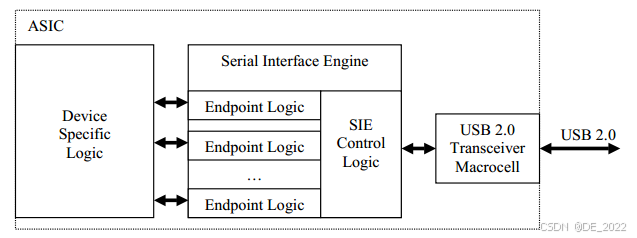

2.1 架构分析

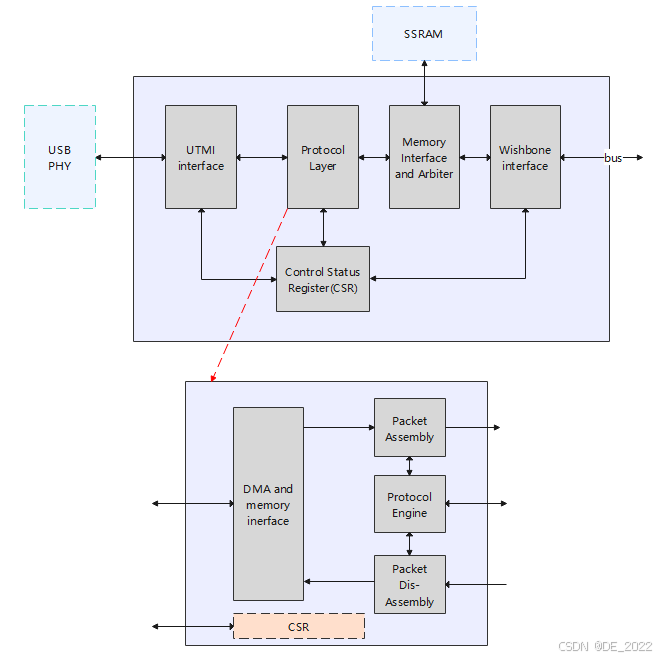

下面是USB2.0 IP架构框图

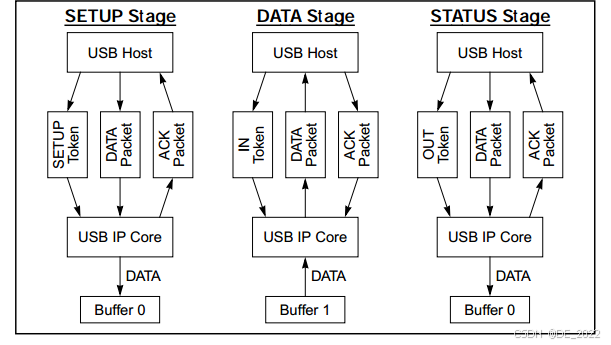

对于控制传输,setup 和status的数据都写入buffer0中,buffer0作为OUT缓冲区。DATA取buffer1的数据。读取数据的上溢出和写数据下溢出都必须以NACK回应。

待补充…

USB3.0的数据收发的数据流

2、xHCI协议

这里主要讲解xHCI协议,帮助大家理解USB主机控制器与软件的数据交互过程,学会定位USB验证环境问题。

2.1 xHCI架构

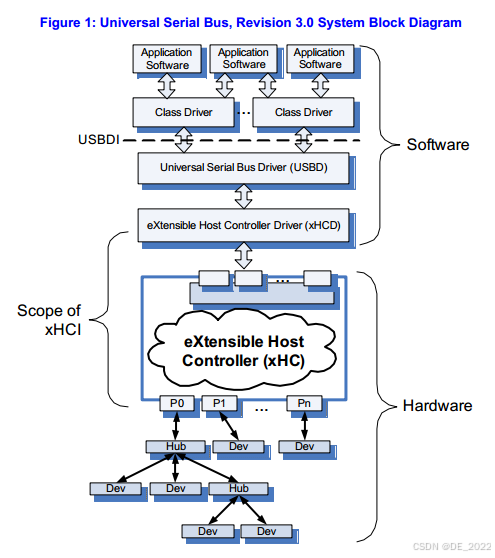

USB主机系统由许多硬件和软件层组成。下面是接口架构

应用程序软件:该软件使用一个或多个USB设备提供的服务。

类驱动软件:该软件在主机PC上执行对应于USB设备的特定“类”(大容量存储,人机界面,音频等)。类驱动软件通常是操作系统的一部分或与USB设备一起提供。

USB驱动(USBD):USBD是一个系统软件总线驱动程序,它抽象了特定操作系统的特定主机控制器驱动程序的细节。USBD提供给系统的通用USB接口被称为USB驱动程序接口或USBDI。

主机控制器驱动程序(xHCD):xHCD在主机控制器硬件和USBD之间提供软件层。

主机控制器(xHC):主控制器是主控制器体系结构的特定硬件实现。

USB设备:这是一种硬件设备,用于扩展总线拓扑(集线器)或执行有用的终端用户功能。

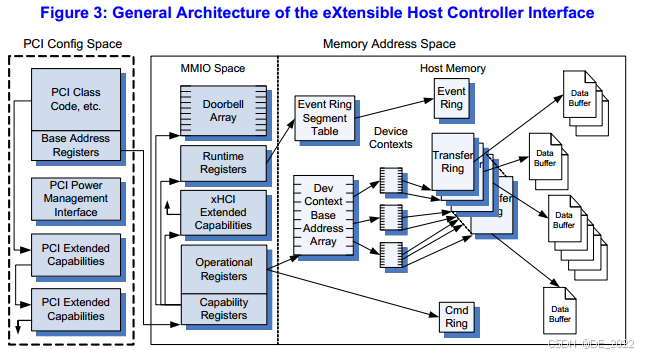

xHCI接口定义了三个接口空间

(1)主机配置空间: 每个xHC实现都应包括一种通过系统软件识别和枚举主控制器的方法。本规范提供了一个主机配置空间的PCI示例,它被称为PCI配置空间。PCI配置空间定义提供了配置空间用于系统xHC枚举和资源(中断、电源、虚拟化等)管理的工作示例。

(2)MMIO空间: 寄存器空间表示由xHC呈现给驻留在内存地址空间中的系统软件的硬件寄存器。寄存器空间提供特定于实现的参数,这些参数定义在xHCI正常和扩展功能寄存器、操作和运行时控制和状态寄存器以及用于标记对单个USB设备的访问的门铃阵列中。这个空间通常称为I/O空间,实现为内存映射I/O (MMIO)空间。

(3)主机内存:该空间由控制数据结构(设备上下文基地址数组、设备上下文、传输环等)和数据缓冲区定义,这些数据结构由xHC驱动程序分配和管理,以启用单个设备的端点流量。这个空间是在内存地址空间的内核区和用户区分配的。

xHCI提供对两类USB传输类型的支持:异步和周期性。同步传输和中断传输是周期性传输类型。异步传输类型包括控制和批量。

xHC寄存器接口由4个主要组件组成:能力寄存器、操作寄存器、运行时寄存器和门铃阵列。操作寄存器和能力寄存器连接在MMIO空间中。运行时寄存器实际上只是操作寄存器的扩展。它们的分区允许运行时寄存器驻留在单独的页面边界上,从而使xHC能够更好地支持虚拟化。在能力寄存器中提供了xHCI能力指针机制(类似于PCI定义的机制),以指向xHC实现的新功能或可选功能。

能力寄存器指定主控制器实现的只读限制、限制和能力。这些值用作主机控制器驱动程序的参数。

运行时寄存器和操作寄存器指定主控制器配置和运行时可修改状态,系统软件使用它们来控制和监视主控制器的运行状态。

xHCI扩展功能指定了xHC实现的可选特性,并提供了在本规范发布后向实现添加新功能的能力。

门铃阵列是一个多达256个门铃寄存器的阵列,支持多达255个USB设备或集线器。每个门铃寄存器为系统软件提供了一种机制,用于通知xHC是否有槽或端点相关的工作要执行。

device slot用作与单个USB设备相关联的一组xHCI数据结构的通用引用.。

每个设备由设备上下文基址数组(Device Context Base Address Array)中的一个条目、门铃数组寄存器中的一个寄存器和设备的设备上下文表示。术语Slot ID是指用于标识特定Device Slot的索引。例如,Slot ID的值将被用作标识设备上下文基地址数组中特定条目的索引。

设备上下文基址数组最多支持255个USB设备或集线器,其中数组中的每个元素是指向设备上下文数据结构的指针。

命令环是软件用来向xHC传递与设备和主机控制器相关的命令的。命令环将被xHC视为只读的。

xHC使用事件环将命令完成和异步事件传递给软件。事件环将被系统软件视为只读。

软件使用传输环来调度单个USB端点的工作项。传输环被组织为传输描述符( Transfer Descriptor TD)数据结构的循环队列,其中每个传输描述符定义一个或多个将被移动到USB或从USB移动的数据缓冲区。传输环被xHC视为只读的。

所有三种类型的环都支持系统软件在它们处于活动状态时增加或缩小它们的能力。写入传输环和命令环的特殊td允许软件更改其大小,但是由于事件环对软件是只读的,因此提供了事件环段表,以便软件可以修改其大小。

2.2 xHCI数据结构

xHC用于管理设备和端点的数据结构是为了适应这种限制而设计的,要么将数据结构保持在4K字节(支持的最小页面大小)以下,要么提供机制来链接不连续的物理内存块,形成更大的、逻辑上连续的数据结构,例如,指向用于向主机传输USB数据的数据缓冲区的数据结构的循环队列。(xHCI有能力去链接不连续的物理地址)

2.2.1 设备上下文基址数组

Device Context Base Address Array (DCBAA)为xHC提供了一个基于Slot ID的查找表,用于访问与每个Slot关联的Device Context数据结构。该数据结构由指向设备上下文数据结构的指针数组组成。当检测到设备附加时:系统软件初始化device Context数据结构,从xHC请求Slot ID,并在Slot ID指示的位置将指向新创建的device Context的指针插入DCBAA。

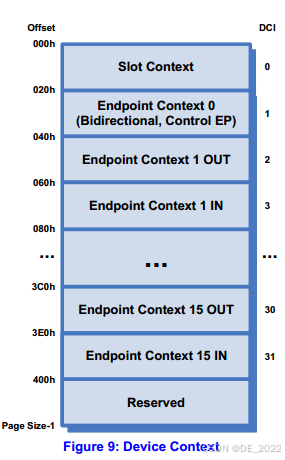

2.2.2 设备上下文

设备上下文数据结构由xHC管理,用于向系统软件报告设备配置和状态信息。设备上下文数据结构由32个数据结构的数组组成。第一个上下文数据结构(index = ’ 0 ')是一个Slot上下文数据结构。其余的上下文数据结构是端点上下文数据结构。

2.2.3 slot上下文

(1)slot上下文数据结构包含与整个设备相关的信息,或者影响USB设备的所有端点。这个数据结构被定义为设备上下文和输入上下文数据结构的成员。

(2)slot上下文提供的信息包括;控制、状态、寻址和电源管理。

(3)寻址信息用于各种目的,由xHC分配的USB设备地址可供开发人员使用总线分析仪跟踪与设备相关的USB活动。路由字符串被xHC用来瞄准超速数据包。Speed、TT Port Number和TT Hub Slot ID字段允许xHC执行分割事务,这是处理连接到高速集线器的低速和全速设备所必需的。电源管理信息包括最大退出延迟,xHC使用它来确定总线上Isoch数据包的调度。(这个段落不明白,有待理解)

(4)作为Device Context成员,Slot Context数据结构被xHC用来向系统软件报告设备参数的当前值。设备上下文的slot 上下文数据结构也被称为“output slot context”。

(5)作为Input Context成员,系统软件使用Slot Context数据结构向主机控制器传递命令参数。输入上下文的槽上下文数据结构也被称为**“input slot context**”。如果针对设备插槽的命令成功,xHC将更新输出插槽上下文,以反映它在生成命令完成事件之前积极用于管理设备的参数值。

(6)插槽上下文的xHCI保留区域可用作xHC实现定义的scratchpad。

2.2.4 端点上下文

(1)端点上下文数据结构定义了特定USB端点的配置和状态。这个数据结构被定义为设备上下文和输入上下文数据结构的成员。

(2)端点上下文的大多数字段包含端点相关的类型、控制、状态和带宽信息,这些信息与设备报告的关联端点相关描述符中的信息相对应。Endpoint Context还定义了一个TR Dequeue Pointer字段,该字段通常提供一个指向与管道关联的传输环的指针。

(3)对于USB3 Bulk端点有一个特殊的情况,其中流可能与端点相关联。流允许终端的数据流在传输环之间由设备进行多路复用。在这种情况下,引入了一个间接级别来访问与端点相关的传输环,并且端点上下文TR Dequeue指针字段包含一个指向流上下文数组数据结构的指针(通常称为流数组),其中数组中的每个流上下文数据结构可能包含一个NULL指针(如果未分配流ID)或指向传输环或与各自流相关的另一个流上下文数组。(这一块涉及流,有待理解)

注意,Device Context和Input Context数据结构提供了USB设备可以声明的所有可能的(31)端点。大多数设备只声明少量端点,这意味着设备上下文或输入上下文中的许多端点上下文数据结构可能未被使用。

(4)作为设备上下文成员,端点上下文数据结构被xHC用来向系统软件报告端点相关参数的当前值。在本文档中,设备上下文的端点上下文数据结构也被称为“输出端点上下文(“Output Endpoint Context”)。

(5)作为输入上下文成员,端点上下文数据结构被系统软件用来将端点相关的命令参数传递给主机控制器。在本文档中,输入上下文的端点上下文数据结构也被称为“输入端点上下文”( “Input Endpoint Context”)。如果引用输入上下文的命令成功,xHC将更新输出端点上下文,以反映它在生成命令完成事件之前积极用于管理端点的参数值。(这里的input和output方向也是相对于主机)

2.2.5 输入上下文

系统软件使用输入上下文数据结构来定义设备配置和状态信息,这些信息将通过地址设备、配置端点或评估上下文命令传递给xHC。它由一个输入控制上下文数据结构、一个slot上下文和1-31个端点上下文数据结构组成。

2.2.6 三种Rings

Command Ring: 用于xHC; (软件 -> xHC)

Event Ring: 用于中断;( xHC -> 软件, 状态和结果)

Transfer Ring: 用于端点或是流;(软件 -> xHC在系统内存缓冲区和设备端点之间移动数据)

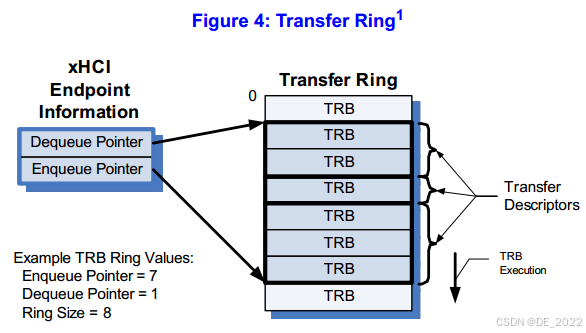

下面是Transfer Ring示意图:

1、USB设备端点之间的传输使用传输描述符(TD)来定义,它由一个或多个传输请求块(trb)组成。

2、TRB中的Chain标志用于标识组成TD的TRB。因此,一个TD指的是传输环上一组连续的TRB数据结构,其中除了TD的最后一个TRB外,所有TRB中都设置了Chain标志。注意,一个TD可以由单个TRB组成,其Chain标志不能设置;

3、“环”是通过在传输环的末尾放置一个特殊的Link TRB来形成的,它将TRB的执行跳回到它的开始

2.2.7 Transfer Request Block(TRB)

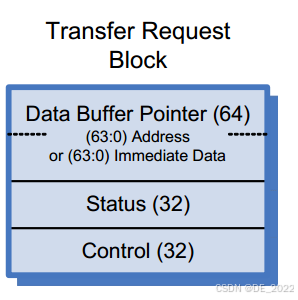

(1)传输请求块(TRB)是一种由软件在内存中构造的数据结构,用于在主机内存和xHC之间传输单个物理上连续的数据块。TRB包含一个数据缓冲区指针、缓冲区的大小和一些额外的控制信息。

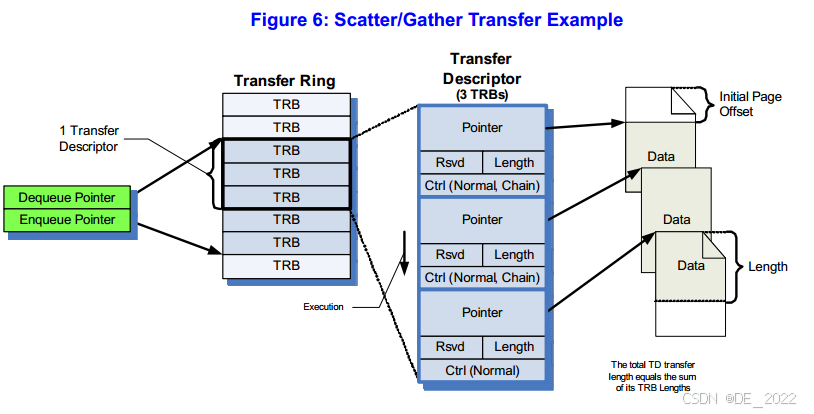

(2)对于大型的多缓冲区操作(例如Scatter/Gather), trb可以被链接起来形成一个复杂的TD。TRB数据结构的小尺寸允许在4K段(内存页)中定义多达256个单独的缓冲区。

(3)系统运行的时间越长,就越难在物理内存中找到连续的页面。如果由于工作负载需求、热插拔事件等的运行时变化,主机需要增加现有传输环的大小或分配多页传输环,则可以使用特殊的Link TRB来扩展环,以包括额外的非物理上连续的段。

(4)TRB的数据缓冲指针字段( Data Buffer Pointer )为数据寻址提供字节粒度。

(5)Length字段位于Status Dword中,用于标识数据缓冲区指针所引用的缓冲区的大小。Length字段可以包含的最大值是64K。当传输Length字节时,xHC将自动访问环中的下一个TRB。确保Length字段与可能遇到的任何页面交叉一致是系统软件的责任。

(6)TRB中的控制双字应该包含一个TRB类型字段,并且可以包含以下一个或多个字段:Chain、Completion中断、Immediate Data、No-Snoop、Interrupt- On Short Packet、Start Isoch ASAP和Frame ID。

2.2.7 Scatter/Gather Transfers

scatter/gather的作用就是将不连续的物理内存在“虚拟”空间进行连续化,Link TRB用指针链接这些不连续的地址。

下图展示三个TRB指向三个不连续的地址段。

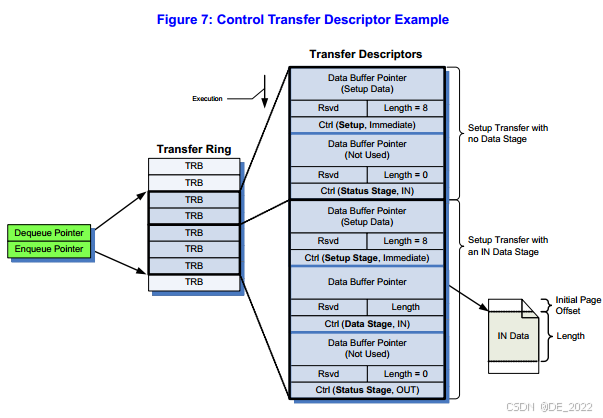

2.2.8 USB transfer传输

控制端点定义了消息管道,其他位流管道。之前的专栏提到USB的控制传输是双向的,具有约束的结构,而Isoch, Interrupt, Bulk端点没有定义USB结构,属于流传输数据。

下图展示有数据阶段和没有数据阶段的控制传输;

Bulk和Interrupt 传输采用普通的TRB,根据数据缓存要求,可以用Link TRB构成TD。

Isoch 传输

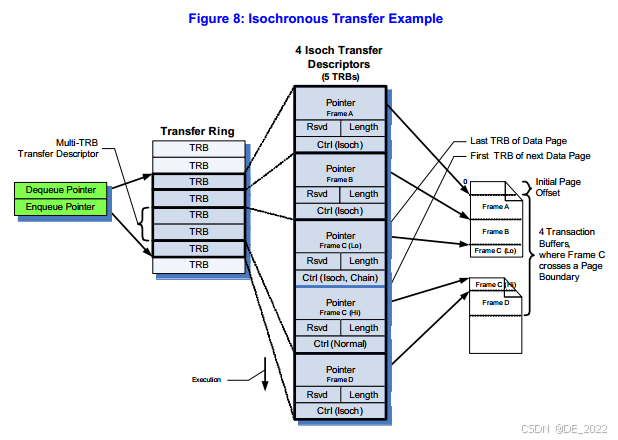

(1)Isoch TD由一个Isoch TRB和零个或多个Normal TRB组成;

(2)Isoch TD的第一个TRB的Control字段中的TRB Type字段设置为Isoch TRB;

(3)每个间隔(由USB端点描述符中的bInterval定义)“消耗”一个Isoch TD;

(4)如果Isoch TD所需的数据在物理上不是连续的(例如,跨越页面边界),则主机应将一个或多个附加的Normal TRB链接到Isoch TRB;

(5)以字节为单位的Isoch传输的大小应限制为 最大数据包大小 x 最大突发大小 x Mult(在端点上下文中定义),或由Isoch TRB和链接到它的所有Normal TRB定义的长度字段的总和。

(6)对于Isoch Out传输,如果达到活动间隔边界时传输环为空,xHC将生成一个环欠运行传输事件。

下图,四个transaction buffer,由5个TRB组成,其中C跨一个Page的边界,被拆分成两个TRB,其中用Chain链接。

2.3 命令接口

Command Ring具有Link TRB机制,Command Ring的工作项为 Command Descriptor , 命令完成产生命令完成事件。

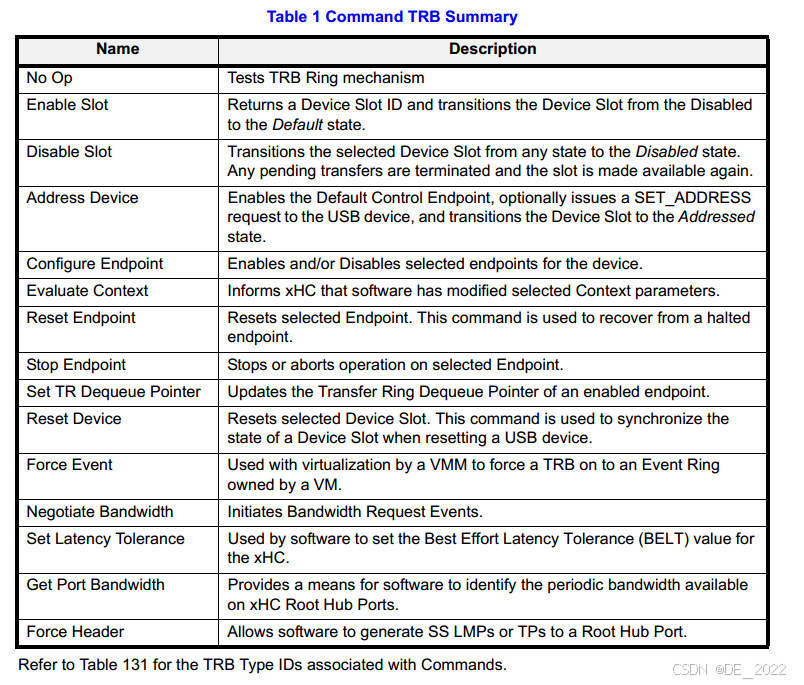

下面是Command TRB的总结

No Op Command可以由软件发出,以在不影响任何xHC或USB设备状态的情况下行使xHC的TRB环机制,或者报告Command Ring Dequeue Pointer的当前值。

Enable Slot命令是软件下发的命令,用于获取可用设备槽位的ID。

Disable Slot命令由软件发出,用于通知xHCI不再需要Device Slot,并且可以释放分配给该Slot的任何资源。

这个xHCI命令替换了通常由系统枚举器在通过xHC枚举USB设备时生成的USB SET_ADDRESS请求,这个xHCI命令替换了通常由系统枚举器在通过xHC枚举USB设备时生成的USB SET_ADDRESS请求。选择分配给USB设备的地址的是xHC,而不是软件。

当系统软件向USB设备发出SET_CONFIGURATION请求时,它启用设备中的一组特定的端点(管道),这些端点(管道)由各自的配置描述符定义。为了简化xHC硬件实现,xHC不从设备读取描述符,也不监控对设备的SET_CONFIGURATION(或SET_INTERFACE)请求。相反,xHC依赖于系统软件来协调xHC中配置的管道与设备中配置的管道。

评估上下文命令是由软件发出的,用于通知xHC应该修改设备上下文中的特定字段。在枚举USB设备的过程中,有几种情况使用不完整的上下文与设备通信。例如,FS设备的默认最大数据包大小为8字节。软件将初始化最大数据包大小字段的默认值控制端点上下文为“8,然后使用端点向设备发出GET_DESCRIPTOR(Device)请求,检索设备描述符的前8个字节。设备描述符的第7字节定义了默认控制端点的实际最大数据包大小。然后使用此命令将默认控制端点的最大数据包大小字段更新为其真实值。该命令将指向输入上下文数据结构的指针传递给xHC。xHC计算输入上下文的特定字段并更新设备上下文。

重置端点命令由软件发出,用于从端点上的停止状态恢复。

停止端点命令由系统软件用于管理传输环。该命令允许软件中止、重定优先级或暂时停止环上td的执行。

Set TR Dequeue Pointer命令是对Stop Endpoint命令的补充,允许软件修改与管道相关的xHC Dequeue Pointer,并在其传输环上重定向td的执行。

Reset Device命令是软件用来通知xHC与设备槽位关联的USB设备已被重置的命令。在所选设备槽位的Slot Context中,复位操作将Slot State字段设置为Default状态,USB device Address字段设置为’ 0 '。复位操作还通过在所有启用的端点上下文中将端点上下文槽位状态字段设置为Disabled来禁用槽位的所有端点,除了默认控制端点。

强制事件命令是xHCI的可选规范命令,仅在启用xHC的虚拟化特性时使用。该命令与其他xHC机制相结合,允许虚拟机管理器(Virtual Machine Manager, VMM)将USB设备模拟到虚拟机。

协商带宽命令是xHCI的可选规范命令,用于恢复系统运行时的USB带宽。

设置延迟容忍度命令可以由软件发出,为xHC提供软件定义的最佳努力延迟容忍度(BELT)值。

获取端口带宽命令由软件发出,用于检索xHC的每个根集线器端口上可用的周期性带宽的百分比。

强制报头命令可以由软件发出,通过选定的根集线器端口向USB设备发送链路管理(LMP)或交易包(TP)。例如,它可以用于发送PING TP或供应商设备测试LMP。

2.4 操作模式

介绍xHCI (eXtensible Host Controller Interface)硬件和xHCD (eXtensible Host Controller Driver)(通常称为系统软件)的通用操作模型。

主机初始化

当系统启动时,枚举主机控制器,为xHC寄存器空间分配一个基址,系统软件将帧长度调整(FLADJ)寄存器设置为系统特定的值;

设备初始化

USB设备的初始化过程是相同的,无论连接到该端口的设备是功能设备还是集线器。一旦设置了与外部集线器相关联的管道,集线器驱动程序将使用标准集线器类命令序列枚举连接到外部集线器端口的设备。本节主要介绍将设备附加到Root Hub端口时的设备初始化过程。

当设备断开时,USB3.0先进入进入Polling状态。Polling成功,端口将进入Enabled状态,并且当前连接状态(CCS)和连接状态变化(CSC)标志设置为“1;

(1)当xHC检测到设备附加时,它应该将当前连接状态(CCS)和连接状态变化(CSC)标志设置为“1”。如果CSC的断言导致Port Status Change Event Generation (PSCEG)从“0”到“1”的转换,xHC将生成Port Status Change Event;

(2)当接收到端口状态变化事件时,系统软件会评估端口ID字段以确定产生该事件的端口。

(3)然后系统软件读取生成事件的端口的PORTSC寄存器。如果事件是由于附加(CCS = ’ 1 ')或分离(CCS = ’ 0 ')造成的,则CSC = ’ 1 ‘。假设事件是由附身造成的:(省略)

(4)端口成功达到Enabled状态后,系统软件通过4.3.2中的Enable Slot命令为新附加的设备获取Device Slot。

(5)成功获取Device Slot后,系统软件将按照4.3.3初始化与该Slot相关的数据结构.

(6)一旦槽位相关的数据结构初始化,系统软件将使用地址设备命令为设备分配地址并启用其默认控制端点。

(7)既然默认控制端点完全可操作,系统软件可以读取完整的USB设备描述符和可能的配置描述符,以便它可以将设备交给适当的类驱动程序。为了读取USB描述符,软件将通过设备的默认控制端点发出USB GET_DESCRIPTOR请求。

(8)在阅读配置描述符后,软件应发出有效位0 (V0)设置为“1”的评估上下文命令,以通知xHC集线器和最大退出延迟参数的值。注意输出槽上下文中断器目标字段的值也可以通过该命令修改。

(9)配置端点命令配置设备插槽,并通过设备的默认控制端点发出USB SET_CONFIGURATION请求来配置USB设备本身。这两个操作的成功完成需要将USB设备的状态从Address推进到Configured, xHC device Slot从addressing推进到Configured。

设备slot初始化

一旦获得了USB设备的xHC设备插槽ID,软件将初始化与该插槽相关的数据结构。以下步骤由系统软件执行:

(1)分配一个Input Context数据结构并将所有字段初始化为’ 0 ‘;

(2)通过设置A0和A1标志为“1”来初始化输入上下文的输入控制上下文。这些标志表明Slot上下文和输入上下文的Endpoint 0上下文受到命令的影响。

(3)初始化输入槽上下文数据结构;

(4)为默认控制端点分配并初始化传输环。TRB环初始化要求请参见第4.9节,TRB环的格式请参见第6.4节。(里面的章节具体见xHCI官方文档)

(5)初始化Input默认控制Endpoint 0上下文

(6)分配输出设备上下文数据结构(6.2.1)并将其初始化为’ 0 '.

(7)用指向输出设备上下文数据结构(6.2.1)的指针在设备上下文基址数组(5.4.6)中加载适当的(设备槽位ID)条目。

(8)为设备插槽发出一个地址设备命令,该命令指向上述输入上下文数据结构。

设备地址分配,设备配置,配置备用接口,低速/全速设备支持,带宽管理

设备分离

当设备从根集线器端口分离时,PORTSC当前连接状态(CCS)位应清除为“0”,连接状态变化(CSC)位应设置为“1”。如果PSCEG的“0”到“1”转换,xHC应通过端口状态更改事件报告更改。检测到分离后,系统软件应通过对受影响的槽位发出disable Slot命令来禁用与该端口关联的Device Slot。

设备槽位管理

xHCI最多支持255个USB设备,其中每个USB设备被分配到一个设备插槽。每个xHC设备插槽由3个主要组件组成:设备上下文基地址数组中的一个条目,设备上下文数据结构,以及门铃数组中的一个门铃寄存器。

下面是Device Context示意图,由31个Endpoint Context和1个slot context

每个设备槽位的门铃阵列中都存在一个32位的门铃寄存器,并根据槽位ID进行索引。

门铃寄存器中的DB Target和DB Stream ID字段表示“摇响”门铃的目的。

使用DB Target = Host Controller Command按响主机控制器门铃(门铃寄存器0),向xHC表明软件已经在命令环中定义了它想要执行的命令。

术语设备上下文索引(DCI)在本文档中用于引用设备上下文中的单个上下文数据结构。DCI取值范围为0 ~ 31。

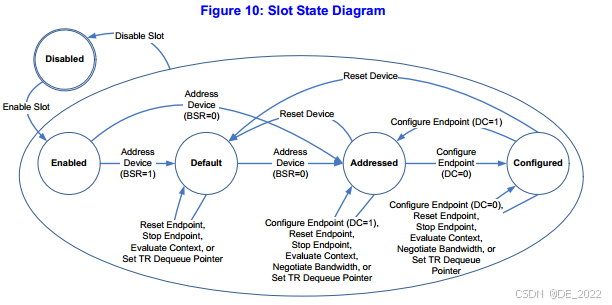

下面是USB的slot状态机示意图

命令接口

xHC的命令接口通过命令环控制寄存器(CRCR)进行管理。

Command Ring是一个专用的TRB Ring,它只允许表131中定义的TRB类型。每个xHC实例只存在一个命令环。

系统软件是所有命令trb的生产者,xHC是消费者。

Command Ring Dequeue Pointer 是由xHC维护的内部寄存器,它不直接暴露给软件。它的值在命令完成事件的命令TRB指针字段中报告。

命令环上的工作项称为命令描述符(CD),CD应由一个命令TRB数据结构组成。

软件通过以下方式向xHC发出命令:1)在命令环上放置一个或多个命令描述符,2)按主控制器门铃。

系统软件可以通过向命令环控制寄存器的命令停止(CS)位写入“1”来停止命令环上的命令执行。在CS位上写一个“1”将阻止xHC在当前执行的命令完成后获取额外的cd,“停止”命令环。命令环停止成功后,将生成一个命令完成事件,完成码设置为命令环停止,命令TRB指针设置为命令环退出队列指针的当前值。

当命令环停止时,环上所有命令描述符的所有权被传递给软件,软件可以删除、添加或重新排列命令描述符。软件通过写入主机控制器门铃寄存器并将DB Reason字段设置为主机控制器命令来重新启动命令执行。如果命令环控制寄存器(CRCR)的命令环指针字段在环停止时被写入,xHC将在CRCR写入定义的新值重新启动命令环执行,否则命令环执行将在当前的Dequeue Pointer值重新启动,即最后一个命令执行(或终止)后的TRB。软件可以通过在命令环控制寄存器的命令环指针字段中写入一个新值来修改命令环退出队列指针的值,然后重新启动它。

中止命令:系统软件可以通过向命令环控制寄存器的命令中止(CA)位写入一个“1”来中止当前命令的执行。应为已终止的命令生成命令完成事件,其完成代码设置为命令终止。

No Op:空操作;

Enable Slot:Enable Slot命令是软件下发的命令,用于获取可用的Device Slot,并将Device Slot从Disabled状态转换为Enabled状态。

Disable Slot:Disable Slot命令是软件下发的命令,用于强制Device Slot进入Disabled状态。典型的用法是在USB设备断开连接时释放设备插槽。

Address Device:地址设备命令由软件发出,根据块集地址请求(BSR)标志的状态,将设备插槽从默认状态转换为默认状态或已寻址状态。

Configure Endpoint:配置端点命令由软件发出,用于启用、禁用或重新配置与目标配置相关联的端点。配置设备。为了在设备中设置配置,软件应向xHC发出配置端点命令,同时向设备发出USB SET_CONFIGURATION请求。USB设备通过向选择配置’ 0 '的USB设备发出SET_CONFIGURATION请求来“解除配置”。

待补充…

3、UTMI接口协议

3.1 架构介绍

UTMI全称为USB 2.0 Transceiver Macrocell Interface

USB外设ASIC的三个主要功能块,包括收发器微单元,串行接口逻辑,设备特定逻辑块。

收发器微单元,处理数据的正反序,位填充和时钟恢复同步。它支持HS(480Mbit/s)和FS(12Mbit/s), LS(1.5Mbit/s)三种传输速率,一般是8/16bit的数据,支持SYNC/EOP的产生与检查,从串行数据中恢复数据和时钟等等。USB2.0可以用SuspendM置于低功耗模式。

SIE模块包括SIE控制逻辑和端点逻辑。SIE控制逻辑主要是用于USB PID和地址识别,以及出力USB数据包和事务的排序和状态机跳转。端点逻辑实现端点编号识别,FIFO控制。

设备特定逻辑是将USB接口连接到设备特定应用程序。

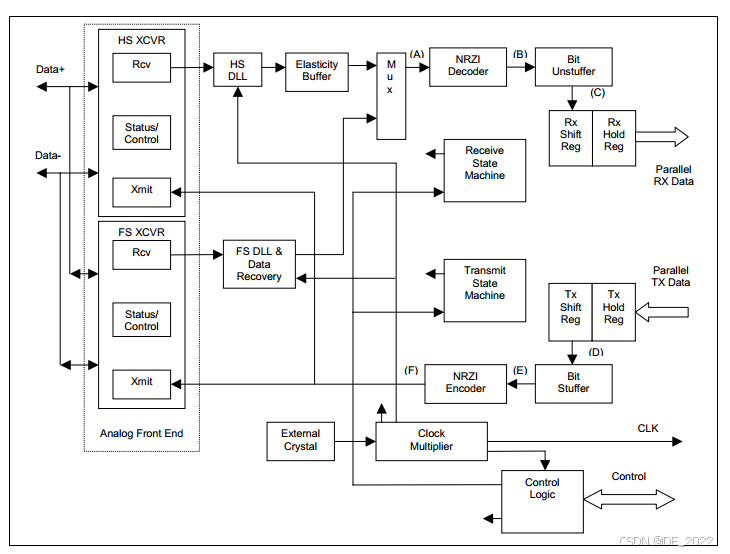

下面是UTM功能模块的示意图,可以看到差分线送入到HS或是FS中,从dp/dm中提取出数据信号和时钟信号。弹性buffer用于消除频差,可能一开始模块两侧的速率不一致。USB2.0协议用的是NRZI编码,USB3.0就换成8B/10B编码,目的是做直流平衡。此外内部有接收和发送的状态,控制数据的收发。里面还有保持寄存器。从外部端口看,是将差分信号转换为8bit的data信号,或是8bit的data信号转换为差分信号。

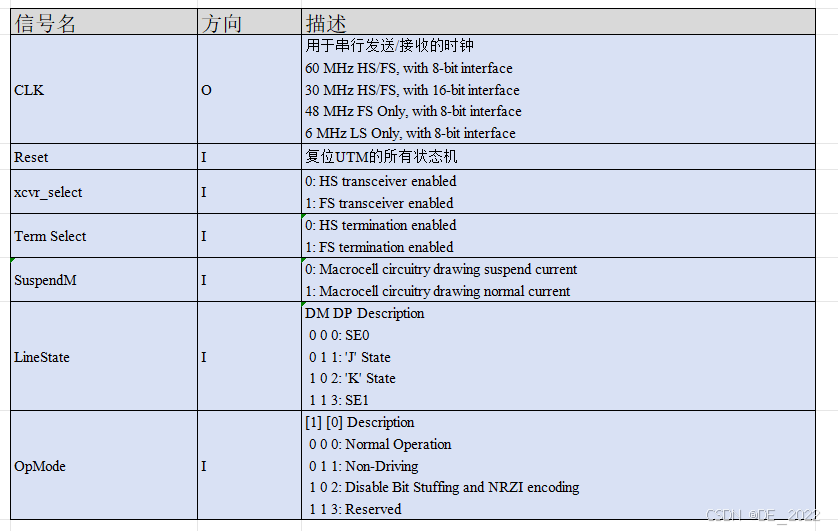

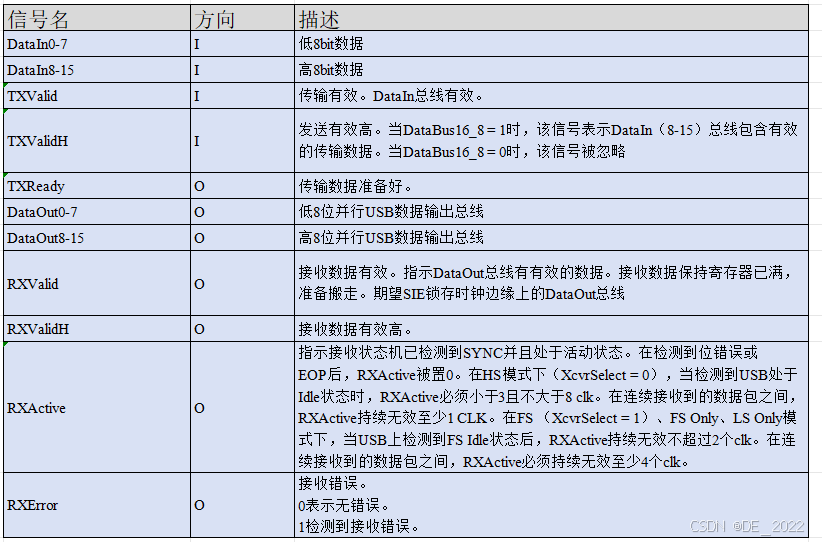

3.2 接口信号描述

下面是UTMI的系统接口信号的含义

Reset是复位内部的状态机,SuspendM控制挂起,注意挂起时Term_Select必须是FS状态,linestate指示dp/dm状态。

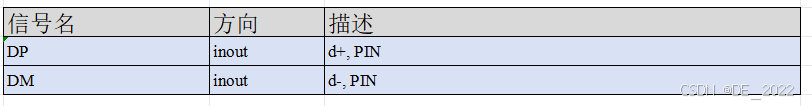

下面是usb接口信号

这是USB2.0的接口信号,要送出PAD。

下面是数据接口信号

3.3 UTMI时序

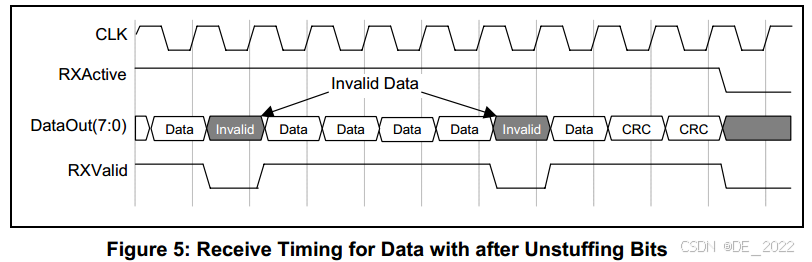

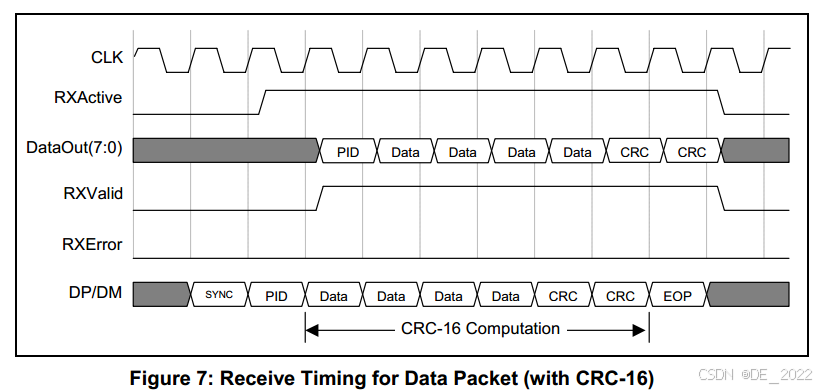

下面是相关时序,因为时钟存在波动,所以会有弹性buffer缓存发送和接受时钟的差异性,即插入无有的SKP序列,而RXError指示Buffer是上溢还是下溢。XcvrSelect决定HS还是FS模式。USB采用的是NRZI编码,解码时会去除填充的0,因为不允许出现7个连续1。如果检测到了违背了NRZI编码规则,会产生EOP信号,RXActive也会拉低。

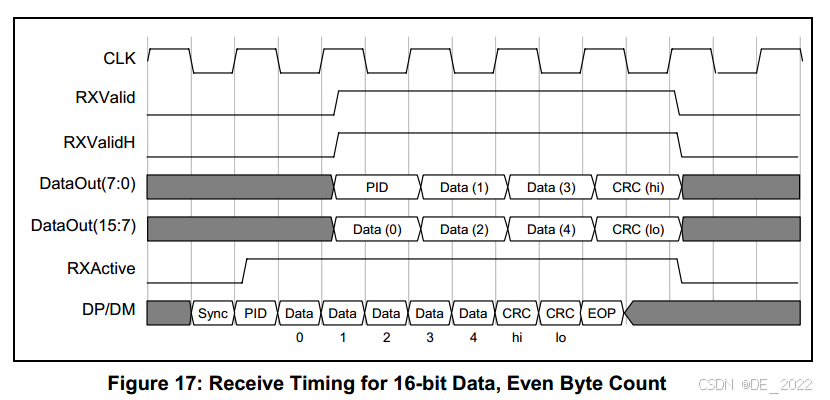

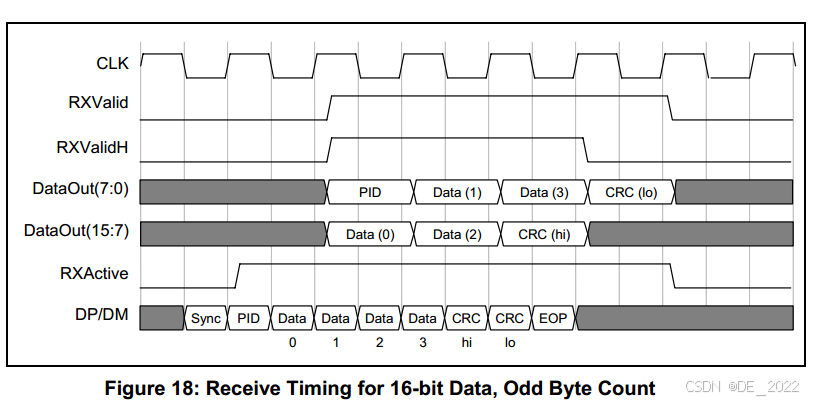

RXActive和RXValid同时拉高说明收到的数据才有效。

数据包会带有16bit的CRC,而令牌包会带有5bit的CRC,握手包不带有CRC。可以看到UTMI接口不会发送SYNC和EOP。

如果收到RXError将终止接收,等待下一个的SYNC。出现RXError的原因有几种(1)错误的位填充,(2)弹性buffer上溢或是下溢,(3)EOP没有对齐,不是一个字节的边界,(3)DLL的sync丢失,(4)供应商特定错误;

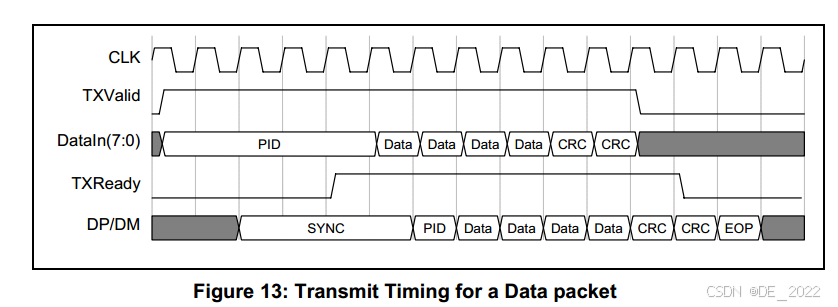

同样的,TXValid和TXReady都拉高1个clk表示传输一个有效字节。TXValid一旦拉低表示一个包传输完成。OpMode有三种模式(1)正常驱动(有编码解码操作),(2)非驱动(支持设备断开),(3)禁止NRZI,

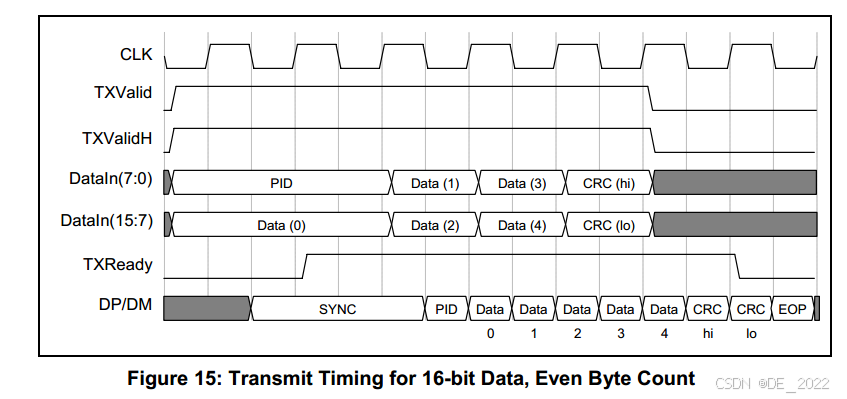

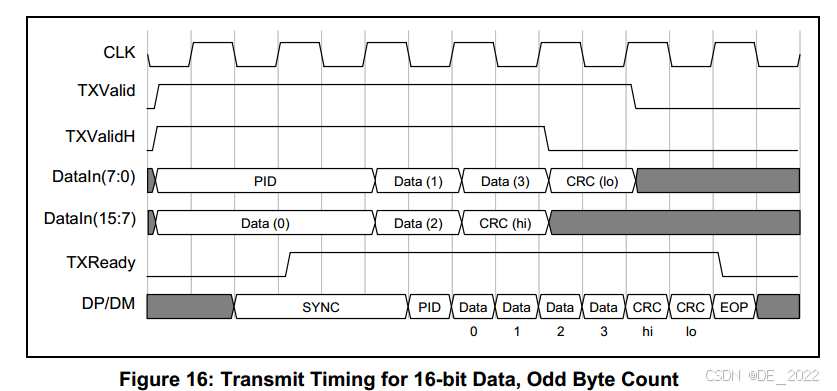

下面是传输16bit位宽数据的时序图,crc-hi/lo实际放在高低DataIn-8bit后面

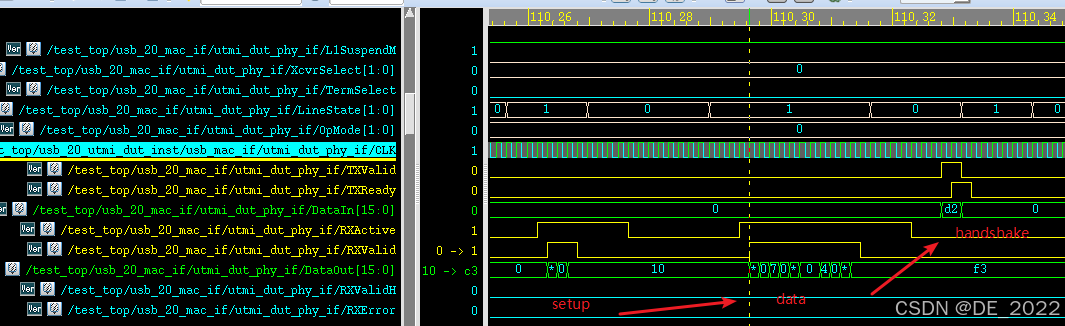

下面是UTMI_VIP的波形展示,根据usb2.0的协议,主机先发送setup包,再发送data数据包,最后接收到从机的ack包。根据usb协议的PID类型,setup包的第一个数据0x2d代表setup,地址为0,crc5为0x10。data包的第一个数据0xc3表示data0,crc16为0x77f3, handshake包的第一个数据为0xd2,表示ack包。

4、PIPE接口协议

4.1 介绍

PIPE接口支持PCIE,SATA,USB,DisplayPort和融合IO PHY的开发。

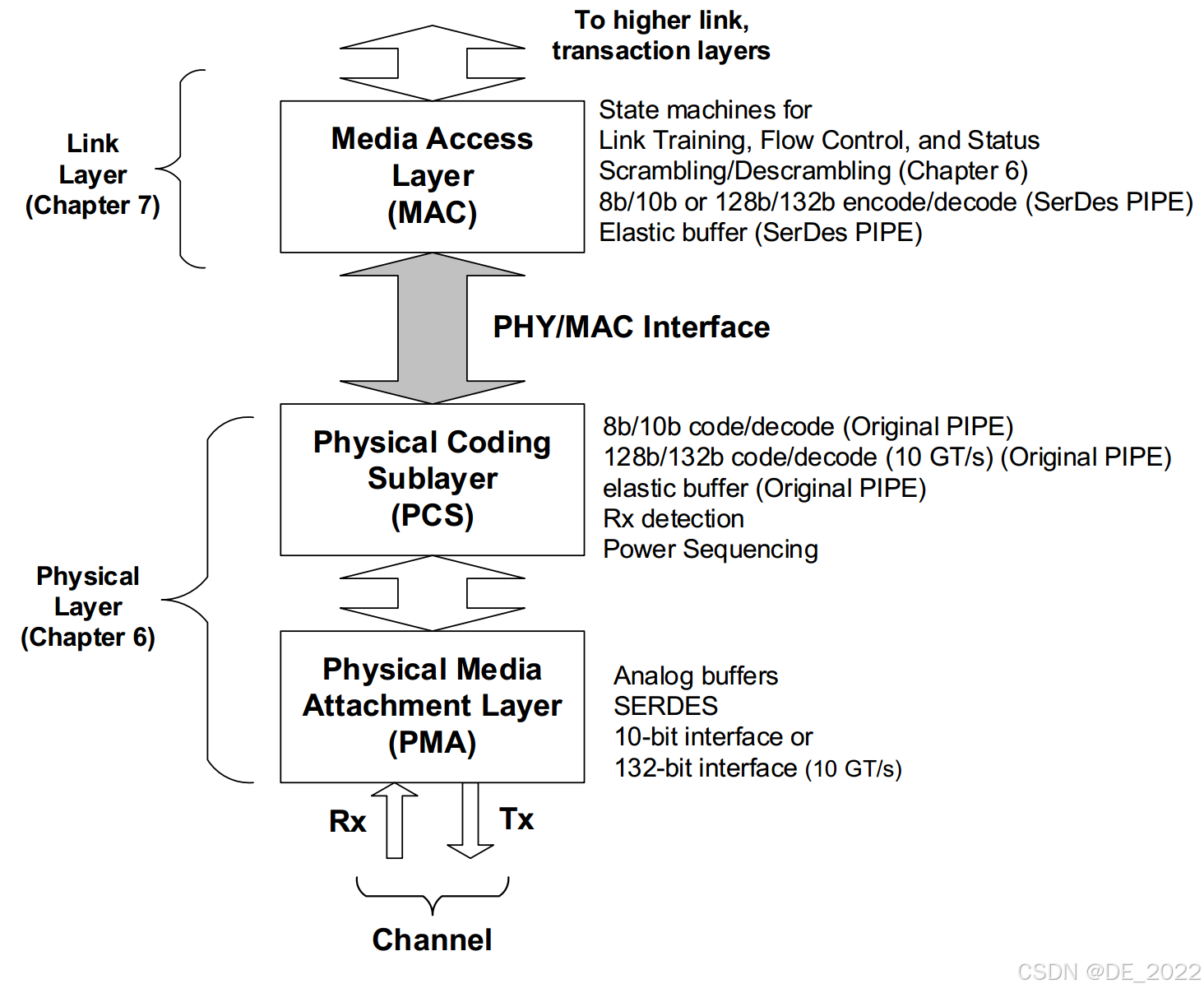

下面是USB的PHY的划分,链路层负责内部状态机ltssm,加扰和去扰,编码和解码以及流控。物理层又分成物理编码子层PCS和物理媒介附层PMA,PMA接收并发送串行lane上的高速串行数据。PCS则充当PMA和控制器之间的接口,执行数据编码和解码、弹性buffer和RX检测等功能。

USB PHY的一些关键特性是:

•标准PHY接口支持USB链路层的多个IP源,并为USB PHY供应商提供目标接口。

•支持5.0 GT/s和/或10GT/s串行数据传输速率

•采用8位,16位或32位并行接口传输和接收USB数据

•允许将高速组件集成到单个功能块中

•USB总线上串行流的数据和时钟恢复

•保持寄存器以阶段发送和接收数据

•8b/10b编码/解码和错误指示

•128b/132b编码/解码和错误指示

•接收器检测

•低频周期性信号(LFPS)

4.2 USB3 PHY架构

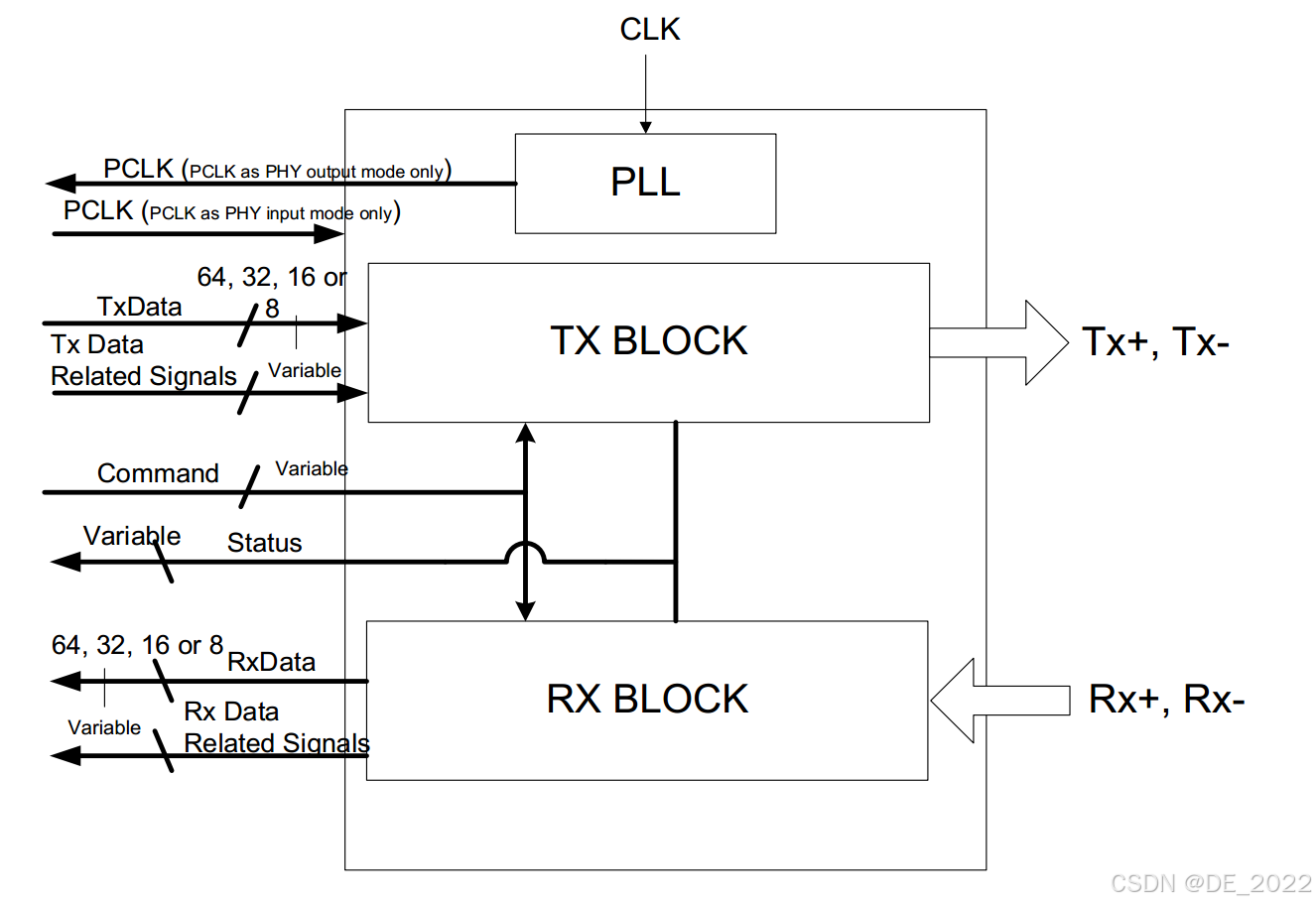

PHY总体功能架构

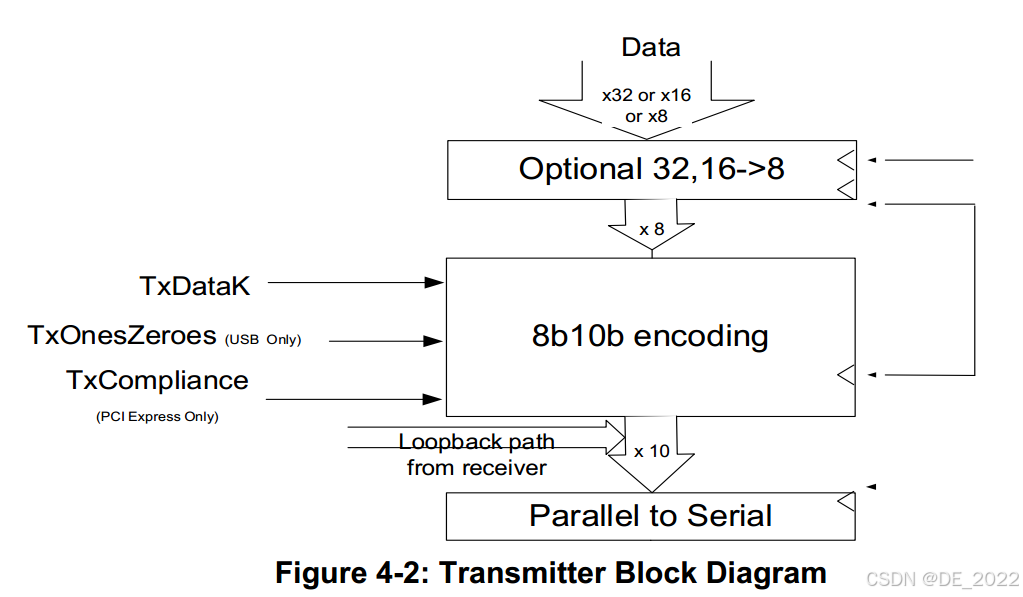

发送模块框图

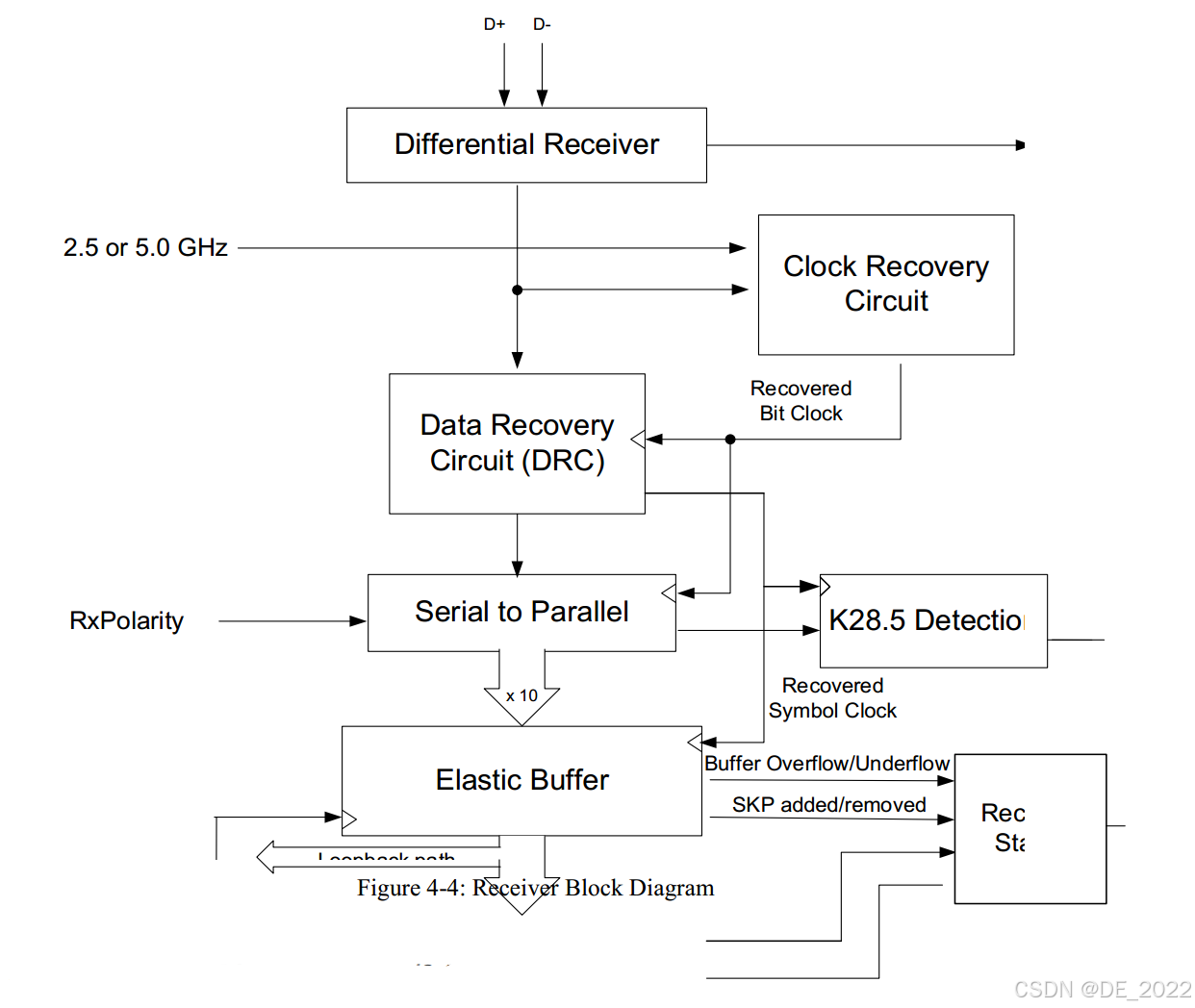

接收模块框图

K28.5是开始的检测位

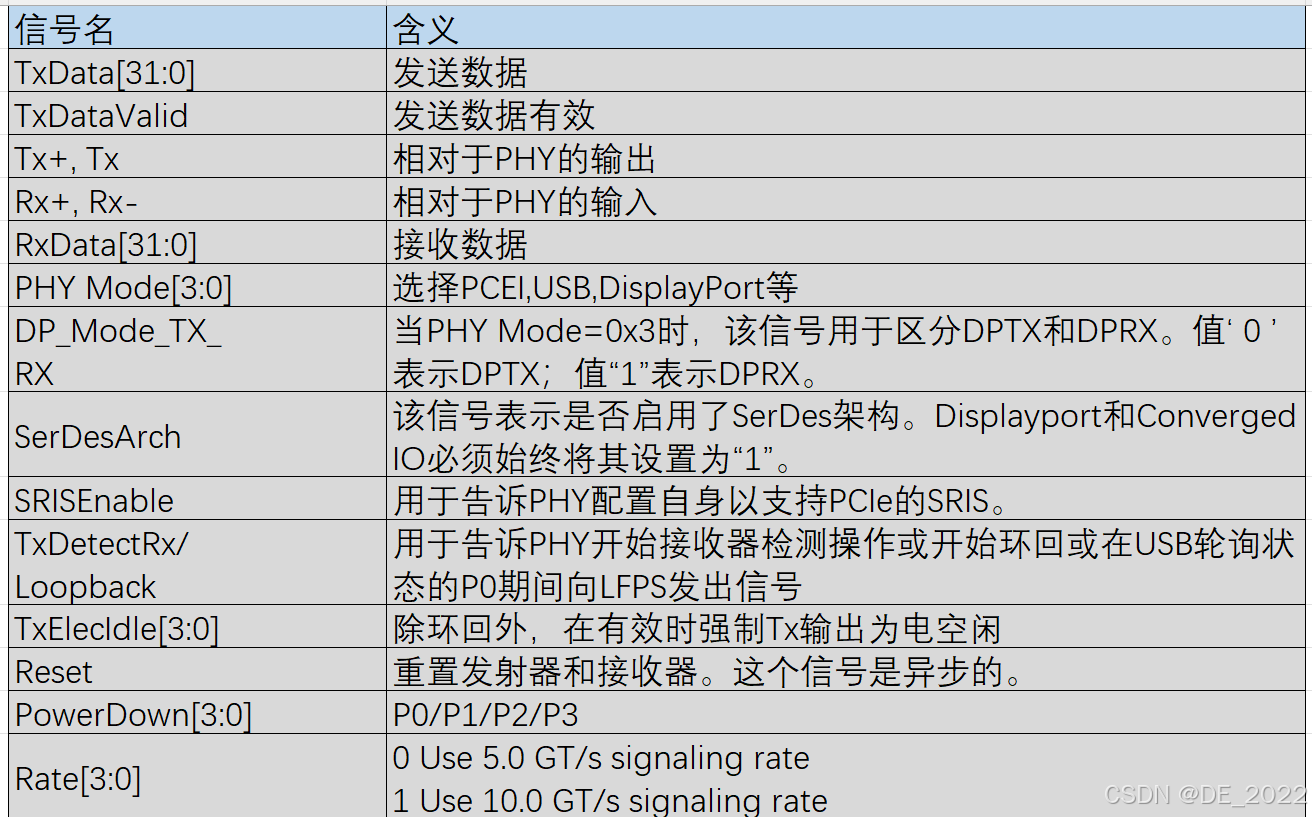

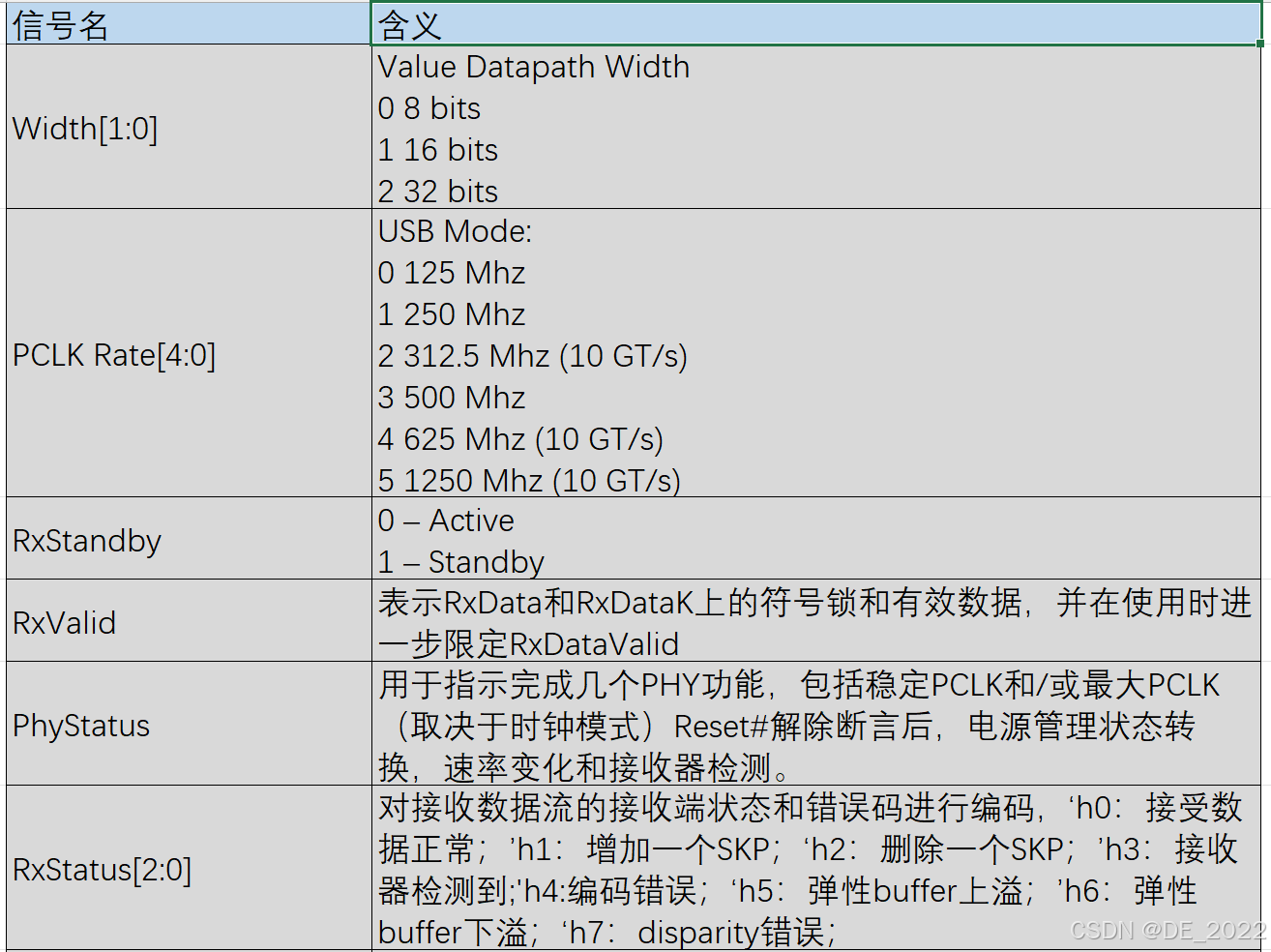

4.3 PIPE接口信号

2995

2995

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?