1.累加器模块的作用

累加器用于存放当前的结果。它也是双目运算中的一个数据来源。

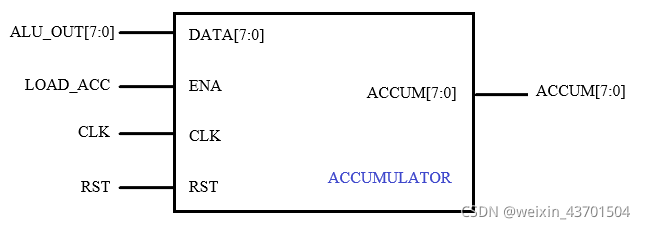

2.模块端口图

3.端口功能描述

复位后,累加器的值是0。当累加器通过ENA端口收到来自CPU状态控制器LOAD_ACC信号时,在clk上升沿触发时就收到来自数据总线的数据。

4.Verilog代码

module accum (

clk ,

rst ,

ena ,

data ,

accum

);

input clk, rst ;

input ena ;

input [7: 0] data ;

output reg [7: 0] accum ;

// accum control

always @( posedge clk ) begin

if ( rst )

accum <= 8'b0;

else

if ( ena )

accum <= data;

end

endmoduletestbench:

`timescale 1ns / 1ps

//

// test reset and enable functions

//

module accum_tb();

reg clk, rst ;

reg ena ;

reg [7: 0] data ;

wire [7: 0] accum ;

accum u3(

.clk ( clk ),

.rst ( rst ),

.ena ( ena ),

.data ( data ),

.accum ( accum )

);

initial clk = 0;

always #10 clk = ~clk;

initial begin

rst = 1;

ena = 1;

data = 8'b1010_0101;

#201;

rst = 0;

#20;

data = 8'b1010_0110;

#20;

data = 8'b1010_0111;

// disable the ena

#20;

ena = 0;

data = 8'b1010_0101;

#100;

rst = 1;

#20;

rst = 0;

ena = 1;

#10000;

end

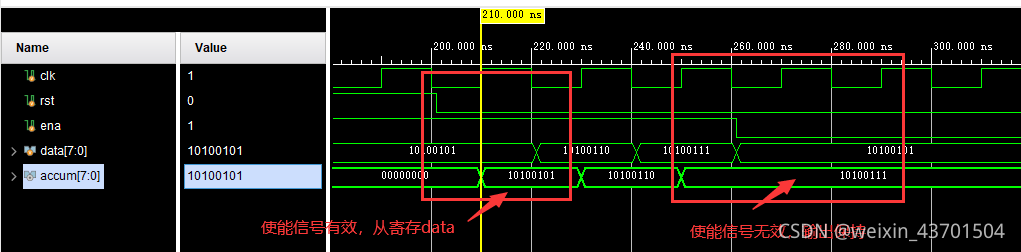

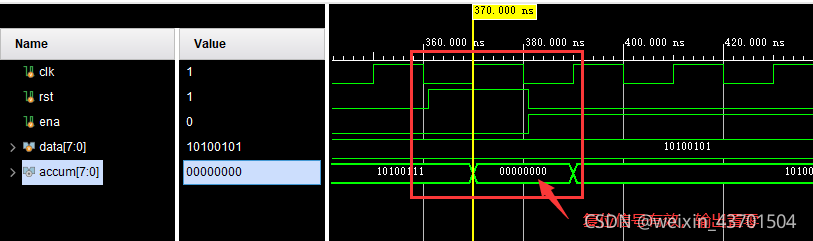

endmodule5.仿真图

本文详细介绍了Verilog语言实现累加器的过程,包括累加器的功能描述、模块端口图、Verilog代码实现以及仿真图。在复位后,累加器初始值为0,当接收到LOAD_ACC信号时,累加器在时钟上升沿更新其值。通过提供的testbench验证了累加器的复位和使能功能。

本文详细介绍了Verilog语言实现累加器的过程,包括累加器的功能描述、模块端口图、Verilog代码实现以及仿真图。在复位后,累加器初始值为0,当接收到LOAD_ACC信号时,累加器在时钟上升沿更新其值。通过提供的testbench验证了累加器的复位和使能功能。

5902

5902

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?