1.指令寄存器模块的作用

顾名思义,指令寄存器用于寄存指令。

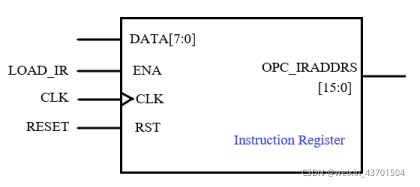

2.模块端口图

3.端口功能描述

指令寄存器的触发时钟是clk,在时钟上升沿的触发下,寄存器将数据总线送来的指令存入低8位或高8位寄存器中。但并不是每个clk的上升沿都寄存数据总线的数据,因为数据总线上有时传输指令,有时传输数据。什么时候寄存,什么时候不寄存,由CPU状态控制器的LOAD_IR信号控制。LOAD_IR信号通过ENA端口输入到指令寄存器,复位后,指令寄存器被清零。

每条指令分为两个字节,即16位。高3位是操作码,低13位是地址(CPU的地址总线为13位,寻址空间为8K字节)。本设计的数据总线为8位,所以每条指令需要取两次。先取高8位,后取低8位。而当前取的是高8位还是低8位,由变量state记录。state为0表示取的是高8位,存入高8位寄存器OPC_IRADDRS[15:8],同时将变量state置为1。下次再进行寄存时,由state为1,可知取的是低8位,存入低8位寄存器中。

4.Verilog代码

module inst_reg (

clk ,

rst ,

ena ,

data ,

opc_iraddrs

);

input clk, rst ;

input ena ;

input [ 7: 0] data ;

output reg [15: 0] opc_iraddrs ;

reg state ;

// always block 1: state control

always @( posedge clk ) begin

if ( rst )

state <= 1'b0;

else begin

if ( ena ) begin

case ( state )

1'b0:

state <= 1'b1;

1'b1:

state <= 1'b0;

default:

state <= 1'b0;

endcase

end

else

state <= 1'b0; // not reset, not ena

end

end

// always block 2: output control

always @( posedge clk ) begin

if ( rst )

opc_iraddrs <= 16'b0;

else begin

if ( ena ) begin

case ( state )

1'b0:

opc_iraddrs[15: 8] <= data;

1'b1:

opc_iraddrs[ 7: 0] <= data;

default:

opc_iraddrs[15: 0] <= 16'bxxxxxxxxxxxxxxxx;

endcase

end

end

end

endmodule

testbench:

`timescale 1ns / 1ps

//

// testbench: First, set all data values to 1

// as the high 8 bits and all 0 as the low 8 bits,

// then, set all data values to 0 as the high 8 bits

// and all 1 as the low 8 bits,

// and observe whether the output value is correct

//

module inst_reg_tb();

reg clk, rst, ena ;

reg [7: 0] data ;

wire [15:0] opc_iraddr ;

inst_reg u2(

.clk ( clk ),

.rst ( rst ),

.ena ( ena ),

.data ( data ),

.opc_iraddrs ( opc_iraddr )

);

initial clk = 0;

always #10 clk = ~clk;

initial begin

rst = 1;

ena = 1;

data = 8'b11111111;

#201;

rst = 0;

#20;

data = 8'b0;

#20;

data = 8'b0;

#20;

data = 8'b11111111;

#20;

// reset function check

rst = 1;

data = 8'b11111111;

#20;

data = 8'b0;

#20;

data = 8'b11111111;

#20;

data = 8'b0;

#20;

// enable function check

rst = 0;

#20;

data = 8'b11111111;

#20;

data = 8'b0;

#20;

ena = 0;

data = 8'b11111111;

#20;

data = 8'b0;

#20;

data = 8'b11111111;

#20;

data = 8'b0;

end

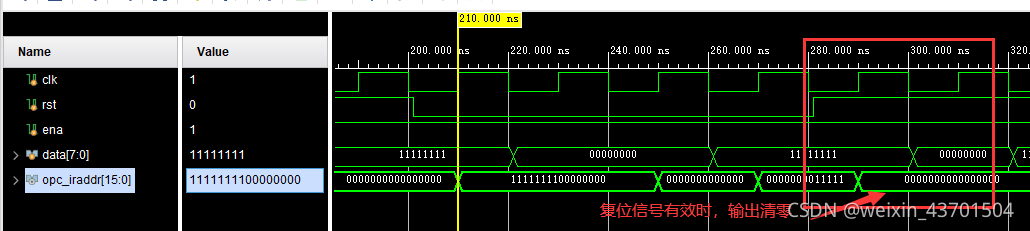

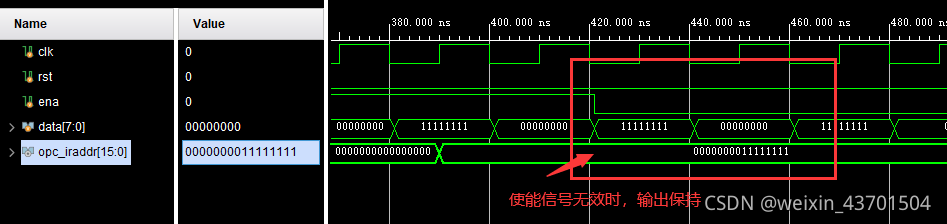

endmodule仿真图:

本文介绍了指令寄存器模块的功能,该模块在时钟上升沿并在LOAD_IR信号控制下存储数据总线上的指令。每条指令由16位组成,包括3位操作码和13位地址。设计中使用了两个8位寄存器分别存储高8位和低8位。Verilog代码展示了如何实现这个功能,并提供了测试激励来验证模块的正确工作。测试过程中,首先设置高8位为1,低8位为0,然后切换高、低8位的数据,最后进行了重置和使能功能的检查。

本文介绍了指令寄存器模块的功能,该模块在时钟上升沿并在LOAD_IR信号控制下存储数据总线上的指令。每条指令由16位组成,包括3位操作码和13位地址。设计中使用了两个8位寄存器分别存储高8位和低8位。Verilog代码展示了如何实现这个功能,并提供了测试激励来验证模块的正确工作。测试过程中,首先设置高8位为1,低8位为0,然后切换高、低8位的数据,最后进行了重置和使能功能的检查。

2768

2768

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?