Verilog 1995 允许在节选范围的索引为常数时从一个向量中节选连续的比特。Verilog 2001,2005 提供了两个新的节选运算符来支持固定宽度的变量节选:+:和 -:,其语法分别为:

[ < starting_bit > +: < width > ] 和 [ < starting_bit > -: < width > ]

参数 width 指的是节选部分的长度, starting_bit 则指明了向量中被选部分是取最左边位还是最右边位,这取决于向量的节选是按递增位索引进行,还是按递减位索引进行。

如下例:

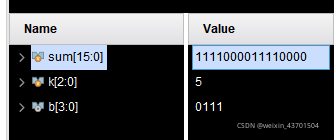

reg [15: 0] sum ;

reg [ 2: 0] k ;

wire [3: 0] b = sum[k +: 3];

表示 b 取的是从sum中的第k位起,往左取到到第k+3位。

若 sum = 16'b1111_0000_1111_0000;

k = 3'b101;(5)

则b的结果为sum[8: 5],即b = 4‘b0111

需要注意的是,“+:”的右边必须是一个常数,不能是表达式或者变量。

而如果是 [ < starting_bit > -: < width > ],中间是“-:”,则表示从starting_bit位开始,往右边取 width位。

如:

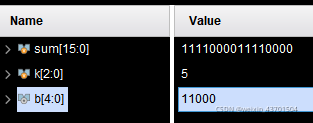

reg [15: 0] sum;

reg [2: 0] k;

wire [4: 0] b = sum[k -: 5];表示从sum的第k位起,往右取5位。

若 k=5,sum = 16'b1111_0000_1111_0000;

则b=sum[5]开始,往右再取5位,结果为:11000

本文介绍了Verilog语言中用于向量节选的两种新运算符:+:和-:,详细解释了它们的用法和区别。+:运算符用于从指定位置开始向左取固定宽度的位,而-:运算符则是从指定位置开始向右取位。通过举例说明了这两个运算符在不同情况下的应用,并给出了具体的计算结果。

本文介绍了Verilog语言中用于向量节选的两种新运算符:+:和-:,详细解释了它们的用法和区别。+:运算符用于从指定位置开始向左取固定宽度的位,而-:运算符则是从指定位置开始向右取位。通过举例说明了这两个运算符在不同情况下的应用,并给出了具体的计算结果。

529

529

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?