串行数据检测,就是输入一段数据,如有检测到特定的比特流,则输出1表示检测到特定序列。比如下文的示例代码,就是当检测到连续3个或以上的1时,输出端输出1。采用状态机的方式设计较为简单,当输入为1时,跳转到下一个状态。当在s2或s3状态时若输入仍为1,则表示出现连续3个或以上的1比特流,此时输出1。当需要检测其他比特流时例如101,改变状态跳转调节即可。笔试中这种题很常见。

Library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity Serial is

port(x,cp:in std_logic;

y:out std_logic );

end Serial;

architecture w of Serial is

type state is (s0,s1,s2,s3);

signal p: state;

signal n: state;

begin

process(cp)

begin

if cp' event and cp='1' then

p<=n;

end if;

end process;

process(x,p)

begin

case p is

when s0=> if x='1' then

n<=s1;

else

n<=s0;

end if;

y<='0';

when s1=> if x='1' then

n<=s2;

else

n<=s0;

end if;

y<='0';

when s2=> if x='1' then

n<=s3;

y<='1';

else

n<=s0;

y<='0';

end if;

when s3=> if x='1' then

n<=s3;

y<='1';

else

n<=s0;

y<='0';

end if;

when others=>null;

end case;

end process;

end w;

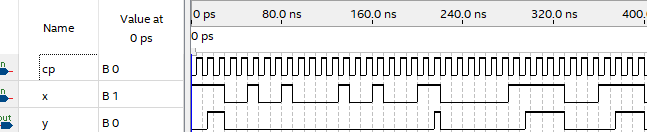

下图为波形仿真结果

7681

7681

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?