主存储器

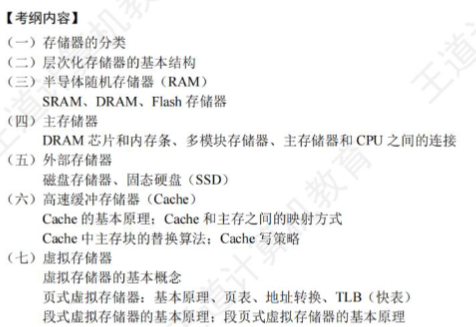

存储器芯片的组成

- 片选线头上的横线表示该信号低电平有效

- 关于总容量的描述除了利用公式总容量=存储单元个数 * 存储字长,还会常见描述 8 K ∗ 8 位 8K*8位 8K∗8位 位的存储芯片,即 2 13 ∗ 8 b i t 2^{13}*8bit 213∗8bit; 8 K ∗ 1 位,即 2 13 ∗ 1 b i t 8K*1位,即2^{13}*1bit 8K∗1位,即213∗1bit; 64 K ∗ 16 位,即 2 16 ∗ 16 b i t 64K*16位,即2^{16}*16bit 64K∗16位,即216∗16bit,第一个数字表示有多少个存储单元,第二个数字表示存储字长为多少

- 总容量为 1KB,①按字节寻址:1K 个单元可表示 10 根地址线,每个单元 1B;②按字寻址:256 个单元,每个单元 4B;③按半字寻址:512 个单元,每个单元 2B;④按双字寻址:128 个单元,每个单元 8B

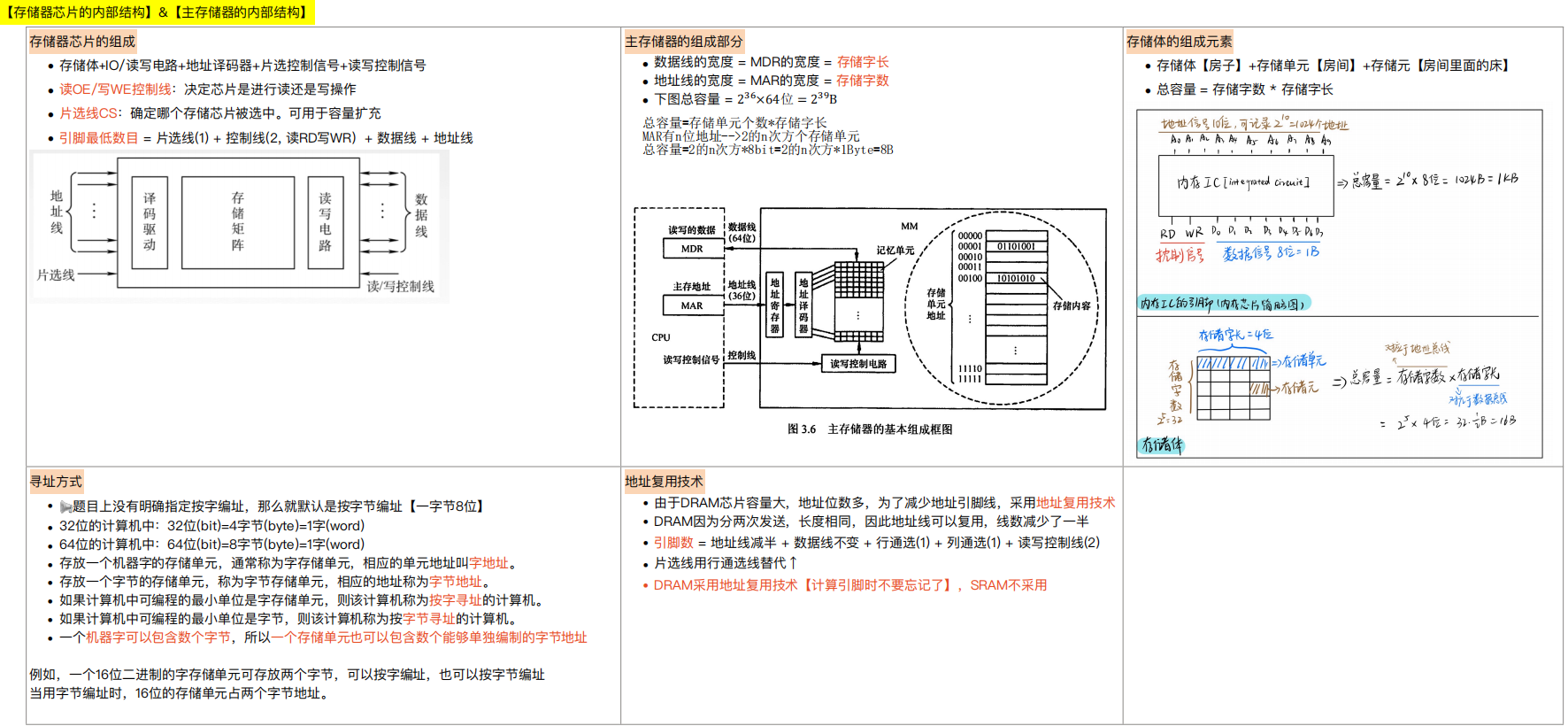

地址复用技术

- DRAM 采用地址线复用技术,可以使地址线、地址引脚减半

主存储器的组成部分

- 由一个个存储 0 或 1 的记忆单元(也称存储元件)构成的存储矩阵(也称存储体)是存储器的核心部件

- 存储元件是具有两种隐态的能表示二进制 0 和 1 的物理器件

- 为了存取存储体中的信息,必须对存储单元编号(也称编址)。

- 编址单元是指具有相同地址的那些存储元件构成的一个单位,可以按字节编址,也可以按字编址

- 现代计算机通常采用字节编址方式

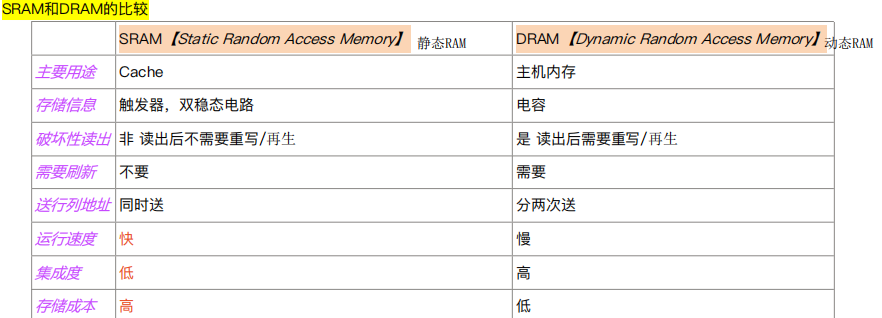

- SRAM 和 DRAM 都是易失

- SRAM: 静态 RAM

- DRAM:动态 RAM

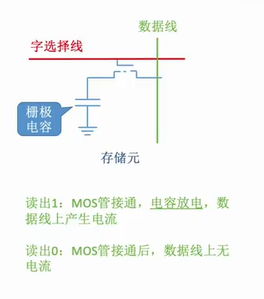

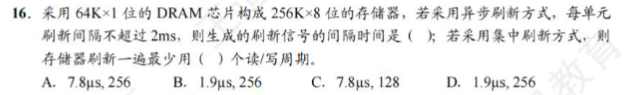

- DRAM 的存储信息电容,读出 1:MOS 管接通,电容放电,数据线上产生电流;读出电容 0:MOS 管接通后,数据线上无电流;②读出数据线只有 1 根;③电容内的电荷只能维持 2ms,即便不断电,2ms 后信息也会消失,需要刷新操作

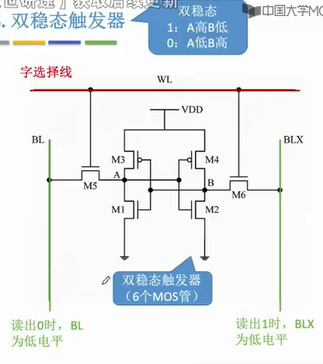

- SRAM 的存储信息双稳态触发器(6 个 MOS 管),②双稳态:(1:A 高 B 低,0:A 低 B 高),只要不断电,触发器的状态就不会改变,保存的 0 和 1 就不会小时,③读出数据线有 2 根

- 破坏性读出,读出后应有重写操作,也称再生

- SRAM 和 DRAM 均为易失性存储器(断电后信息消失)

- DRAM 的刷新是由存储器独立完成,不需要 CPU 控制

- 主存芯片 DRAM 已经过时,现在的主存通常采用 SDRAM 芯片

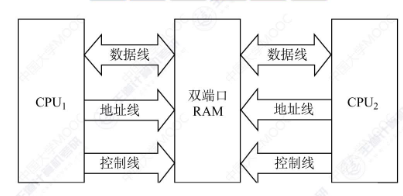

双端口 RAM(408 不考,自命题考)

- 作用:优化多核 CPU 访问一根内存条的速度

- 支持双端口 RAM 需要有两组完全独立的数据线、地址线、控制线。CPU、RAM 中也要有更复杂的控制电路

- 两个端口对同一主存操作有以下 4 种情况:

-

- 两个端口同时对不同的地址单元存取数据 😀

-

- 两个端口同时对同一地址单元读出数据 😀

-

- 两个端口同时对同一地址单元写入数据 会发生写入错误

-

- 两个端口同时对同一地址单元,一个写入数据,另一个读出数据 会发生读出错误

-

针对错误的解决办法:

置“忙”信号为 0,由判断逻辑决定暂时关闭一个端口(即被延时),未被关闭的端口正常访问,被关闭的端口延长一个很短的时间段后再访问

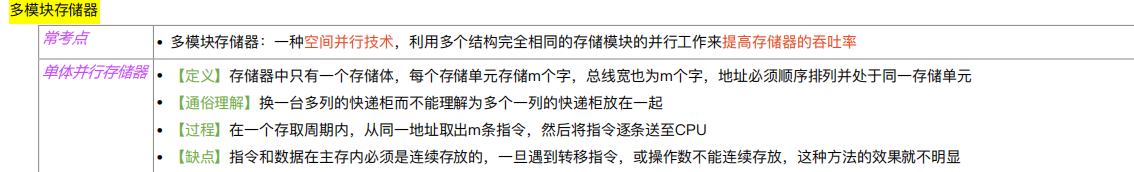

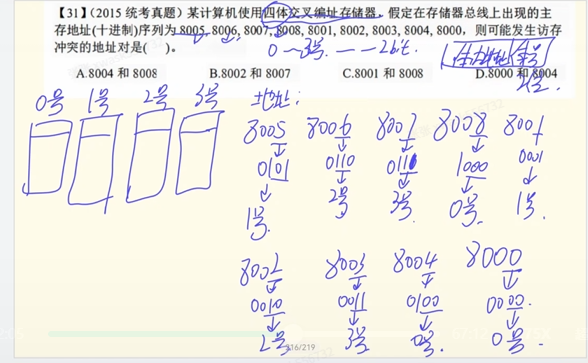

多模块存储器

小结

- 📕存取周期 T=存取时间 r+恢复时间

- 双端口 RAM

- 支持两个 CPU 同时访问 RAM

- 可同时读/写不同的存储单元;可同时读同一个存储单元;不能同时写(或者一读一写)同一个单元

- 若发生“冲突”,则发生“BUSY”信号,其中一个 CPU 的访问端口暂时关闭

- 多模块存储器

- 单体多字存储器

- 每次并行读出 m 个连续的字

- 总线宽度也要扩展为 m 个字

- 多体并行存储器

- 高位交叉编址:理论上多个存储体可以被并行访问,但是由于通常会连续访问,因此实际效果相当于单纯的扩容

- 📕低位交叉编址:①当存储模块数 m≥T/r 时,可使流水线不间断;②每个存储周期内可读写地址连续的 m 个字;③微观上,m 个模块被串行访问;宏观上,每个存取周期内所有模块被并行访问

- 单体多字存储器

小节选择题答案

| 序号 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 答案 | B | B | B | B | B | C | D | A | D | A | C | B | ||

| 序号 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 |

| 答案 | B | D | A | D | A | B | A | A | ||||||

| 序号 | 29 | 30 | 31 | 32 | 33 | 34 | ||||||||

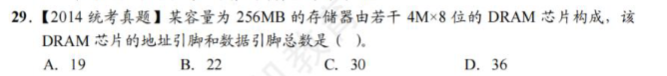

| 答案 | B |

28-34 为往年真题

5 题是要求选择错误的项

错题序号汇总:1、2、7、10、13、15、16、18、19、20、22-24、29、31-34

错题解析

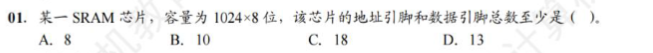

- C

- 存储容量=存储字数 x 存储字长

- 题中说容量为 1024x8 位,1024 相当于存储字数,8 位相当于存储字长

- 问的是芯片地址引脚数和数据引脚数,地址引脚数相当于 MAR 位数, 1024 = 2 10 1024=2^{10} 1024=210, 也就是用 10 个 bit 位可以表示 1024 行,地址引脚只需要 10 个

- 一个存储元件对应一个数据引脚,8 位则数据引脚需要 8 个

- 总的看数据引脚+地址引脚需要 18 个

- C

- 存储器容量 32Kx16 为,16 位表示数据线有 16 根, K = 2 10 + 2 5 = 32 K K =2^{10}+2^{5}=32K K=210+25=32K, 故地址线为 15

- A

- 主存由 RAM 和 ROM 构成,都是统一编址,而非独立编址

- 访问 RAM 的时候是随机存取,访问时间与存储单元的物理位置无关

- RAM 是随机存取,是易失性的,停电后,信息丢失

- ROM 是随机存取,ROM 是非易失性的,停电后信息不会丢失

- 关于半导体存储器的说法:

- 在同一个存储器中,每个存储单元,有多少存储器元件都是一样的

- “编址”,是指给每个存储单元一个编号

- 存储器的核心部分是存储阵列,由若干存储单元构成。存储阵列,就是磁盘阵列,有 RAID0、RAID1 等

- 每个存储单元由若干存储元件构成,每个存储元件存储一个比特位

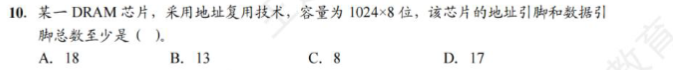

- B

- 地址复用技术可以将地址线的个数减少一半

- 1024 = 2 10 1024=2^{10} 1024=210,一般得用 10 根,由于采用了地址复用技术,所以 5 根就够了

- 8 位说明数据线需要 8 根,一共需要 13 根

- A

- RAM:SRAM (Cache) 和 DRAM(主存)都易失

- EPROM,叫可擦除可编程只读存储器,是可读也可写,但写入次数有限,属于 ROM,为非易失

- Flash 存储器,由 EPROM 发展而来,兼有 ROM 和 RAM 的优点,仍然属于 ROM,非易失

- CD-ROM 光盘,是串行访问存储器,是直接存取存储器,既不是 RAM 也不是 ROM,非易失

-

U 盘,采用 Flash 存储器技术,由 EPROM 发展而来,只读存储器

-

某计算机系统,其操作系统保存于硬盘上,其内存储器应采用:RAM+ROM

- 操作系统保存在硬盘上,开机时把操作系统从辅存调用主存中来,而主存由 DRAM 构成,易失性,OS 从辅存调入主存引导程序,肯定是非易失,ROM

- B

- 随机存储器,RAM

- EPROM,可擦除可编程只读存储器,可读可写(写入次数有限),无法取代 RAM(随机存储器),本质属于 ROM

- C

- 动态半导体存储器 DRAM (动态随机存储器)

- 工作中存储器内容不会产生变化–因为会通过刷新保证数据存在,每隔一段时间就会将原有数据刷新一遍

- 每隔一定时间,需要根据原存内容重新写入一遍

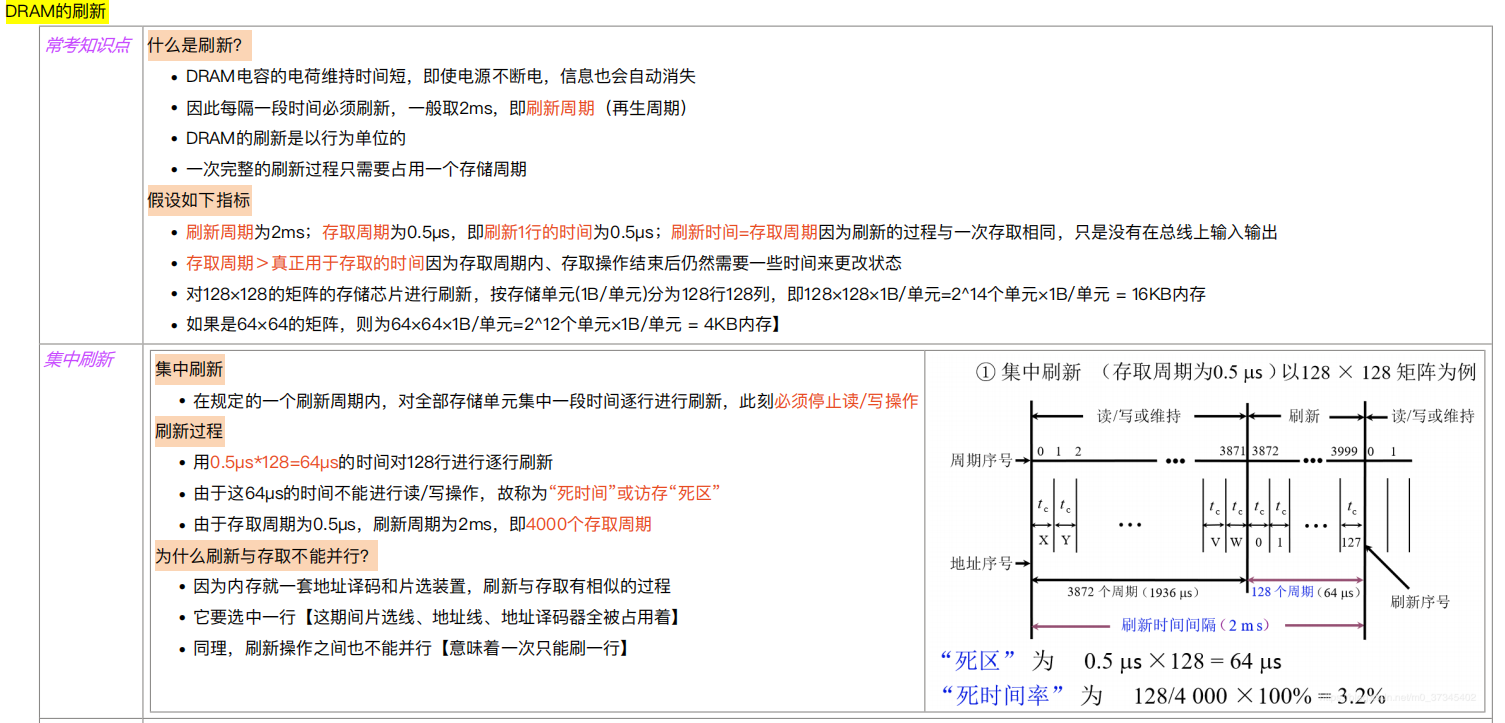

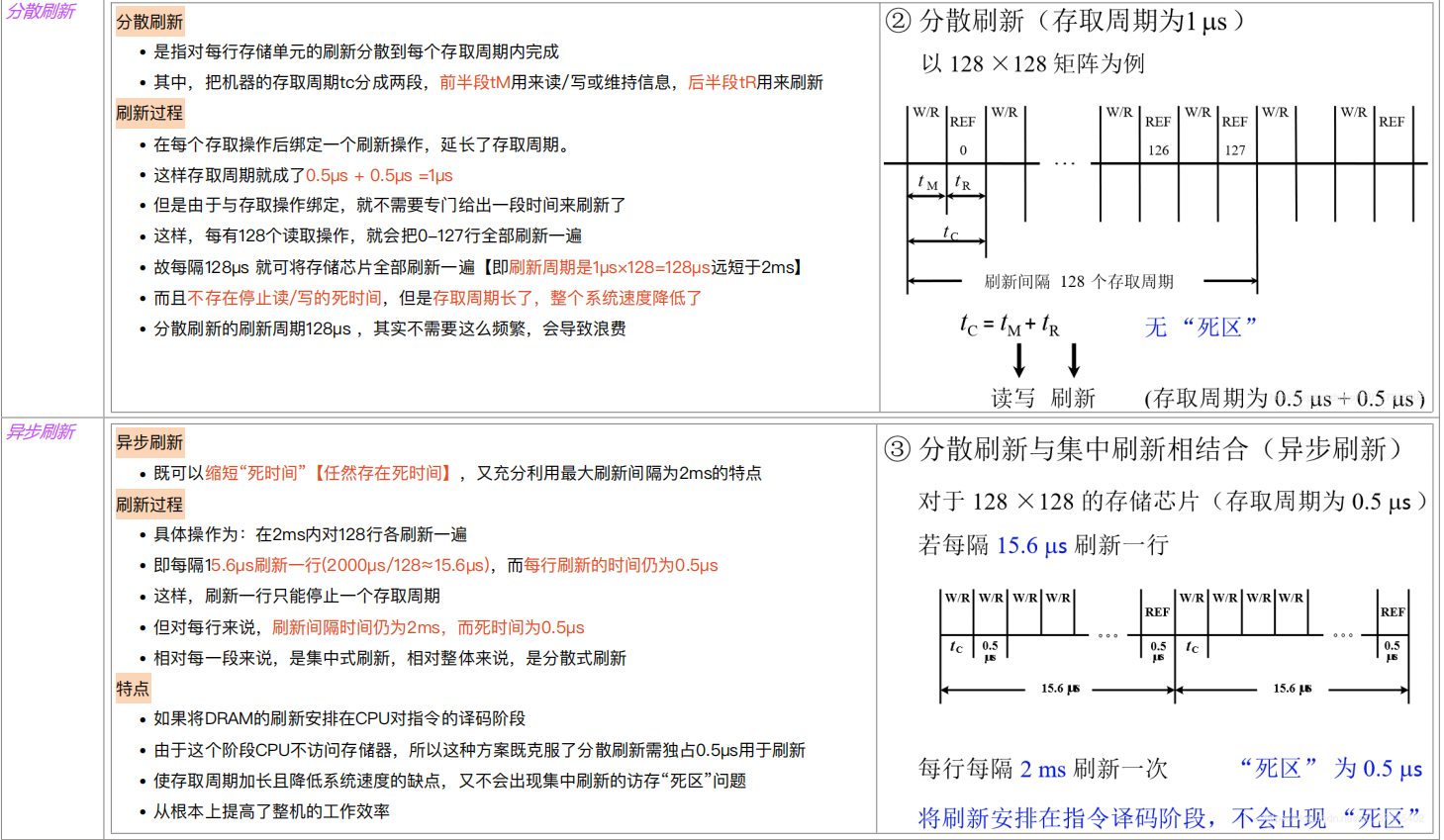

- 存储周期其实就是存取周期;DRAM 刷新分为分散、集中、异步刷新,其中分散刷新一次占一个存取周期

- A #todo暂未理解

- 一块 DRAM 芯片 64Kx1 位, 64 K = 2 16 个存储单元 64K=2^{16}个存储单元 64K=216个存储单元,1 个存储单元有 1 个存储元件,一般有 16 根地址线,应分为 8 根行地址线+8 根列地址线,1 根数据线

- 64Kx1 位的 DRAM 芯片由一个 256x256 的位平面组成。构成存储器的所有芯片同时按行刷新,每个芯片有 256 行,故存储器所有单元刷新一遍至少需要 256 次刷新操作

- 若采用异步刷新方式,则相邻两次刷新信息的时间间隔为 2ms/256=7.8us

- 若采用集中刷新方式,则整个存储器刷新一遍最少需要 256 个读/写周期,在刷新过程中,存储器不能进行读/写操作

-

刷新是通过对存储单元进行“读但不输出数据”,即“假读”的操作来实现的;②刷新是一个读取的过程,根据读出内容对相应单元进行重写,因此会和 CPU 的访存冲突,会有访存“死时间”。刷新是指每隔一定的时间必须向栅极电容补充一次电荷,并以行为单位

-

关于 DRAM 和 SDRAM 的说法:

- 传统 DRAM 芯片与 CPU 采用异步方式交换数据

- SDRAM 芯片与 CPU 采用同步方式交换数据

- DRAM 和 SDRAM 都需要定时刷新,都本质属于 RAM

- SDRAM 的行缓冲器通常用 SRAM 实现

- 突发传输方式①1 个首地址,可以传输多个数据(类比毛毛虫),普通传输1 个地址传输 1 个数据

- 每推出新一代 DRAM 芯片,地址线至少增 1 根,则容量至少提高到原来的 4 倍

- DRAM 芯片通常采用地址复用技术

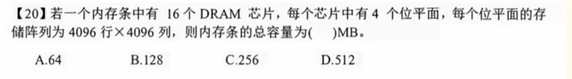

- B

- 存储阵列就是磁盘阵列:由大量存储单元组成,每个存储单元只放 1 位(1bit),排 N 行 xM 列,有 4096x4096 个存储单元,

- 1 个芯片有 4 个位平面,16 个 DRAM 就有 16x4 个位平面,1 个内存条有 16 个 DRAM,总=16x4x4096x4096x1bit= 2 30 b i t = 2 27 B = 2 7 M B = 128 M B 2^{30}bit=2^{27}B=2^7MB=128MB 230bit=227B=27MB=128MB

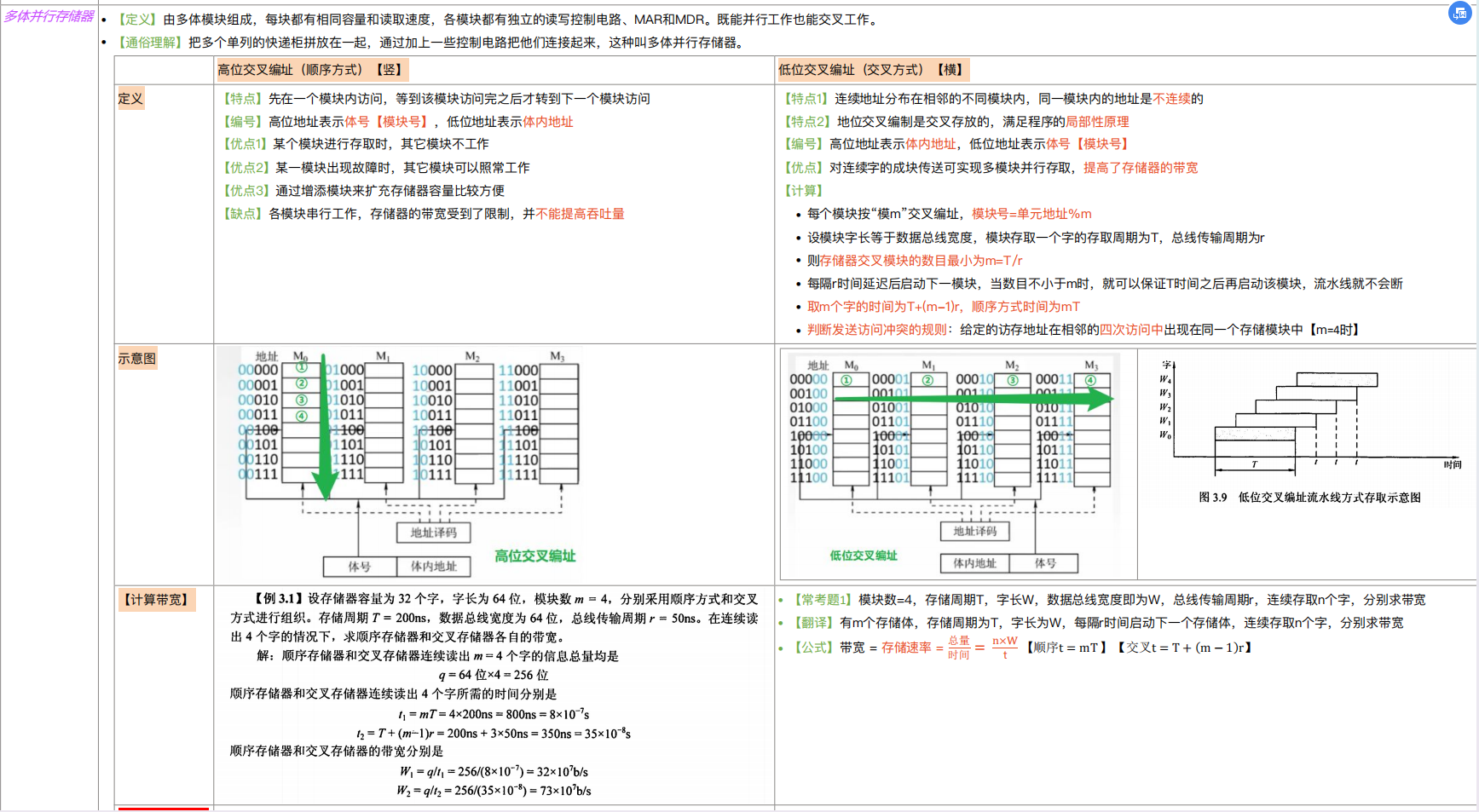

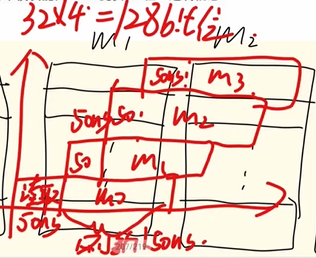

高位交叉编址和低位交叉编址

多模块存储器:说交叉编址一般默认低位交叉编址

-

高位交叉编址(顺序方式):地址+1 是加在体内地址

- 高位表示体号(高 2 位)

- 剩余表示体内地址(低 8 位)

-

低位交叉方式(交叉方式):地址+1 是体号+1

- 低位表示体号(低 2 位)

- 剩余表示体内地址(高 8 位)

- 有两种启动方式:同时启动和轮流启动

-

若每一个模块的存储单元中元件数=数据总线位数,采用轮流启动, m ≥ T / r m≥T/r m≥T/r (模块数 m0… 数大于等于模块存取周期/总线周期) T,从一个模块读一个存储单元再到读该模块第 2 个存储单元所要时间(读取恢复时间,也就是存储周期);r,读取该模块时间,不包括恢复时间,也就是总线传输周期 ,轮流启动默认从 T 开始,每 1/m 个存取周期可读出或写入一个数据(一个存储单元)

-

同时启动,每个模块每个存储单元 10bit,看总线宽度是否与模块总 bit 位是否相等,相等是同时启动

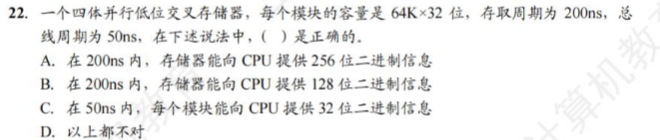

- B

- 存取周期既包含读取也有写入时间 (刷新),总线周期只有读取

- 四体说明它有四个存储模块

- 每个模块的容量是 64Kx32 位,说明有

64

K

=

2

16

行

64K=2^{16}行

64K=216行,有

2

16

2^{16}

216 个存储单元,32 位说明是 32bit

-

C #todo题未掌握

-

D

- 由 16Kx8 位的芯片组成 64Kx8 位的存储器,需要 4 个模块(64/16)

- 由 BFFFH 确定体号在第 4 个模块,地址是 0003H (第一个模块地址从 0000H 开始),是交叉编址方式,而不是顺序编址

- 关于单体多字存储器:—A

- 将多个内存条的存储单元看成一个整体的存储单元

- 对于单体多字存储器,当数据指令连续存放时,而且无过多跳转指令时,读写效率会比较高

- A 项单体多字存储器主要解决主存容量太小的问题 ❌

- 单体多字存储器中,每个存储单元存储多个字

- 指令与数据的连续存放有利于单体多字存储器提高主存的读/写速度

- 过多的跳转指令会严重影响单体多字存储器的工作效率

- 多模块存储器之所以能提高存储器的访问速度,是因为各模块有独立的读/写电路,可以实现并行操作,可以同时启动,也可以轮流启动

- 采用高速元器件:Cache、SRAM、SDRAM

- 采用信息预读技术(当一个磁盘被访问时,相同磁道上数据也会一起被读到内存缓冲区中,有点像突发传送)

- 关于闪存:

- 闪存,Flash 存储器,由 EPROM 发展而来,是非易失性,可以快速擦除与重写(可读也可写),不可替代 RAM,写速度比读速度慢

- 闪存使用 MOS 管上的栅极电压控制电流,看浮栅上有无电荷存信息,MOS 管是一种半导体存储器

- 闪存是 ROM 的一种,具有非易失性

- ROM 与 RAM 都采用随机存取方式,ROM 构成闪存,可以替代计算机外部存储器。比如 SSD(固态硬盘),基于闪存芯片,保留 Flash 的非易失性,可以快速擦除和重写,读写速度会更快,功耗会更低

- A

- 想到 DRAM 就要想到地址复用技术

- 4Mx8 位,8 位:1 个存储单元有 8 个存储元件,8bit,数据总线=8 根; 4 M = 2 22 4M=2^{22} 4M=222 采用地址复用技术需要 11 根地址总线,最后总计 19 根

- 需要刷新的存储器:

- SDRAM,本质是 DRAM,只是多了系统时钟控制,DRAM 一定需要刷新刷新

-

D (读完之后需要恢复)

-

C #todo题未掌握

-

C

- 存储阵列:由大量存储单元组成,每个存储单元放 1bit

- 2 K ∗ 1 位 = 2 11 2K*1位=2^{11} 2K∗1位=211,采用地址复用技术,行列、地址线相同

- 尽量减少刷新开销,刷新是以行为单位,行尽量少

- C

- A 选项: 内存条的容量= 8 ∗ 8192 ∗ 8192 ∗ 8 b i t = 2 32 b i t = 2 29 B = 2 9 M = 512 M B 8*8192*8192*8bit=2^{32}bit=2^{29}B=2^9M=512MB 8∗8192∗8192∗8bit=232bit=229B=29M=512MB

- B 选项:采用 8 体多模块交叉编址方式,且同时启动

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?