通信电子电路锁相环课设过程梳理

Multisim仿真实现

multisim里面没有找到CD4046集成芯片,只找到了一个替代的PLL_VIRTUAL元件,该元件集成度很高,只需要简单的设置VCO锁定频率以及低通滤波器的截止频率,外部不需要添加多余的元器件,可以说是十分方便了。

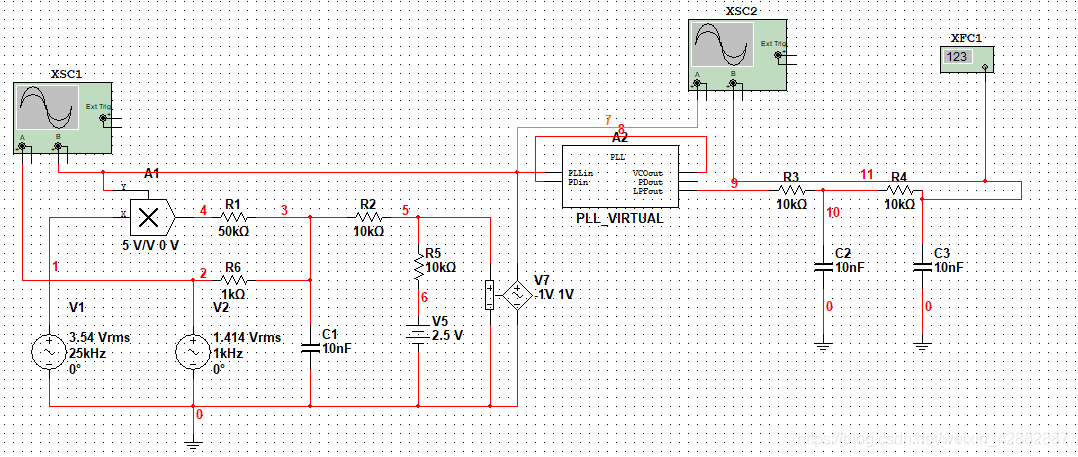

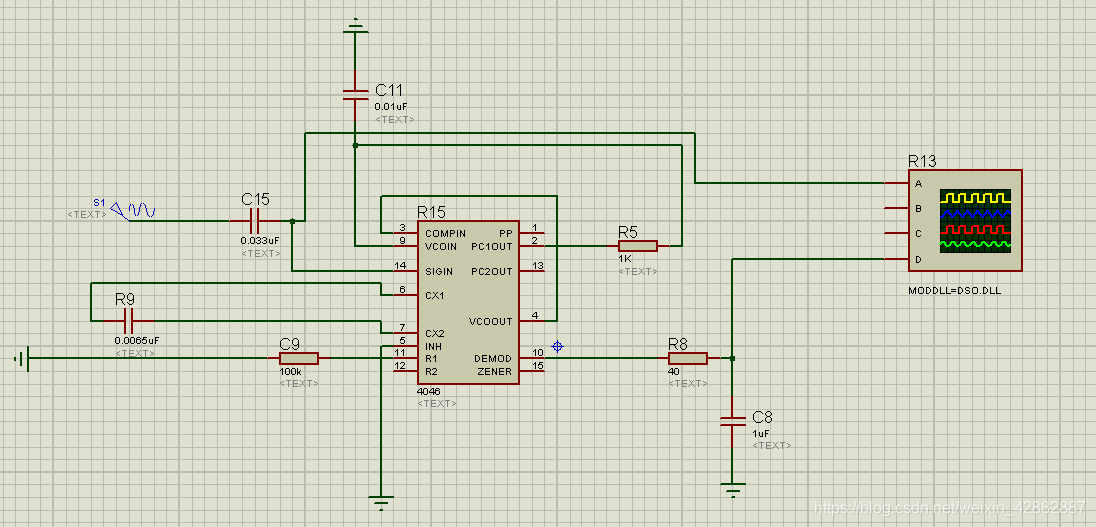

电路图

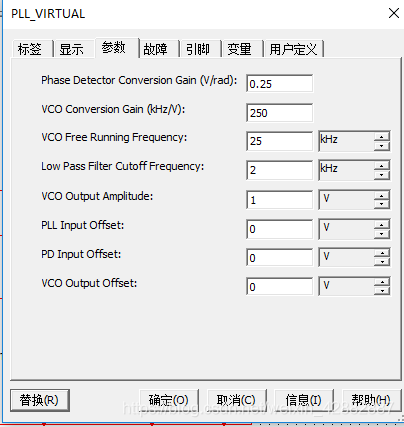

双击PLL_VIRTUAL,设置参数如下:

(是根据调频波来设置的,电路中,前面的一部分是调频电路,后边利用PLL_VIRTUAL

进行解调,调频波:载波25kHZ,信号1KHz)

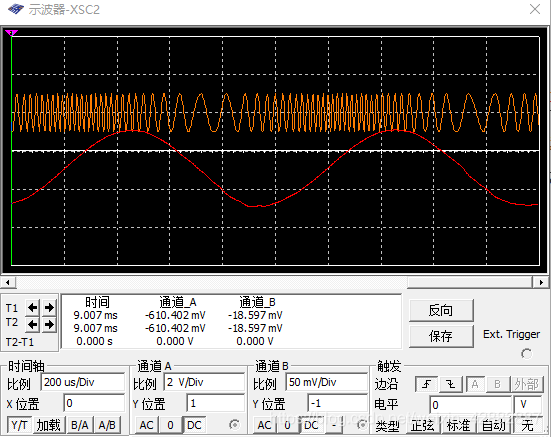

解调效果

双击示波器:

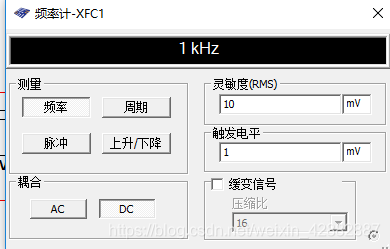

为了方便看出解调波形的频率,特意加了一个频率计,双击频率计

Proteus

元器件的查找

-

1. 停止运行才可以,改删线路

-

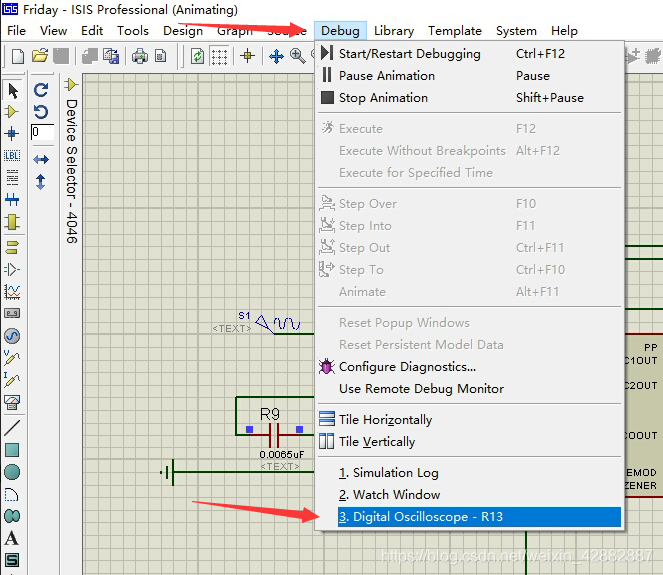

2. 双击示波器不出现波形

解决办法:

-

3. 寻找CD4046仿真芯片

点击P,输入4046查询 -

4. 寻找电容器

点击P,输入Capacitors,找到合适电容器,修改参数 -

5. 找电阻

点击P,输入res,然后选择电阻,修改参数; -

6. 找地

点击左边工具栏的终端模式,然后选择ground; -

7. 找信号源

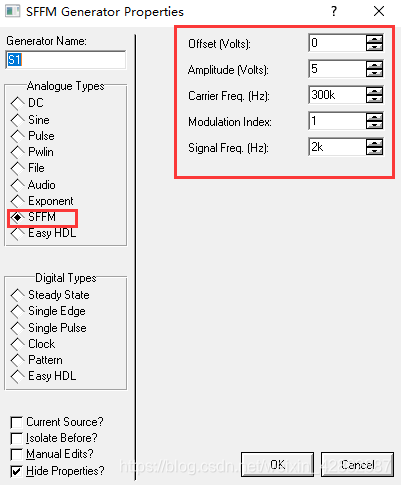

左边工具栏,选中Generator模式,选择需要的信号源,这里选择单频率调波信号发生器

注意事项

- 压控振荡器的震荡频率要和输入的载波频率一致,并且高于信号的频率

- 需要适当调整低通滤波器的参数,满足信号频率通过,过滤载波

- 音频信号的带宽范围是:200Hz到3500Hz

- 当VCO控制电压为0时,其输出频率最低;当输入控制电压等于电源电压VDD时,输出频率则线性地增大到最高输出频率

- CD4046采用的是RC型压控振荡器,必须外接电容C1和电阻R1作为充放电元件,当锁相环对跟踪的输入信号的频率宽度有要求时还需要外接电阻R2。

- 信号占空比的计算:

正脉冲的时间 除以 整个脉冲的周期

小tips,双击4046,点击右方data,可以出现该芯片的pdf参考文件

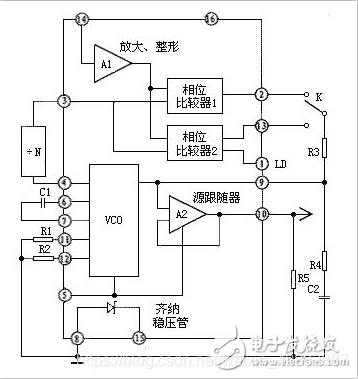

CD4046工作原理

- 输入信号 Ui从14脚输入后,经放大器A1进行放大、整形后加到相位比较器Ⅰ、Ⅱ的输入端,图3开关K拨至2脚,则比较器Ⅰ将从3脚输入的比较信号Uo与输入信号Ui作相位比较,从相位比较器输出的误差电压UΨ则反映出两者的相位差。

- UΨ经R3、R4及C2滤波后得到一控制电压Ud加至压控振荡器VCO的输入端9脚,调整VCO的振荡频率f2,使f2迅速逼近信号频率f1。

- VCO的输出又经除法器再进入相位比较器Ⅰ,继续与Ui进行相位比较,最后使得f2=f1,两者的相位差为一定值,实现了相位锁定。

- 若开关K拨至13脚,则相位比较器Ⅱ工作,过程与上述相同,不再赘述。

电子元器件的解释:

CD4046BC微功率锁相环(PLL)低功率,线性,压控振荡器的主体

(VCO),源极跟随器,齐纳二极管和两相比较。

两相比较器有一个共同点,信号输入和通用比较器输入。信号输入可以直接耦合用于大电压信号,或电容耦合到信号处的自偏置放大器最小输入用于小电压信号。

相位比较器I,一个异或门,提供数字误差信号(相位补偿I Out)并保持90°VCO中心频率的相移。

信号之间输入和比较器输入(均为50%占空比),它可能锁定在接近har-的信号输入频率上VCO中心频率的字母。

相位比较器II是边缘控制的数字存储器网络。它提供数字误差信号(相位补偿.IIOut)和锁定信号(相位脉冲)表示锁定条件并保持信号之间的0°相移输入和比较器输入。

VCO

线性压控振荡器(VCO)产生一个输出信号(VCO Out),其频率由下式确定VCO IN输入端的电压,电容和电阻 - 电感器连接到引脚C1 A,C1 B,R1和R2。**VCO IN的源跟随器输出(解调器输出)与10kΩ或更高的外部电阻一起使用。

应用

•FM解调器和调制器

•频率合成和乘法

•频率歧视

•数据同步和调节

•电压 - 频率转换

•音解码

•FSK调制

•电机速度控制

设计要求:

R1, R2 ≥ 10 kΩ, R S ≥ 10 kΩ,

C1 ≥ 50 pF.

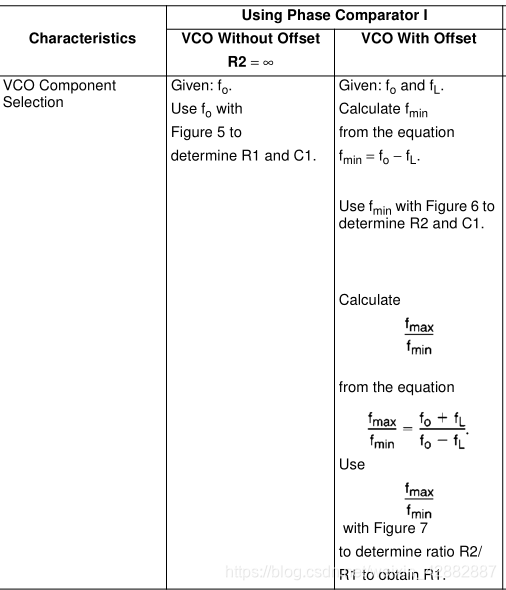

使用比较器1时:

没有信号输入的时候,VCO将调整到中心频率 f0,fmin=0;

信号输入噪声抑制高

VCO调整到fmin

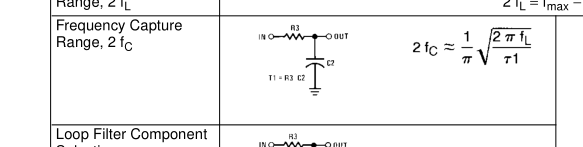

2 f L = full VCO frequency range

2 f L = f max − f min

R3,C2即为低通滤波器

参数计算设计

仿真电路图

图中的参数均是由上面所述计算得到:

信号源参数设置

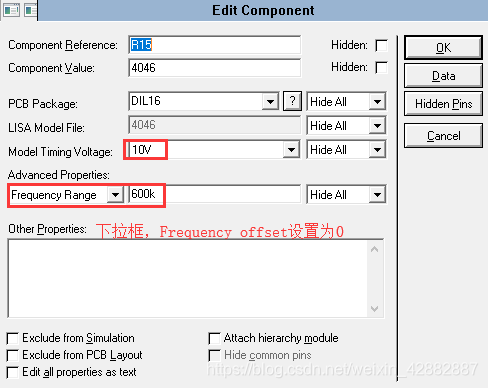

4046参数设置

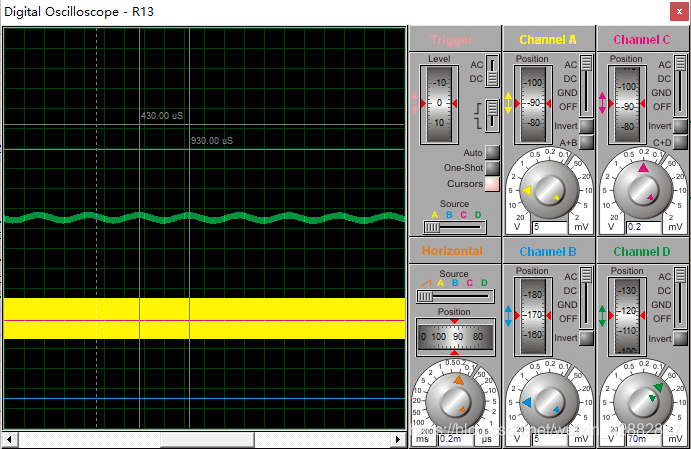

效果图

绿色的波形为解调波形,计算得到解调波形的频率为:

T=(930us-430us)= 500us;

f = 1/500us = 2kHz。和输入信号频率一致。

(下边黄色信号,为调频波,因为频率过高所以密度很大)

本文对通信电子电路锁相环课设过程进行梳理,包括Multisim仿真实现,使用PLL_VIRTUAL元件进行解调;Proteus中元器件的查找及注意事项;介绍了CD4046工作原理、电子元器件解释、VCO及应用;给出设计要求、参数计算设计和仿真电路图,最后得到解调波形频率与输入信号频率一致。

本文对通信电子电路锁相环课设过程进行梳理,包括Multisim仿真实现,使用PLL_VIRTUAL元件进行解调;Proteus中元器件的查找及注意事项;介绍了CD4046工作原理、电子元器件解释、VCO及应用;给出设计要求、参数计算设计和仿真电路图,最后得到解调波形频率与输入信号频率一致。

523

523

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?