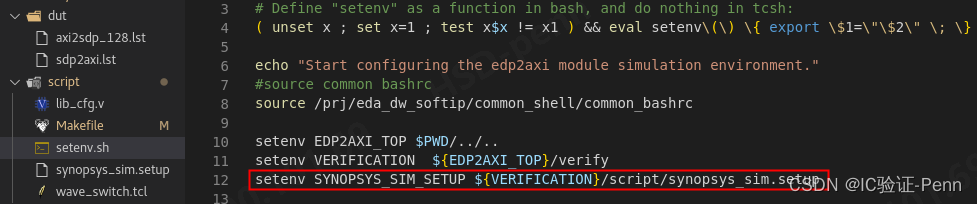

1.第一步在设置环境变量的脚本里面指定自定义的synopsys_sim.setup

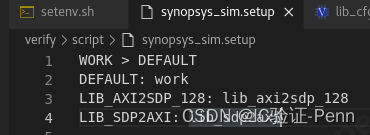

2.在synopsys_sim.setup指定需要编译的库,默认都是在work库

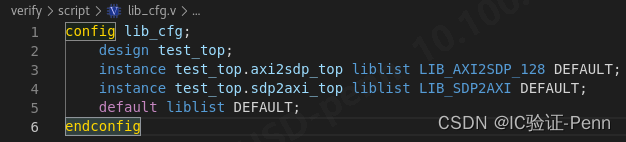

3.编写lib_cfg.v文件指明instance和lib的依赖关系

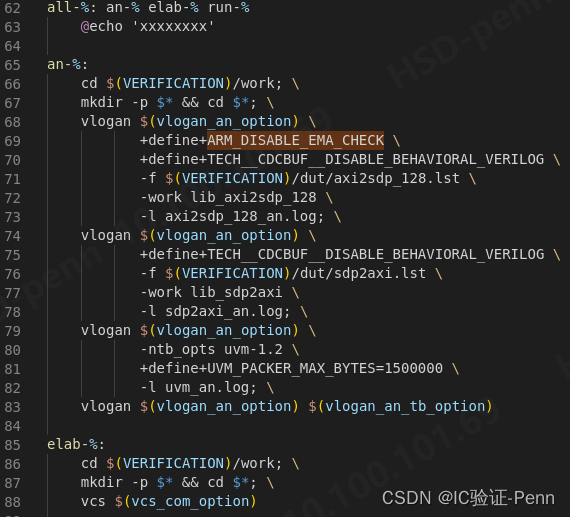

4.makefile中添加an的编译选项

5.使用vlogan编译,需要单独编译成指定库的需要加-work lib_XXX,主要分设计,uvm,tb

6.编译成库又两个作用,第一是解决module名字一样但是实现不一样,第二是提高仿真效率

如果为了提高效率,可以把lib编译出来之后,如果内容不变,可以直接引用,lib_cfg.v文件如下

config xxx

design tb_top;

default liblist DEFAULT LIB_AXI2SDP_128 LIB_SDP2AXI;

endconfig

注意:这个就是使用的3步编译法,2步编译不适用,这也就是3步编译法更具灵活性,大型项目一般使用3步,小型项目使用2步,根本还是为了提高效率;

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?