首先是软件的下载,这里我下载的是quartus2(altera芯片),modelsim(仿真工具),notepad++(代码编辑器),下载方式csdn上都有,我就不再详述了。这里注意的是quartus2版本要和后面下载的器件库版本一致,器件库可以在intel官网里面下载。

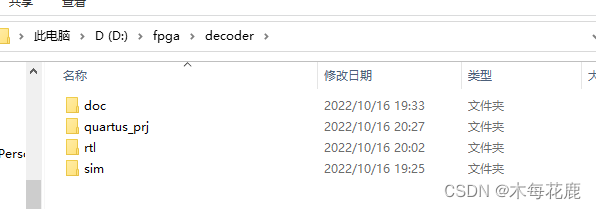

下面讲一个好习惯

每个模块下面创建4个文件夹,doc可以放一些框图,真值表之类的。prj拿来放工程文件,rtl拿来放rtl代码,sim拿来放仿真相关文件以及testbench之类的。

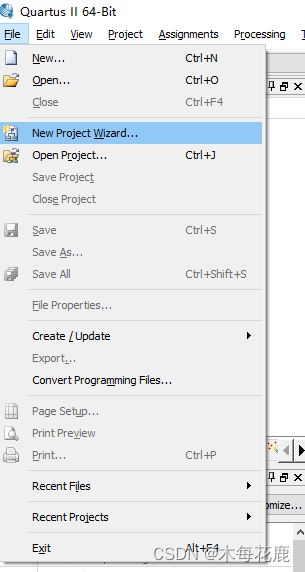

本次从工程文件创立讲起,进入quartus先建立工程文件

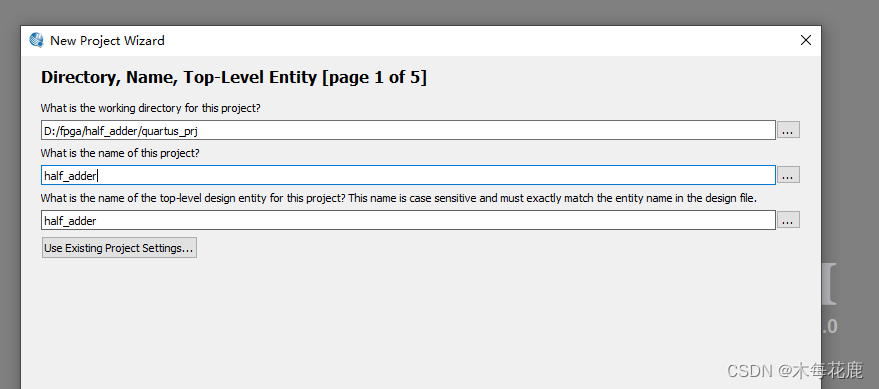

继续下一步,第一行是文件存放位置,存放在提前建好的prj文件夹,第二行是名字,一般直接模块名

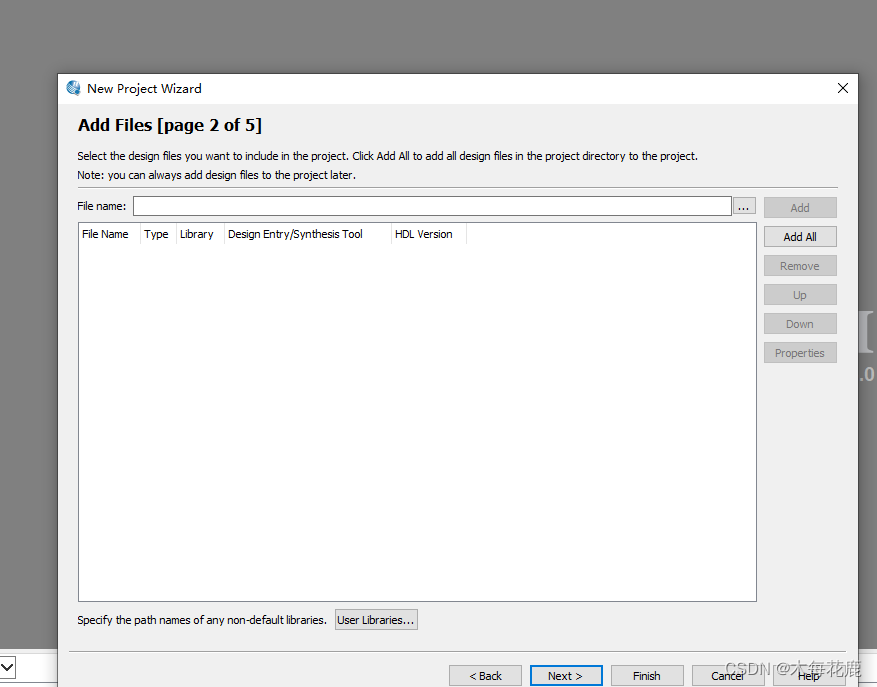

这一步是添加已经写好的rtl代码,这里不用添加直接下一步

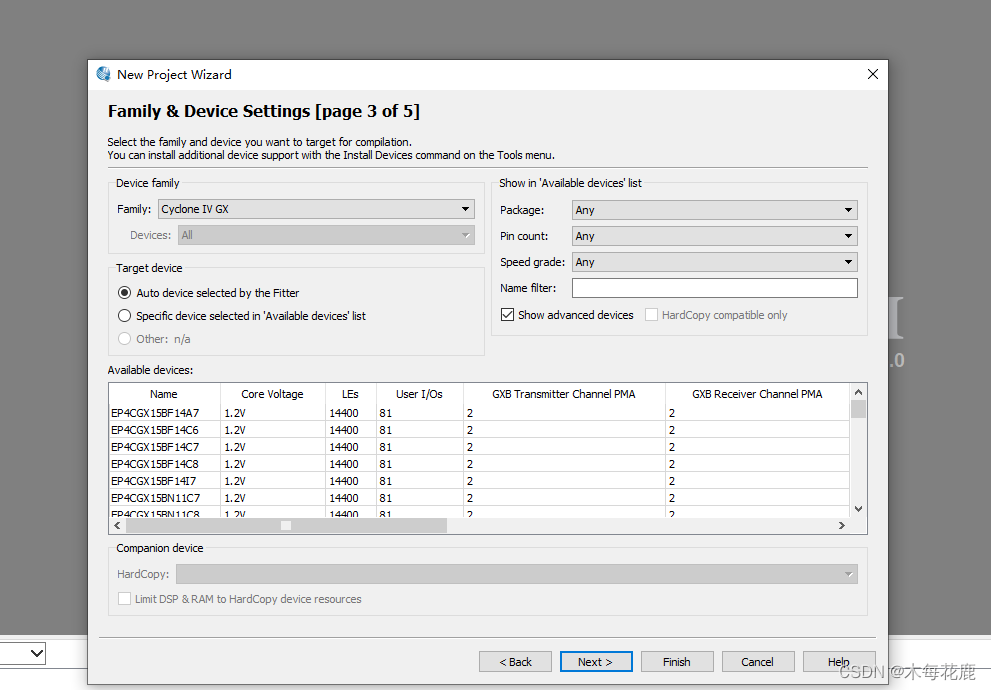

这里在已经下载好的器件库里选择对应的芯片

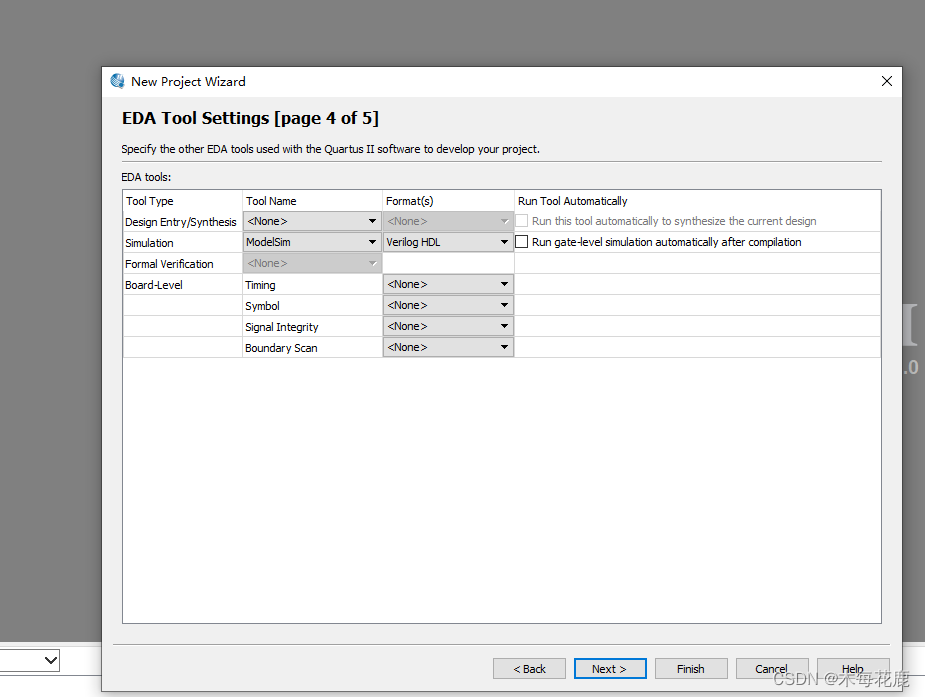

这里把仿真那一项选择modelsim,后面做联合仿真

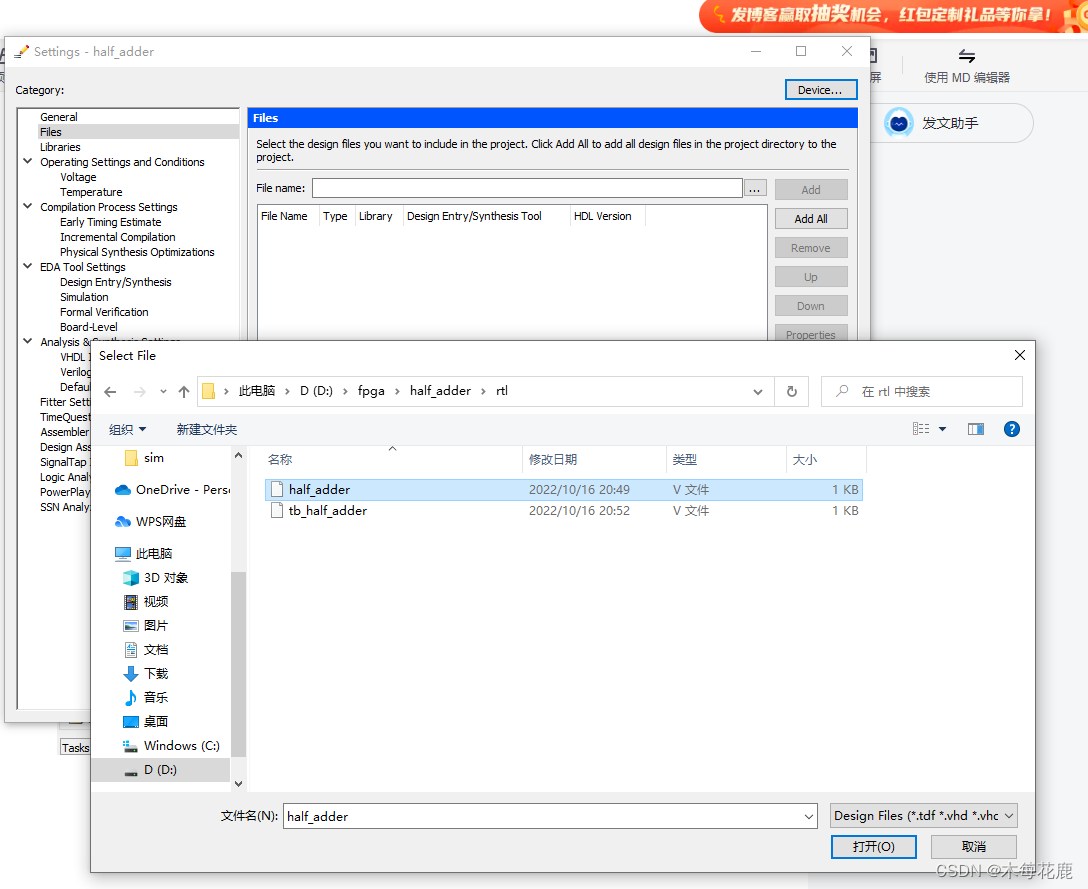

然后就创建工程完成,选择下面file,然后右键准备添加写好的verilog代码

然后就创建工程完成,选择下面file,然后右键准备添加写好的verilog代码

然后点击add添加,apply应用

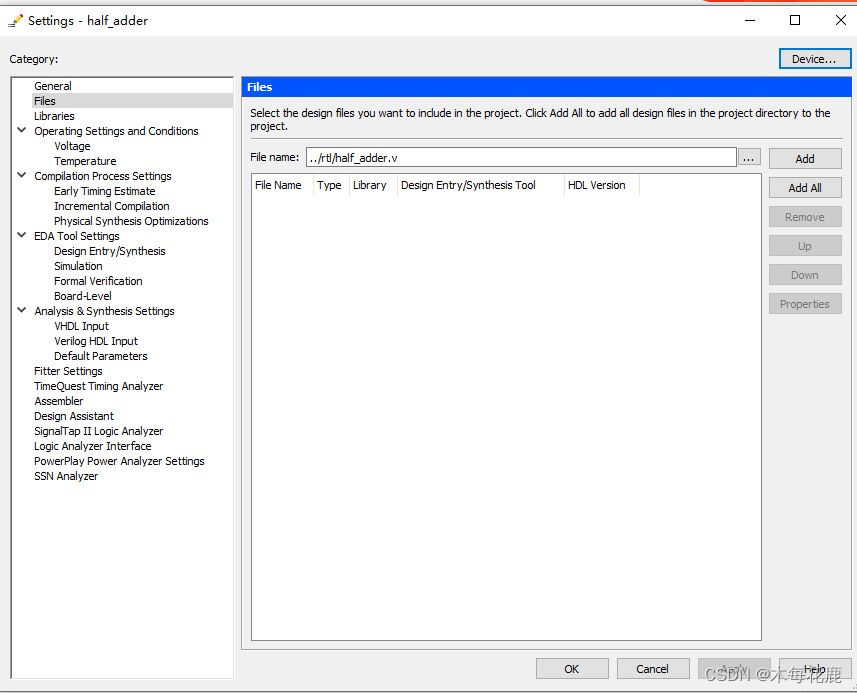

这个时候已经添加成功了

这个时候已经添加成功了

这篇博客介绍了FPGA自学的初步过程,包括使用Quartus II和Modelsim进行开发和仿真,以及Notepad++作为代码编辑器。作者强调了良好的文件组织习惯,并详细讲解了如何创建工程、添加Verilog代码以及进行编译。内容涵盖了半加器和全加器的逻辑设计,通过Visio绘制的框图和真值表进行辅助理解,同时提供了Testbench的编写方法,通过Modelsim进行联合仿真验证逻辑的正确性。

这篇博客介绍了FPGA自学的初步过程,包括使用Quartus II和Modelsim进行开发和仿真,以及Notepad++作为代码编辑器。作者强调了良好的文件组织习惯,并详细讲解了如何创建工程、添加Verilog代码以及进行编译。内容涵盖了半加器和全加器的逻辑设计,通过Visio绘制的框图和真值表进行辅助理解,同时提供了Testbench的编写方法,通过Modelsim进行联合仿真验证逻辑的正确性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1948

1948

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?