文章目录

-

- 一、实验目的

-

二、实验内容

-

三、实验设计

-

四、实验结果及仿真

熟悉元件封装方法,掌握层次化电路设计方法;掌握VHDL例化语句的设计方法。

1.用VHDL语言设计1位全加器,其中仅就半加器实体进行例化声明及端口映射语句,或运算直接调用运算函数。通过编译、仿真验证功能正确性。

2.就实验过程及结果进行简要描述和分析,并思考与用原理图方法设计的各自特点。

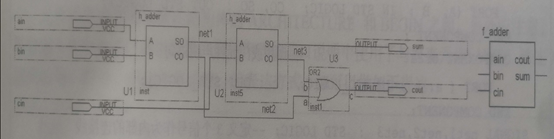

全加器可以由两个半加器和一个或门连接而成,其经典的电路结构如下图所示。图的右侧是全加器的实体模块,它显示了全加器的端口情况。设计全加器之前,需要先设计好半加器。

整个设计过程和表述方式都可以用VHDL来描述。首先设计出半加器。半加器实现的VHDL描述如下所示。

Library Ieee;

Use Ieee.Std_Logic_1164.All;

Entity h_adder is

port (a,b : in Std_Logic; co,so : out Std_Logic);

End Entity h_adder;

Architecture Bhv of

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7063

7063

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?