1.四选一数据选择器,Y为输出,D0~D3为输入,S为选择控制,代码如下:

module mux4_case (Y,D0,D1,D2,D3,S); //四选一数据选择器

input D0,D1,D2,D3;

input[1:0] S;

output reg Y;

always @(S or D0 or D1 or D2 or D3)

case(S)

2'b00: Y=D0;

2'b01: Y=D1;

2'b10: Y=D2;

default: Y=D3;

endcase

endmodule约束文件(ISE):

## Clock signal

#NET "clk" LOC = B8 | IOSTANDARD = LVCMOS33;

## FPGAOL LEDs(signle-digit-SEGPLAY)

NET "Y" LOC=K17 | IOSTANDARD = LVCMOS33;

## FPGAOL SWs

NET "D0" LOC=M13 | IOSTANDARD = LVCMOS33;

NET "D1" LOC=R18 | IOSTANDARD = LVCMOS33;

NET "D2" LOC=T18 | IOSTANDARD = LVCMOS33;

NET "D3" LOC=N14 | IOSTANDARD = LVCMOS33;

NET "S[0]" LOC=U12 | IOSTANDARD = LVCMOS33;

NET "S[1]" LOC=U11 | IOSTANDARD = LVCMOS33; 2.跑马灯,通过S控制,实现左移、右移、对开、对分,100MHz时钟经分频后频率约6Hz,跑马灯的转换频率约为3Hz,代码如下:

module led_run(Y,clk,S); //跑马灯,S控制方向、模式,实现左移/右移,对开/对分

input clk; //100MHz

input[1:0] S;

output reg[7:0] Y;

reg[3:0] count=0;

reg[23:0] cnt=0;

always@(posedge clk) //分频

cnt<=cnt+1;

always@(posedge cnt[23]) //低频时钟

begin

count[2:0]=count[2:0]+2*S[0]-1; //改变方向

count[3]=S[1]; //改变模式

end

always@(count)

case(count)

0:Y=8'b10000000;

1:Y=8'b01000000;

2:Y=8'b00100000;

3:Y=8'b00010000;

4:Y=8'b00001000;

5:Y=8'b00000100;

6:Y=8'b00000010;

7:Y=8'b00000001;

8:Y=8'b10000001;

9:Y=8'b01000010;

10:Y=8'b00100100;

11:Y=8'b00011000;

12:Y=8'b10000001;

13:Y=8'b01000010;

14:Y=8'b00100100;

15:Y=8'b00011000;

default:Y=8'b10000000;

endcase

endmodule对应的约束文件(ISE):

## Clock signal

NET "clk" LOC = B8 | IOSTANDARD = LVCMOS33;

## FPGAOL LEDs(signle-digit-SEGPLAY)

NET "Y[0]" LOC=K17 | IOSTANDARD = LVCMOS33;

NET "Y[1]" LOC=K18 | IOSTANDARD = LVCMOS33;

NET "Y[2]" LOC=L14 | IOSTANDARD = LVCMOS33;

NET "Y[3]" LOC=M14 | IOSTANDARD = LVCMOS33;

NET "Y[4]" LOC=L18 | IOSTANDARD = LVCMOS33;

NET "Y[5]" LOC=M18 | IOSTANDARD = LVCMOS33;

NET "Y[6]" LOC=R12 | IOSTANDARD = LVCMOS33;

NET "Y[7]" LOC=R13 | IOSTANDARD = LVCMOS33;

## FPGAOL SWs

NET "S[0]" LOC=U12 | IOSTANDARD = LVCMOS33;

NET "S[1]" LOC=U11 | IOSTANDARD = LVCMOS33;

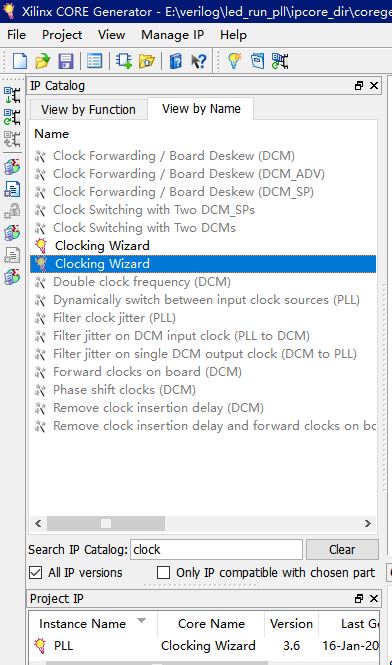

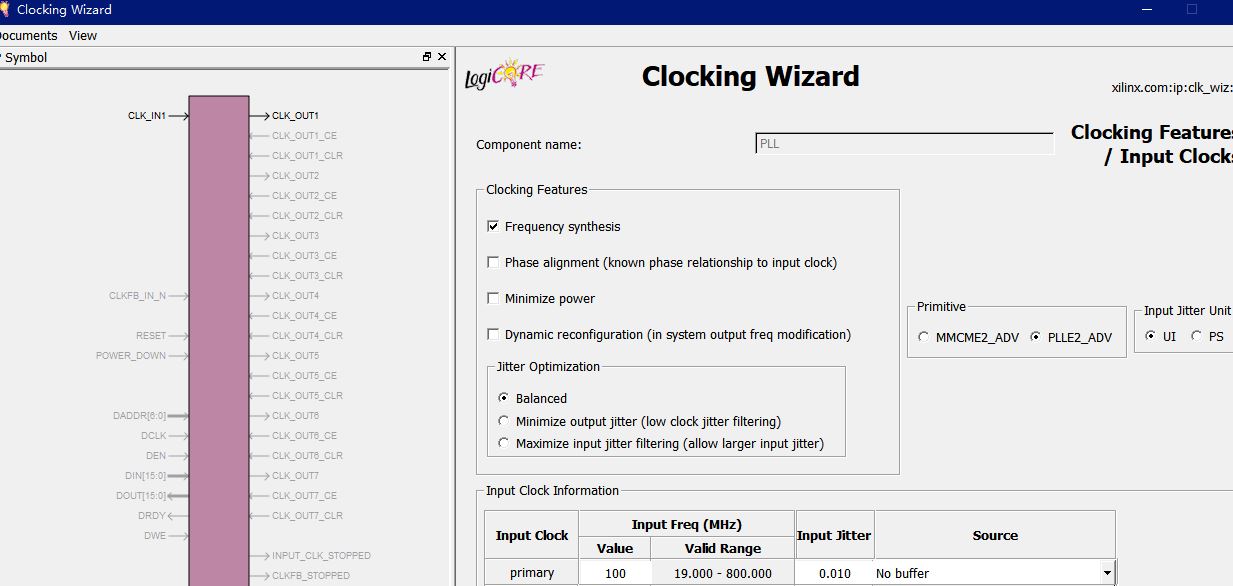

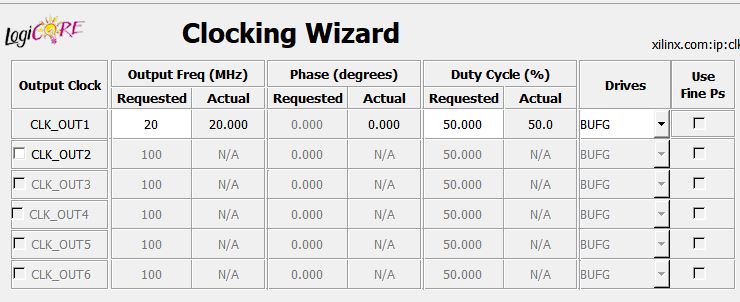

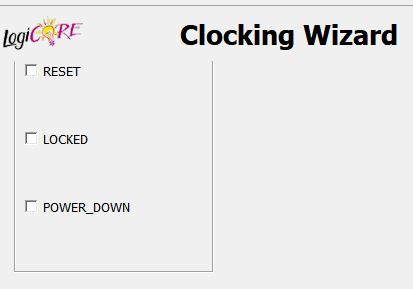

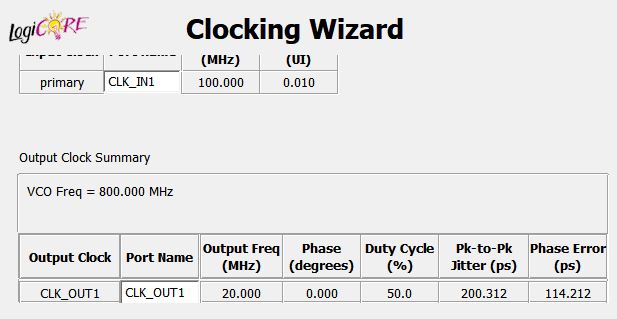

3.通过PLL,可以方便地生成所需要频率的时钟,板载时钟为100MHz,为了作出比较,引入20MHz时钟,利用PLL产生,PLL操作流程如下:

代码如下:

module led_run(Y,clk,S); //跑马灯,S控制方向、模式,实现左移/右移,对开/对分

input clk; //100MHz

input[1:0] S;

output reg[7:0] Y;

reg[3:0] count=0;

reg[23:0] cnt=0;

always@(posedge CLK_OUT1) //分频

cnt<=cnt+1;

always@(posedge cnt[23]) //低频时钟

begin

count[2:0]=count[2:0]+2*S[0]-1; //改变方向

count[3]=S[1]; //改变模式

end

always@(count)

case(count)

0:Y=8'b10000000;

1:Y=8'b01000000;

2:Y=8'b00100000;

3:Y=8'b00010000;

4:Y=8'b00001000;

5:Y=8'b00000100;

6:Y=8'b00000010;

7:Y=8'b00000001;

8:Y=8'b10000001;

9:Y=8'b01000010;

10:Y=8'b00100100;

11:Y=8'b00011000;

12:Y=8'b10000001;

13:Y=8'b01000010;

14:Y=8'b00100100;

15:Y=8'b00011000;

default:Y=8'b10000000;

endcase

PLL U0(

.CLK_IN1 (clk),

.CLK_OUT1 (CLK_OUT1)

);

endmodule

文章展示了两个Verilog模块的实现,一个是四选一数据选择器,通过输入S控制选择D0到D3中的一个作为输出Y;另一个是跑马灯逻辑,利用S控制跑马灯的左移、右移、对开和对分模式,100MHz时钟经过分频产生6Hz左右的低频时钟,使得跑马灯转换频率约为3Hz。

文章展示了两个Verilog模块的实现,一个是四选一数据选择器,通过输入S控制选择D0到D3中的一个作为输出Y;另一个是跑马灯逻辑,利用S控制跑马灯的左移、右移、对开和对分模式,100MHz时钟经过分频产生6Hz左右的低频时钟,使得跑马灯转换频率约为3Hz。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?