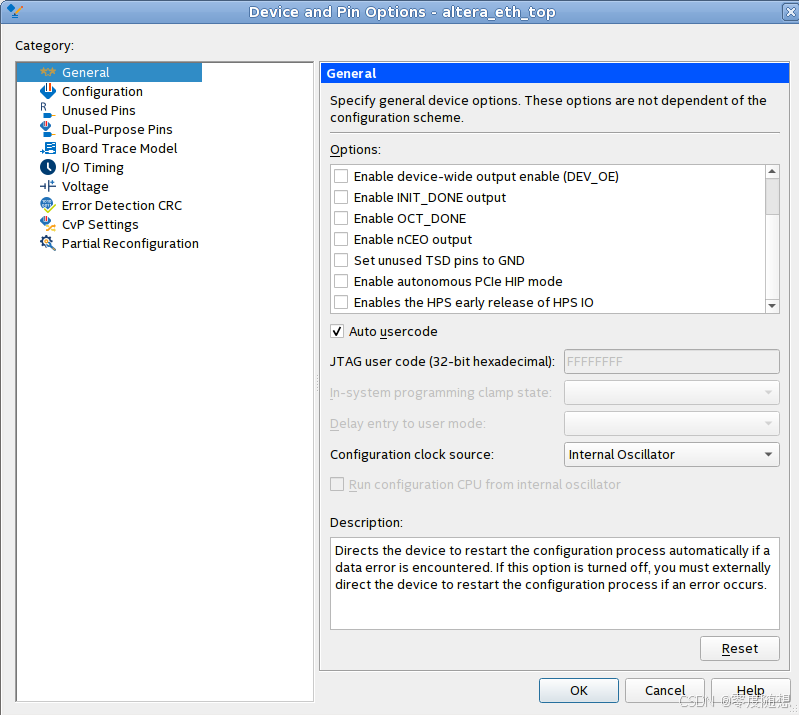

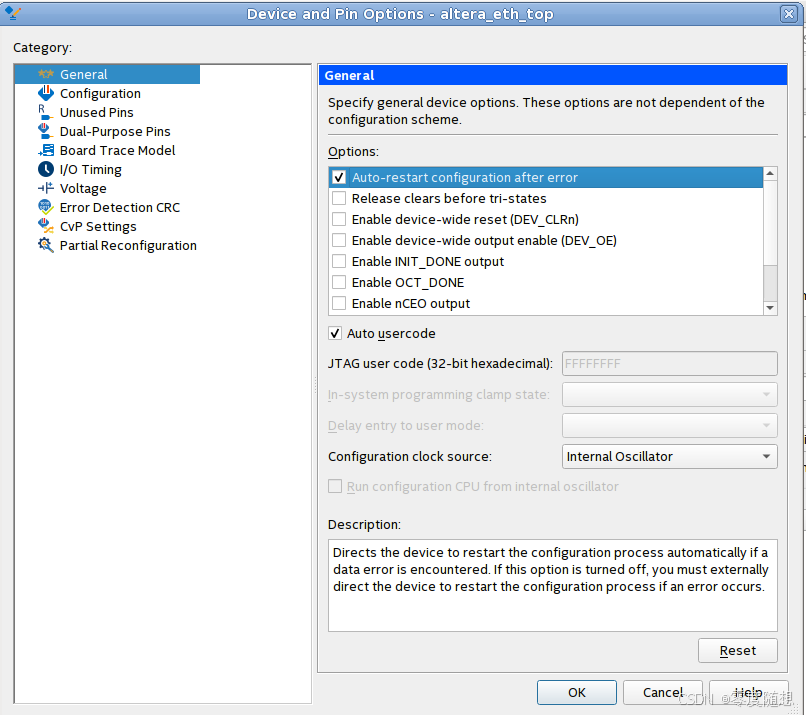

配置 Altera FPGA(现场可编程门阵列)设备的“Device and Pin Options”对话框,选项是和 FPGA 的设备选项相关的。每个选项的功能如下:

1. Auto-restart configuration after error

- 当设备在配置过程中遇到错误时,会自动重启配置过程。如果不勾选这个选项,则需要手动指示设备重新启动配置过程。

2. Release clears before tri-states

- 在配置完成时,清除信号将会在三态信号之前被释放。这对于确保器件在三态输出之前已经清除是很有用的。

3. Enable device-wide reset (DEV_CLRn)

- 启用整个设备的复位(DEV_CLRn)功能。激活此信号会将整个设备复位到初始状态。

4. Enable device-wide output enable (DEV_OE)

- 启用设备的整体输出使能功能(DEV_OE)。当这个信号激活时,设备的所有输出会被有效地使能,否则输出将被禁用。

5. Enable INIT_DONE output

- 启用 INIT_DONE 输出引脚。在设备成功初始化完成后,此引脚会输出一个信号,表示设备已经准备好。

6. Enable OCT_DONE

- 启用 OCT_DONE 引脚,用于指示片上端接(On-Chip Termination)完成。

7. Enable nCEO output

- 启用 nCEO 输出引脚,通常用于级联配置模式,用来通知下一个 FPGA 器件当前配置状态。

8. Set unused TSD pins to GND

- 将未使用的 TSD(时钟发生器)引脚接地。这样可以防止引脚悬空,从而降低噪声和功耗。

9. Enable autonomous PCIe HIP mode

- 启用 PCIe(PCI Express)HIP(硬件接口层)的自主模式。这允许 PCIe 硬核在不需要 FPGA 配置的情况下自动初始化并工作。

10. Enables the HPS early release of HPS IO

- 允许 HPS(硬处理器系统)在 FPGA 完全配置完成之前,提前释放 HPS IO 引脚。这在特定的系统设计中可能会有所需求,允许处理器和外设尽早进行通信。

11. Auto usercode

- 自动生成一个用户代码。这个代码用于识别 FPGA 器件,可以是 32 位的用户定义标识符。

12. JTAG user code (32-bit hexadecimal)

- JTAG 用户代码字段,允许用户手动输入一个 32 位的十六进制代码,以识别 FPGA。通常用于测试和调试。

13. Configuration clock source

- 配置时钟源,用于定义 FPGA 配置过程中使用的时钟源。选择“Internal Oscillator”(内部振荡器)意味着 FPGA 将使用内置的时钟源。

这些选项可以帮助用户在 FPGA 的配置过程中进行特定的设置,以满足不同的应用需求。希望这能帮助您更好地理解这些配置选项的作用!

765

765

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?