资料下载请点我(第4次更新)

关于今日推文

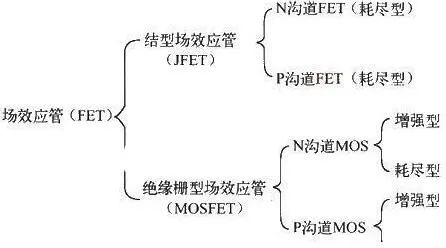

场效应晶体管(Field Effect Transistor缩写(FET))简称场效应管。主要有两种类型(junction FET—JFET)和金属 - 氧化物半导体场效应管(metal-oxide semiconductor FET, 简称MOS-FET)。由多数载流子参与导电,也称为单极型晶体管。它属于电压控制型半导体器件。具有输入电阻高(107~1015Ω)、噪声小、功耗低、动态范围大、易于集成、没有二次击穿现象、安全工作区域宽等优点。场效应管(FET)是利用控制输入回路的电场效应来控制输出回路电流的一种半导体器件,并以此命名。由于它仅靠半导体中的多数载流子导电,又称单场极型晶体管。场效应管分为两种类别:结型场效应管(JFET)和绝缘栅场效应管(MOS管)。下文会着重介绍场效应管种类的具体知识与区别。

本文详细解析了N沟道和P沟道结型场效应管的工作原理,重点阐述了增强型MOS管的工作机制,当VGS=0时管子截止,加上适当电压后,载流子被吸引形成导电沟道。此外,还介绍了N沟道增强型场效应管的特点。

本文详细解析了N沟道和P沟道结型场效应管的工作原理,重点阐述了增强型MOS管的工作机制,当VGS=0时管子截止,加上适当电压后,载流子被吸引形成导电沟道。此外,还介绍了N沟道增强型场效应管的特点。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1764

1764

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?