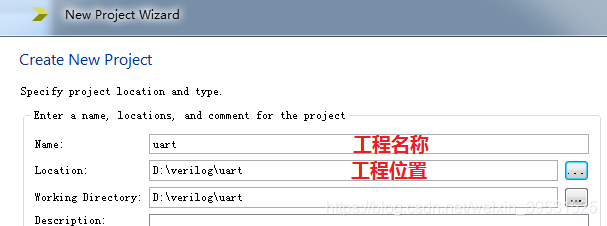

File \ New Project,弹出如下界面

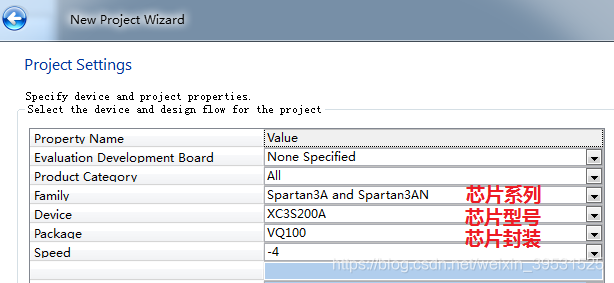

按下图介绍更改后点击“next” => “finish”

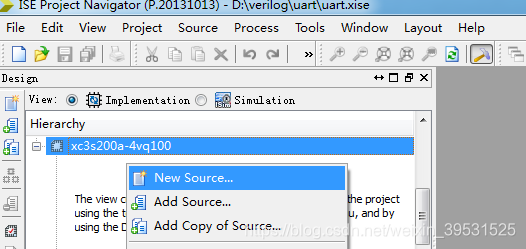

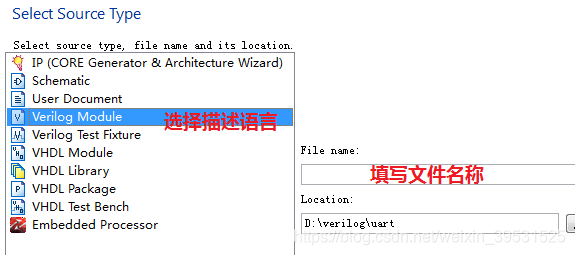

新建一个Verilog文件

填写文件名称后,点击“next”=>“next”=>“finish”

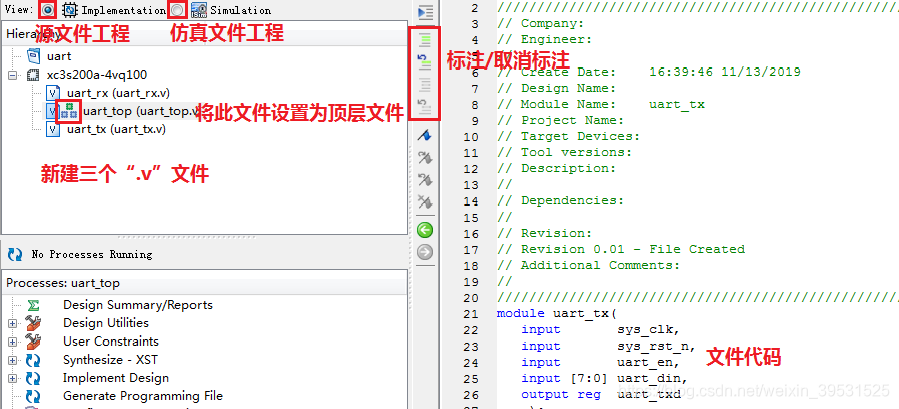

建立三个文件,并将其中之一设置为顶层文件,见下图

对两个非顶层文件进行语法检查

对顶层文件进行语法检查双击“Synthesize - XST”

出现”Process “Synthesize - XST” completed successfully”表明编译成功!

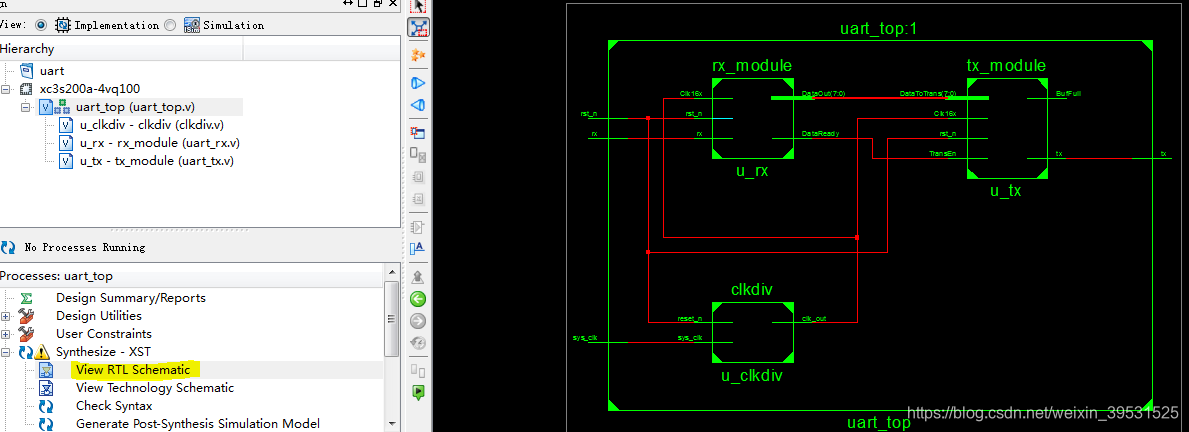

查看RTL

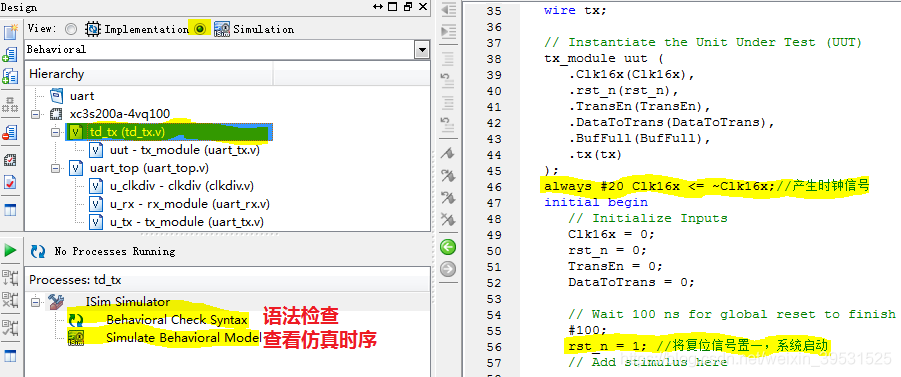

对某一文件添加仿真

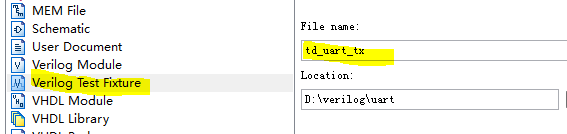

右键/new source/选择"Verilog Test Fixture"/填写测试文件名称"td_xx"

仿真界面

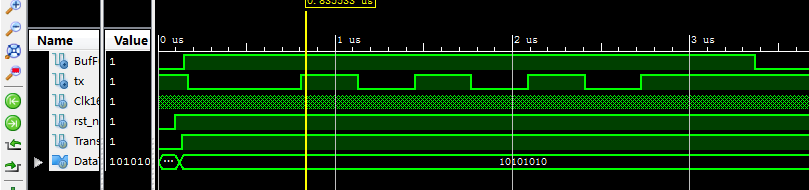

仿真结果

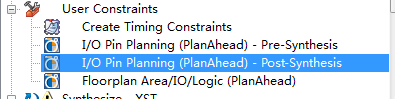

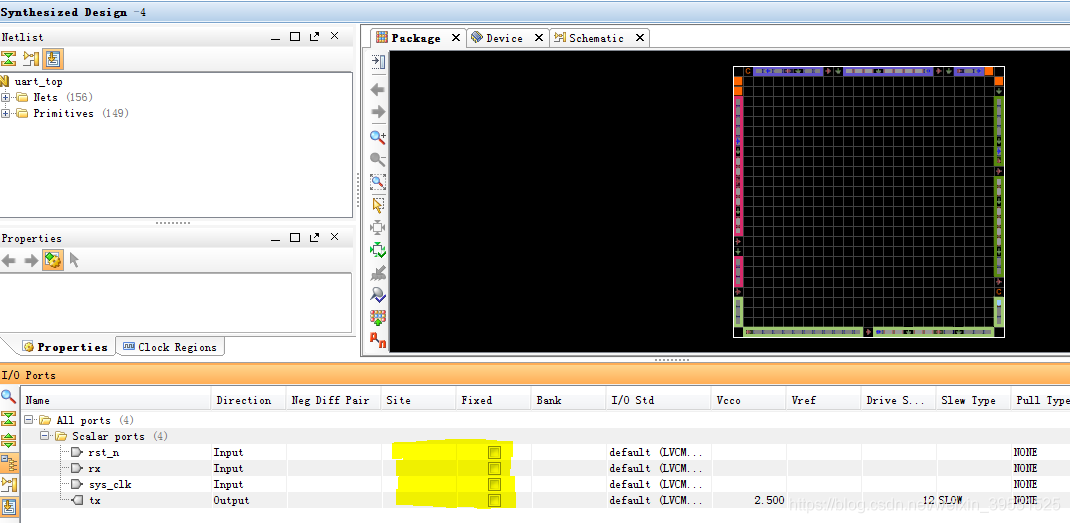

添加硬件约束,管教约束文件。

生成".bit"流文件,就可以烧录程序了

ISE Design Suite 14.7创建一个Xilinx工程

最新推荐文章于 2025-04-11 19:39:46 发布

本文详细介绍使用FileNewProject创建Verilog项目的过程,包括文件的建立、语法检查、合成、RTL视图查看、仿真设置及硬件约束添加,直至生成.bit流文件。

本文详细介绍使用FileNewProject创建Verilog项目的过程,包括文件的建立、语法检查、合成、RTL视图查看、仿真设置及硬件约束添加,直至生成.bit流文件。

2511

2511

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?