1、如何编译UVM代码

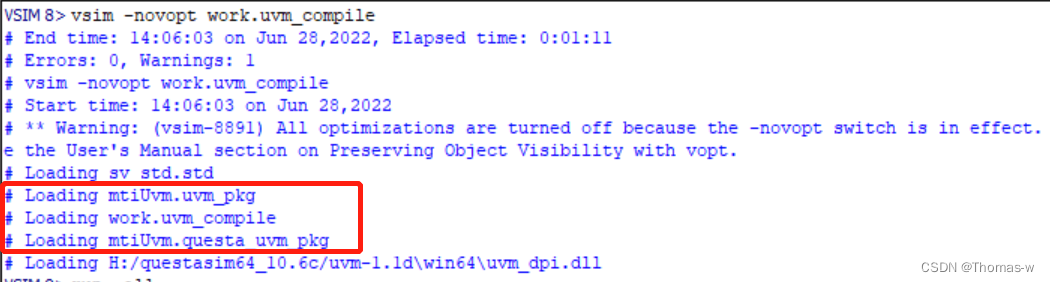

首先添加文件,然后编译文件,在work库里面进行模块仿真uvm_compile,命令窗口中运行“run -all” 查看输出仿真语句。

uvm_compile代码:

module uvm_compile;

import uvm_pkg::*;

`include "uvm_macros.svh"

initial begin

`uvm_info("UVM", "Hello, welcome to RKV UVM training!", UVM_LOW)

#1us;

`uvm_info("UVM", "Bye, and more gifts waiting for you!", UVM_LOW)

end

endmodule

编译了uvm_compile,但是同样也加载了uvm_pkg,这是因为 import uvm_pkg::*; 已经默认把他编译到mtiuvm里面了,默认已经编译好的库。

sv_std.std:指的是systemverilog的内建包,定义了一些class、task、function和变量;

mtiUvm.uvm_pkg:表示mentor已经编译好的库

mtiUvm.questa_uvm_pkg:是questa专门针对uvm定制的库

无论在什么地方,我们的验证顶层都需要这两句话,代表的是从预编译的UVM库

import uvm_pkg::*;

`include "uvm_macros.svh";2、SV和UVM之间的联系

sv_class_inst代码:

module sv_class_inst;

import uvm_pk

本文详细介绍了UVM代码编译流程,包括uvm_compile示例,SV和UVM间的联系,验证顶层的区别,以及搭建验证平台和编写测试用例的方法。通过实例展示了如何查看对象和组件继承,以及UVM验证的启动步骤。

本文详细介绍了UVM代码编译流程,包括uvm_compile示例,SV和UVM间的联系,验证顶层的区别,以及搭建验证平台和编写测试用例的方法。通过实例展示了如何查看对象和组件继承,以及UVM验证的启动步骤。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1582

1582

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?