在上一章我们已经把DDR4的IP核配置好了,这一章来描述一下DDR4 IP核的例化接口,以及接口的作用。

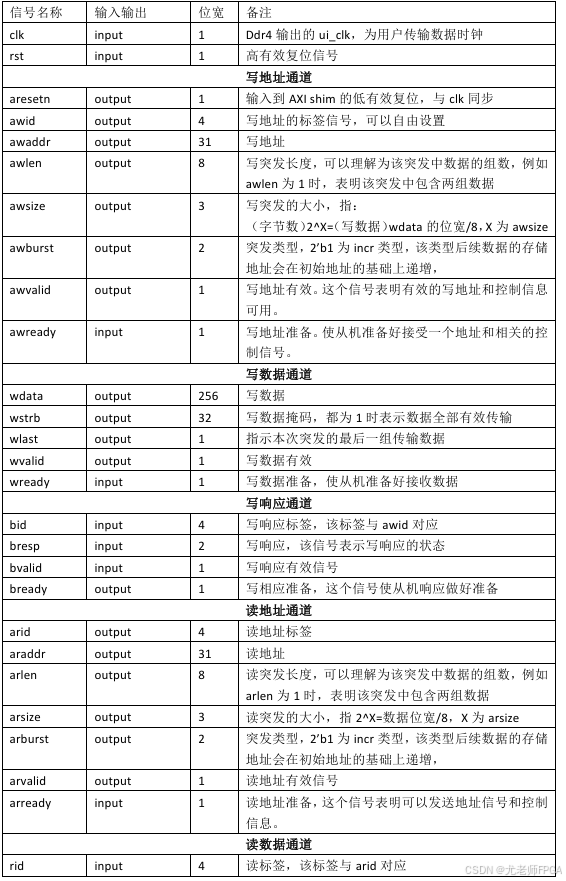

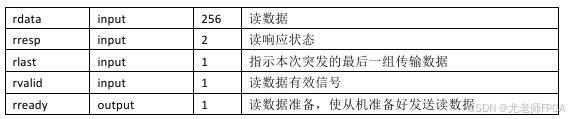

DDR4 IP核接口列表

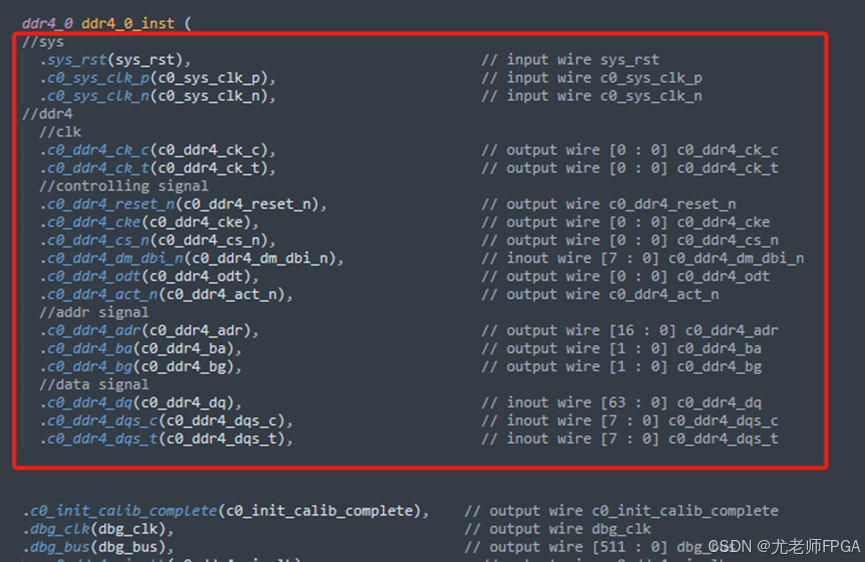

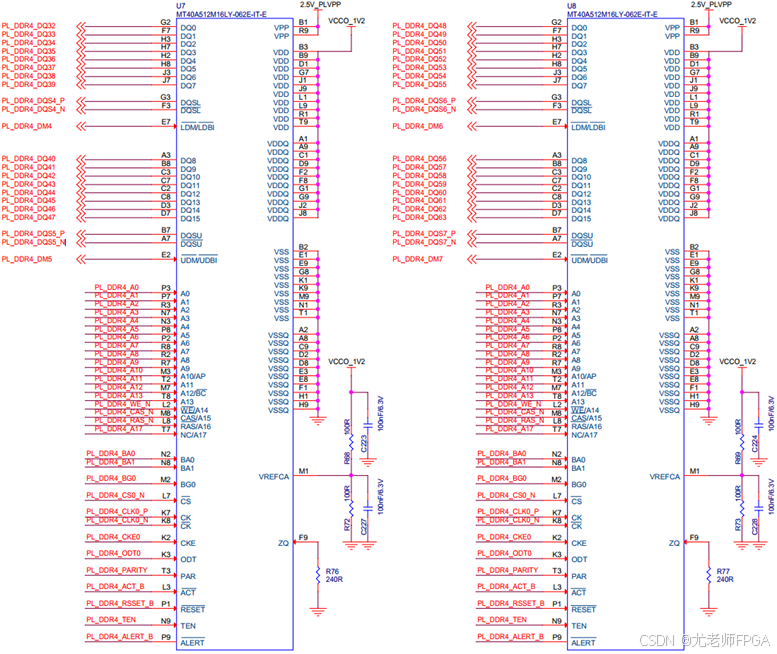

下图为DDR4需要连接到顶层的接口,需要链接到管脚。

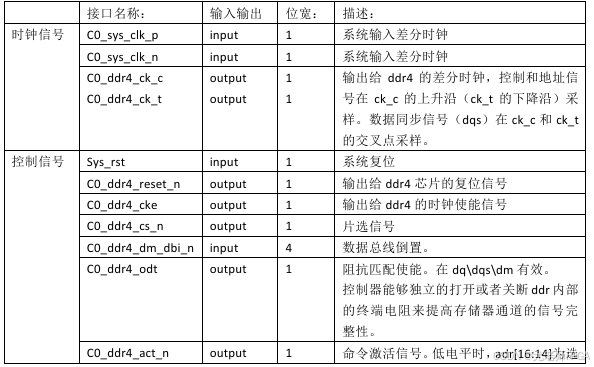

顶层接口描述:

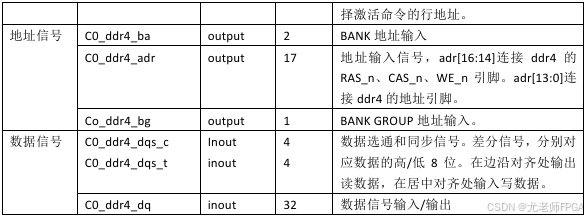

以上接口分为时钟信号、控制信号、地址信号、数据信号。

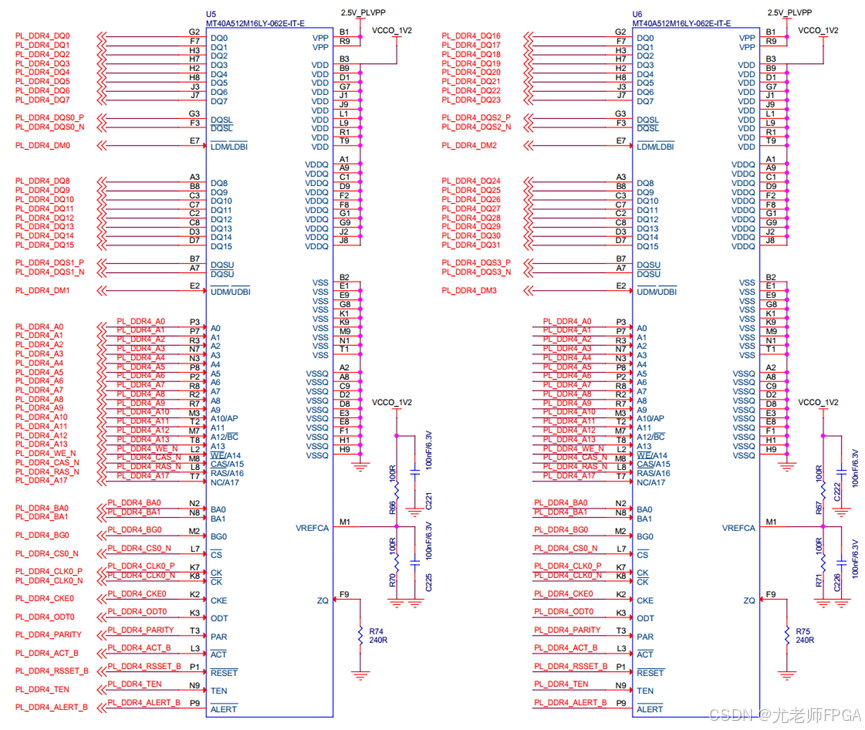

DDR4原理图。核心模块在PL侧搭载了4片镁光(Micron)的DDR4内存,单片内存大小为1GB,数据接口16bit。通过4片内存级联后,可存储4GB数据,数据接口为64bit。

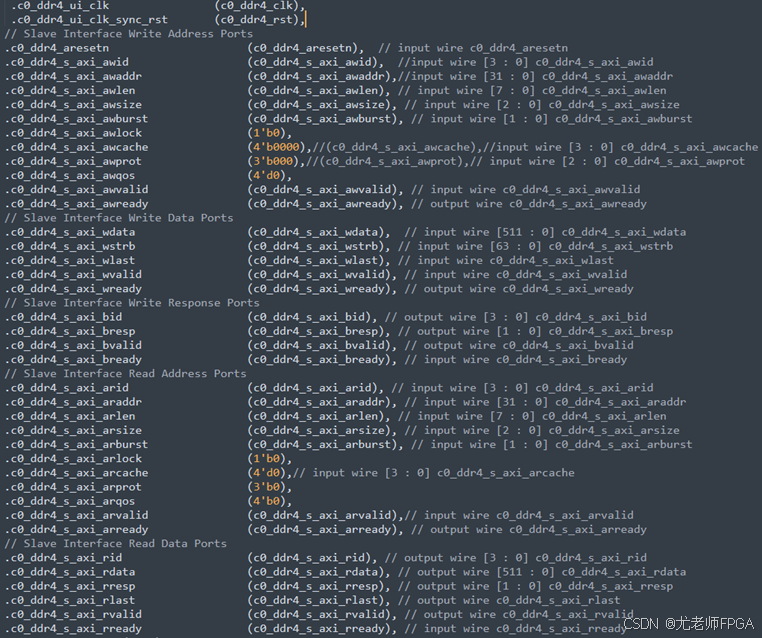

本案例中用户接口为AXI4接口时序。

通道接口定义:

ddr4 主机AXI4接口定义:

其他信号说明:

awlock(arlock):访问类型(1bits):0为正常访问。

awcache(arcache):内存类型(4bits):面命一次传输是怎样通过系统的。4’b0000为不缓存和不缓冲。

awprot(arprot):保护水平及安全等级(3bits):3’b000为普通访问。

awqos(arqos):服务质量(4bits),该信号用于优先级声明信号,值越高代表优先级越高。

说明:ddr4 ip 接口的awlock、awcache、awprot、awqos、arlock、arcache、arprot、arqos信号在工程中没有特别要求,可以设置为0。ddr4 ip为从机,我们实现的是主机的信号接收和传输。

初始化成功信号:

init_calib_complete信号为高电平时,表明DDR4的初始化和校准工作已经全部完成。在FPGA逻辑处理中,只有当这个信号处于高电平状态,才能对DDR4进行读写操作,否则将无法正常执行DDR4的读写任务,甚至可能导致操作失败。同时,该信号也扮演着辅助验证硬件DDR4检测的重要角色。

8854

8854

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?