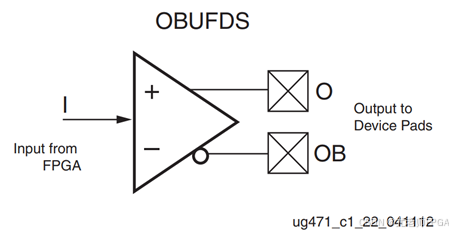

前面一讲说到差分信号用于信号传输输入到FPGA内部处理时,需要使用IBUFDS原语将外部的差分信号变为单端使用,而如果FPGA想要输出差分信号,那么就需要将内部的单端信号转为差分信号输出,这个操作需要使用到OBUFDS原语去实现。

OBUFDS原语:

OBUFDS是差分输出缓存原语,用于将单端信号I转换成差分信号正端O和负端OB,O和OB将输出到焊盘上输出到外部;

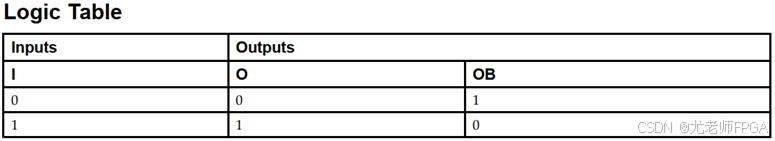

上图为原语的真值表,

I输入0值,O输出0,OB输出1;

I输入1值,O输出1,OB输出0;

可以看到,输出的正端与输入相同,输出的负端与输入相反;

原语的例化形式如下:

7系器件:

OBUFDS #(

.IOSTANDARD(“DEFAULT”), // Specify the output I/O standard

.SLEW(“SLOW”) // Specify the output slew rate

) OBUFDS_inst (

.O(O), // Diff_p output (connect directly to top-level port)

.OB(OB), // Diff_n output (connect directly to top-level port)

.I(I) // Buffer input

);

Ultrascale+器件:

OBUFDS OBUFDS_inst (

.O(O), // 1-bit output: Diff_p output (connect directly to top-level port)

.OB(OB), // 1-bit output: Diff_n output (connect directly to top-level port)

.I(I) // 1-bit input: Buffer input

);

可以看到两个原语的端口一致,不过7系的原语同样比Ultrascale+系多两个参数;

参数说明:

参数IOSTANDARD:差分输出管脚使用的电平标准。

常见值有:

“LVDS_25”:LVDS差分信号,1.25V共模电压(默认值,Bank供电电压为2.5V)。

“LVDS”:LVDS差分信号,1.25V共模电压(默认值, Bank供电电压为1.8V)。

“DEFAULT”:自动适配Bank默认电平,但需确保FPGA Bank供电与外部信号匹配。

参数SLEW:控制输出信号的压摆率(Slew Rate),控制输出信号电压从逻辑0(1)变到逻辑1(0)的速度,影响信号边沿的陡峭程度;

可选值:

“SLOW”:降低信号边沿变化速度,减少电磁干扰;

“FAST”:提高信号边沿速度,适用于高频信号,但是过快的变化可能会增加噪声;

一般默认值设置为“SLOW”以降低电磁干扰;

当信号频率过高,如大于100MHz,为了时序不出问题,可能就需要将其设置为“FAST”去满足高频信号的时序要求;

但在一些电磁干扰比较敏感的场合,例如医疗设备、汽车电子等场景,优先使用“SLOW”;

其中差分的输出端口需直接连接到顶层的输出端口;

关于Ultrascale+器件的参数控制则在XDC中可以约束控制;

set_property IOSTANDARD LVDS_25 [get_ports {O OB}]

set_property SLEW SLOW [get_ports {O OB}]

IBUFDS原语仿真;

测试模块:

module top_7series_obufds(

input wire clk,

input wire rst,

input wire din,

output wire dout_p,

output wire dout_n

);

OBUFDS #(

.IOSTANDARD(“DEFAULT”), // Specify the output I/O standard

.SLEW(“SLOW”) // Specify the output slew rate

) OBUFDS_inst (

.O(dout_p), // Diff_p output (connect directly to top-level port)

.OB(dout_n), // Diff_n output (connect directly to top-level port)

.I(din) // Buffer input

);

endmodule

testbench:

设置1个随机的信号输入,然后仿真查看单端转差分原语对于输入的处理结果,其中每100ns产生随机的输入;

`timescale 1ns / 1ps

module tb;

reg clk;

reg rst;

reg data;

wire dout_p;

wire dout_n;

initial begin

clk = 0;

rst = 1;

#100

rst = 0;

end

always #50 clk = ~clk;

initial begin

data = 0;

while(1)begin

#100

data = $random;

end

end

top_7series_obufds inst_top_7series_obufds (

.clk(clk),

.rst(rst),

.din(data),

.dout_p(dout_p),

.dout_n(dout_n)

);

endmodule

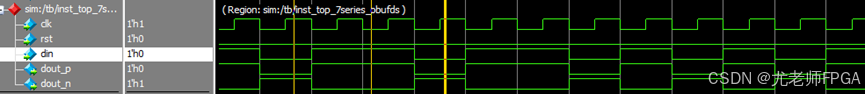

仿真结果:

可以看到,

在第1个黄线处,data输入0,dout_p输出0,dout_n输出1,输出正确;

在第2个黄线处,data输入1,dout_p输出1,dout_n输出0,输出正确;

在第3个黄线处,data输入0,dout_p输出0,dout_n输出1,输出正确;

可以看到仿真波形,data_p与data相同,data_n与data相反,仿真的结果符合原语的特性;

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?