library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity fenpin is

port(

clk:in std_logic;

q:out std_logic

);

end;

architecture b1 of fenpin is

signal q1,q2:std_logic;

signal count:std_logic_vector(7 downto 0);

begin

process(clk)

begin

if (clk'event and clk='1')then

if(count ="01100011")then

count <= (others => '0');

q1 <= not q1;

else count<=count+1;

end if;

end if;

end process;

q <= q1;

end;

代码类型竟然没有VHDL。。。

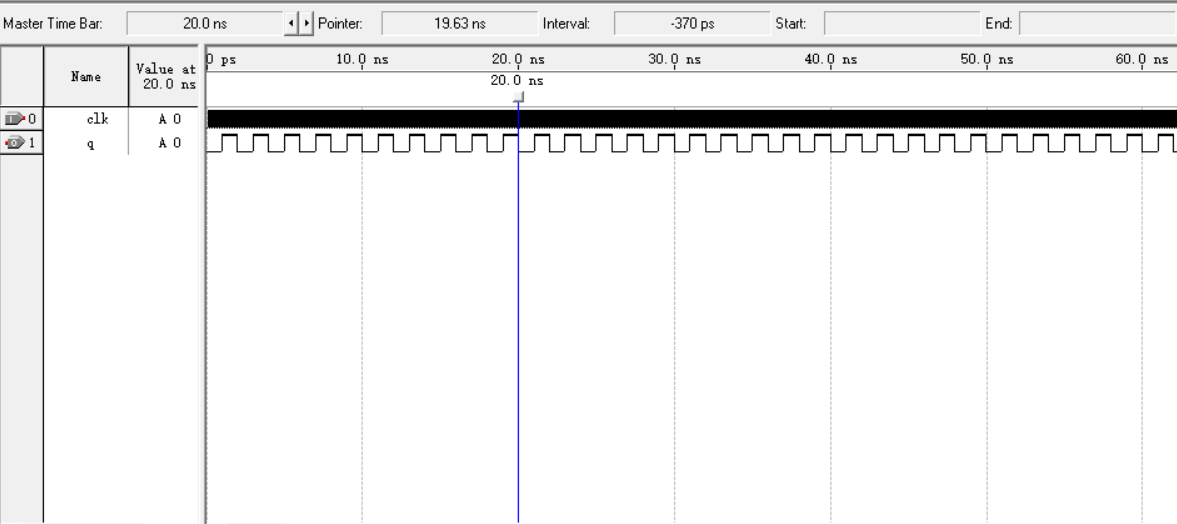

上边的代码就是一个分频器,200分频,时序仿真始终没结果,换成功能仿真就好了

外部时钟等等这里就不提了,直接说解决方案

解决方案1:

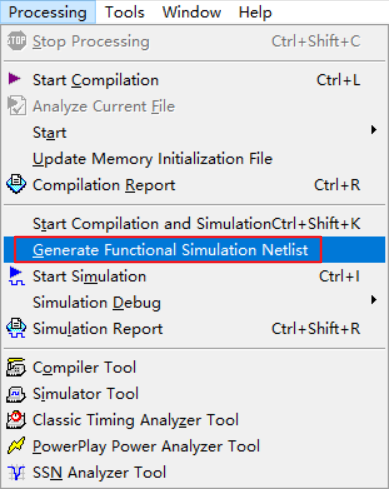

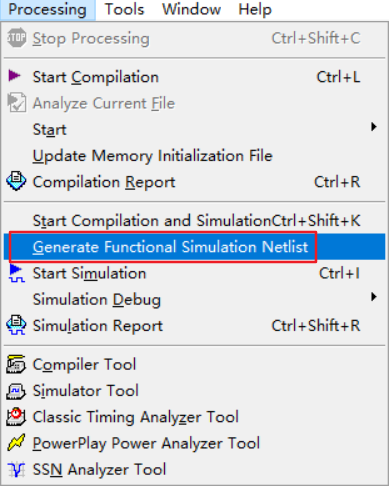

首先Generate Functional Simulation Netlist,生成功能仿真的网格

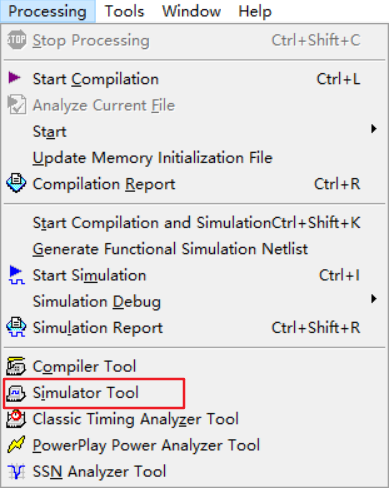

然后选择Simlation Tool

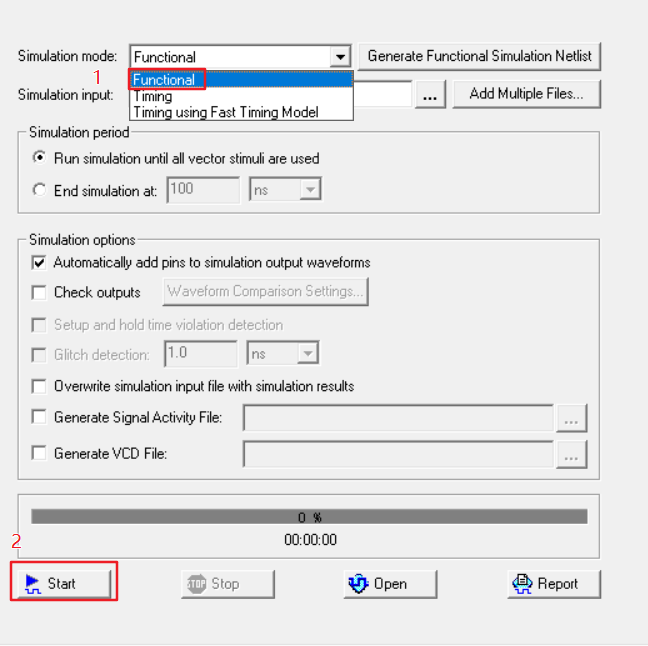

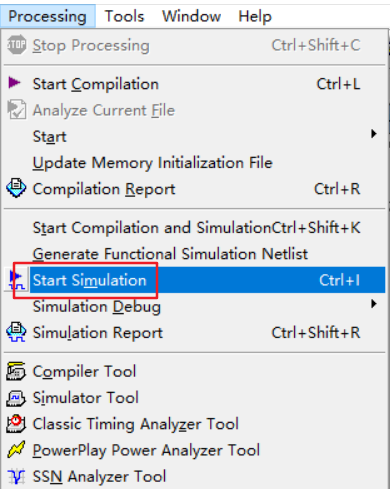

选择Functional ,然后点击START

然后就有结果了

方法2:

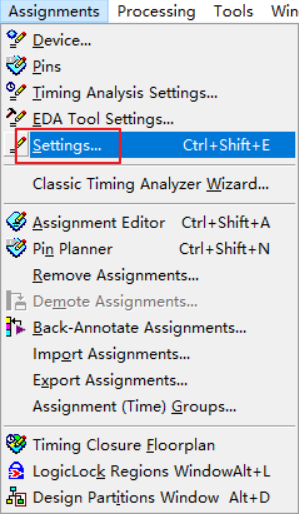

Assignments -- setttings

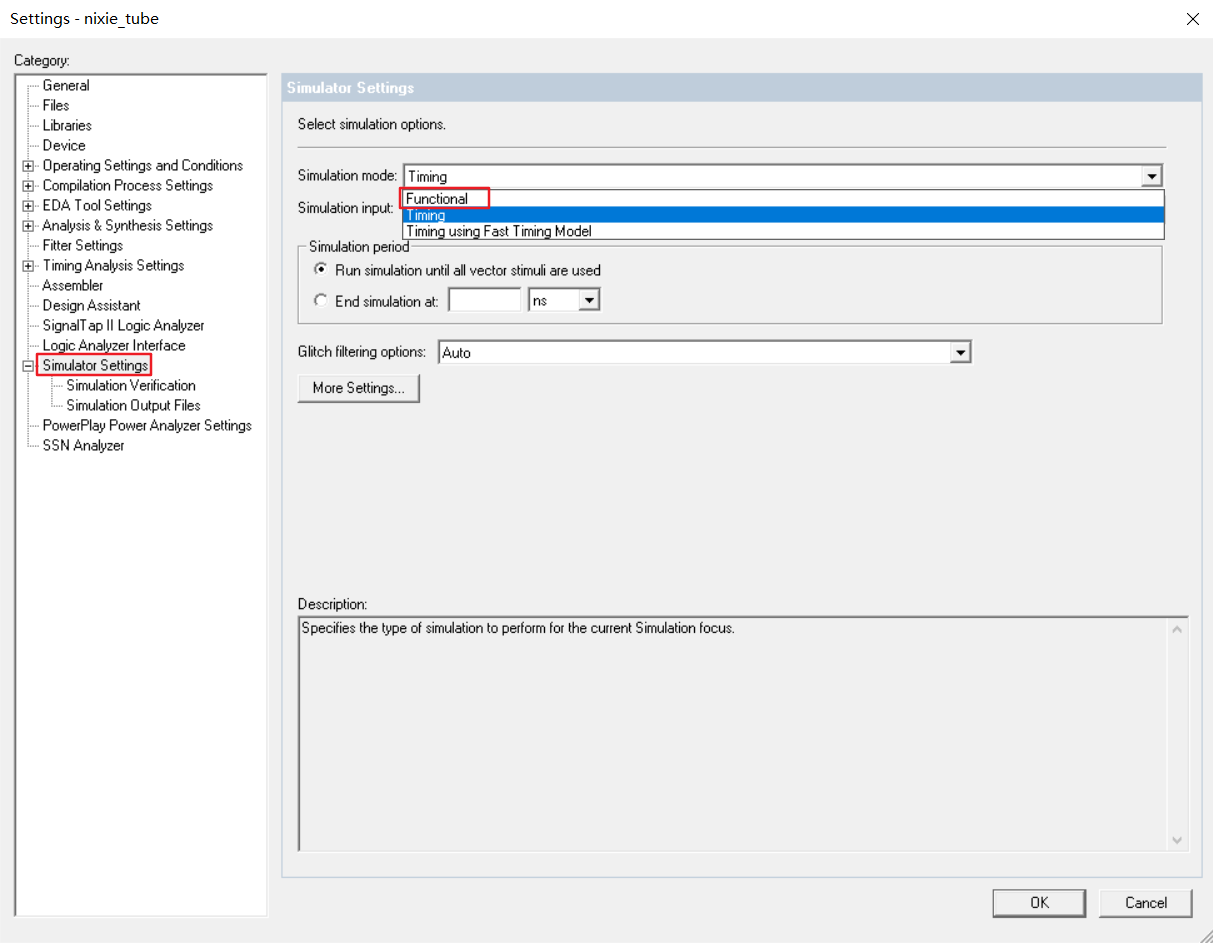

simulation settings -- functional

processing -- Generate Functional Simulation Netlist

start simulation

然后就OK了

本文介绍了一个基于VHDL的200分频器设计,并详细记录了在时序仿真遇到问题后的解决过程。通过两种方法成功进行功能仿真,包括生成功能仿真网格及设置仿真工具。

本文介绍了一个基于VHDL的200分频器设计,并详细记录了在时序仿真遇到问题后的解决过程。通过两种方法成功进行功能仿真,包括生成功能仿真网格及设置仿真工具。

803

803

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?