1.3.1 编码器

4输入2输出编码器代码如下

View Code

View Code

1 module encoder

2 (

3 input [3:0] iA,

4 output reg [1:0] oQ

5 );

6

7 always @(*)

8 begin

9 oQ=2'b00;

10 case(iA)

11 4'b0001:oQ=2'b00;

12 4'b0010:oQ=2'b01;

13 4'b0100:oQ=2'b10;

14 4'b1000:oQ=2'b11;

15 default :;

16 endcase

17 end

18

19 endmodule

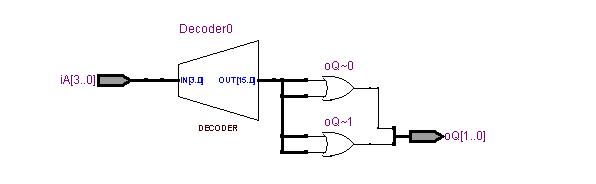

RTL级视图如下

testbench代码如下

View Code

View Code

1 `timescale 1ns/1ns

2 module encoder_tb;

3

4 reg [3:0] ia;

5 wire [1:0] oq;

6

7 initial

8 begin

9 ia=4'b0000;

10 #20 ia=4'b0001;

11 #20 ia=4'b0010;

12 #20 ia=4'b0100;

13 #20 ia=4'b1000;

14 #20 $stop;

15 end

16

17 encoder encoder_inst

18 (

19 .iA(ia),

20 .oQ(oq)

21 );

22

23 endmodule

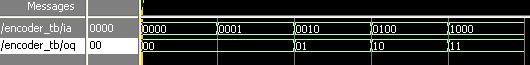

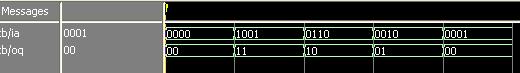

RTL级仿真波形如下

1.3.2 优先编码器

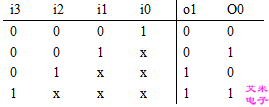

真值表如下,参考艾米电子

代码如下

View Code

View Code

1 module encoder

2 (

3 input [3:0] iA,

4 output reg [1:0] oQ

5 );

6

7 always @(*)

8 begin

9 oQ=2'b00;

10 if(iA[3])oQ=2'b11;

11 else if(iA[2])oQ=2'b10;

12 else if(iA[1])oQ=2'b01;

13 else oQ=2'b00;

14 end

15

16 endmodule

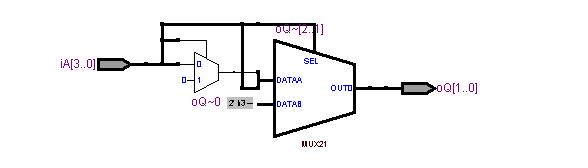

RTL级视图

RTL级仿真波形

1.3.3 译码器

通过case语句很容易实现如数码管等译码电路。

本文详细介绍了编码器和译码器的设计方法,包括4输入2输出编码器及优先编码器的Verilog代码实现,并提供了RTL级视图与仿真波形。同时,还展示了如何利用case语句实现译码器。

本文详细介绍了编码器和译码器的设计方法,包括4输入2输出编码器及优先编码器的Verilog代码实现,并提供了RTL级视图与仿真波形。同时,还展示了如何利用case语句实现译码器。

5306

5306

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?