最近做了个NVME4.0的一致性测试夹具如下图,SFF8639接口,PCIE的传输模式,现在捋一捋这三位啥关系。

先说接触最广的PCIE,这个不难理解,这个是总线标准,X1,X4,X8,X16,外形啥样,当然是金手指,但是左边那个金手指好像不是PCIE的接口,这个时候就要来说SFF8639,其实这个SFF8639就是我们经常说的U.2接口,不用解释,看着就是给硬盘用的。

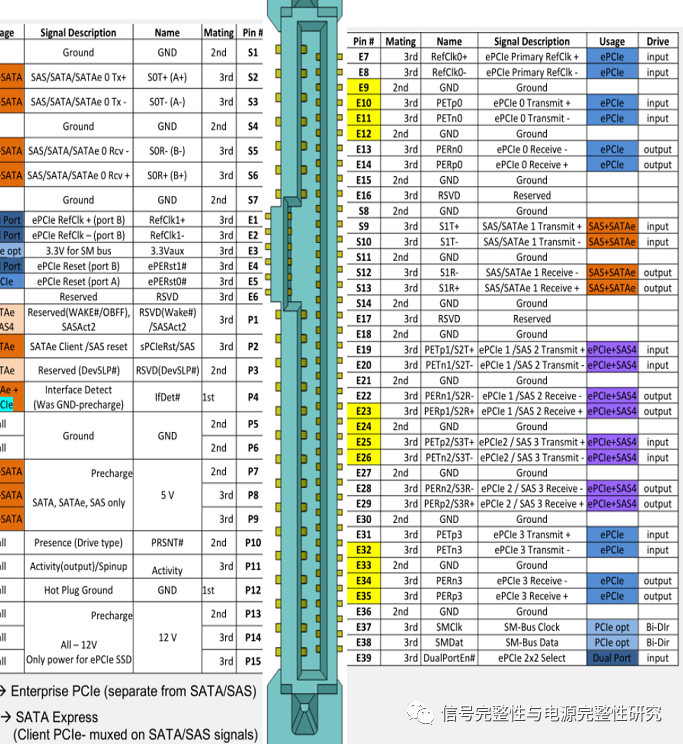

为什么它和PCIE扯上关系,我们看下接口定义

有管脚定义是ePCIE Transmit或者receiver,这也就是PCIE协议的传输通道,所以在这里SFF8639是个接口,可以通过这个接口走PCIE的信号,一点不矛盾。你也可以把这个接口换成M.2或者直接换成PCIE的金手指,没任何问题,无非就是外形变了,走的还可以是PCIE信号,不止如此,我们看信号定义发现它也支持SAS。

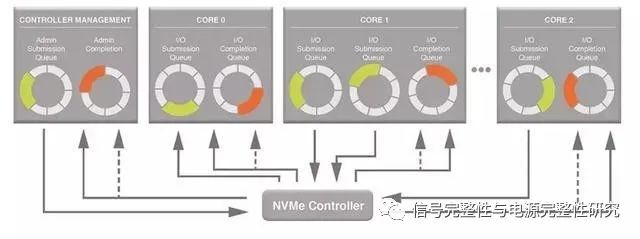

最后来说NVME,NVME其实是个通信协议,全称是Nonvolatile Memory Express(非易失性存储),听名字就知道是个软件东东,所以你可以把它和硬件分开。

从图上看到,它本质是上建立了多个计算机与存储设备的通路,这样搬运数据的速度自然就提高了。在NVMe协议中,多个通路其实就是多个队列,而在SATA中计算机与存储设备只能有一个队列,即使是多CPU情况下,所有请求只能经过这样一个狭窄的道路。而NVMe协议可以最多有64K个队列,每个CPU或者核心都可以有一个队列,这样并发程度大大提升,性能也自然更高了。

好了,基本都搞明白了吧,是不是1+1+1>3呢,买SSD的时候不要被坑哦!

本文介绍了NVME、PCIE和U.2(SFF8639)之间的关系。PCIE是一种总线标准,SFF8639即U.2接口,常用于硬盘,可传输PCIE信号。NVME是一种高速非易失性存储协议,通过建立多个队列提高数据传输速度。理解这些概念有助于选择合适的SSD存储设备。

本文介绍了NVME、PCIE和U.2(SFF8639)之间的关系。PCIE是一种总线标准,SFF8639即U.2接口,常用于硬盘,可传输PCIE信号。NVME是一种高速非易失性存储协议,通过建立多个队列提高数据传输速度。理解这些概念有助于选择合适的SSD存储设备。

1577

1577

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?