中断技术概述

中断系统作用:实时测控,单片机能及时地响应和处理单片机外部事件或内部事件所提出的中断请求。

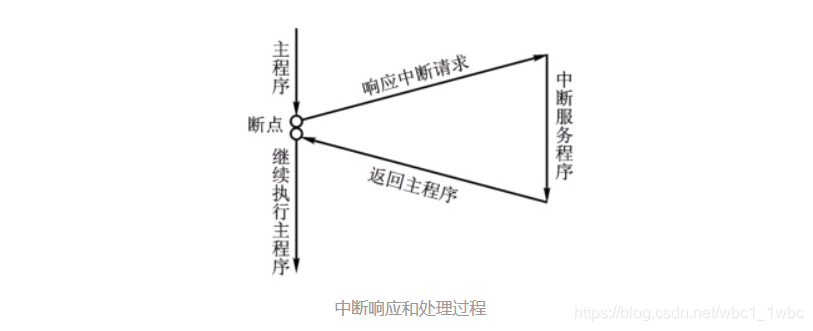

中断的概念:CPU正在执行程序时,单片机外部或内部发生的某一事件,请求CPU迅速去处理。CPU暂时中止当前的工作,转到中断服务处理程序处理所发生的事件。处理完该事件后,再回到原来被中止的地方,继续原来的工作,这称为中断。 CPU处理事件的过程,称为CPU的中断响应过程。

能够实现中断处理功能的部件称为中断系统;产生中断的请求源称为中断请求源。中断源向CPU提出的处理请求,称为中断请求(或中断申请)。

能够实现中断处理功能的部件称为中断系统;产生中断的请求源称为中断请求源。中断源向CPU提出的处理请求,称为中断请求(或中断申请)。

进入中断→保护现场→中断处理 → 恢复现场 →中断返回

中断方式优点:大大地提高了CPU的工作效率。

中断系统结构

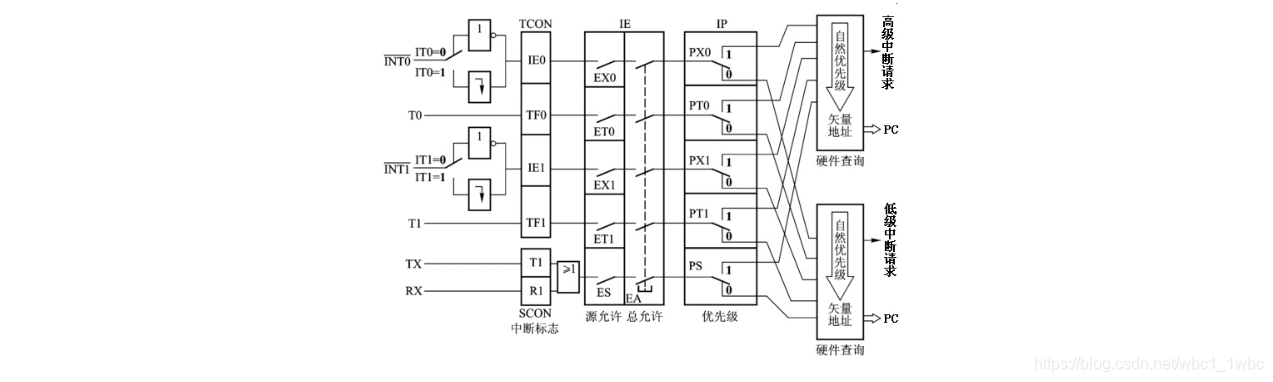

中断系统结构见图。中断系统有5个中断请求源(简称中断源),2个中断优先级,可实现2级中断服务程序嵌套。每一中断源可用软件独立控制为允许中断或关闭中断状态;每一个中断源的优先级均可用软件设置。

中断系统结构见图。中断系统有5个中断请求源(简称中断源),2个中断优先级,可实现2级中断服务程序嵌套。每一中断源可用软件独立控制为允许中断或关闭中断状态;每一个中断源的优先级均可用软件设置。

中断请求源

由图,中断系统共有5个中断请求源,它们是:

(1)INT0*—外部中断请求0,外部中断请求信号(低电平或负跳变有效)由INT0引脚输入,中断请求标志为IE0。

(2)INT1—外部中断请求1,外部中断请求信号(低电平或负跳变有效)由INT1*引脚输入,中断请求标志为IE1。

(3)定时器/计数器T0计数溢出的中断请求,标志为TF0。

(4)定时器/计数器T1计数溢出的中断请求,标志为TF1。

(5)串行口中断请求,标志为发送中断TI或接收中断RI。

中断请求标志寄存器

5个中断请求源的中断请求标志分别由特殊功能寄存器TCON和SCON相应位锁存。

1.TCON寄存器

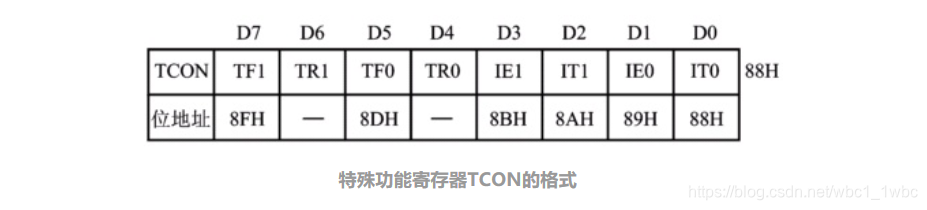

为定时器/计数器的控制寄存器,字节地址为88H,可位寻址。既包括定时器/计数器T0、T1溢出中断请求标志位TF0和TF1,也包括两个外部中断请求的标志位IE1与IE0,还包括两个外部中断请求源的中断触发方式选择位。TCON格式见图。

TCON寄存器中与中断系统有关各标志位功能如下:

(1)TF1—定时器/计数器T1的溢出中断请求标志位。当启动T1计数后,T1从初值开始加1计数,当最高位产生溢出时,硬件 置TF1为“1”,向CPU申请中断,响应TF1中断时,TF1标志硬件自动清“0”,TF1也可由软件清“0”。

(2)TF0—定时器/计数器T0溢出中断请求标志位,与TF1类似。

(3)IE1—外部中断请求1中断请求标志位。

(4)IE0—外部中断请求0中断请求标志位,与IE1类似。

(5)IT1—选择外中断请求1为跳沿触发还是电平触发方式。0–电平触发方式,加到INT0脚上的外中断请求输入信号为低电平有效,并把IE1置“1”。转向中断服务程序时,则由硬件自动把IE1清“0”。1–跳沿触发方式,加到INT1脚上的外中断请求输入信号从高到低的负跳变有效,并把IE1置“1”。转向中断服务程序时,则由硬件自动把IE1清“0”。

(6)IT0—选择外中断请求0为跳沿触发方式还是电平触发方式,与IT1类似。 当AT89S51复位后,TCON被清“0”,5个中断源的中断请求标志均为0。

TR1(D6位)、TR0(D4位)这2位与中断系统无关,仅与定时器/计数器T1和T0有关,将在定时器/计数器中介绍。

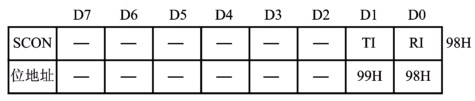

SCON寄存器

串行口控制寄存器,字节地址为98H,可位寻址。SCON的低二位锁存串口的发送中断和接收中断的中断请求标志TI和RI,格式见上图。

SCON标志位功能:

(1)TI—串口发送中断请求标志位。CPU将1字节的数据写入串口的发送缓冲器SBUF时,就启动一帧串行数据的发送,每发送完一帧串行数据后,硬件使TI自动置“1”。CPU响应串口发送中断时,并不清除TI中断请求标志,TI标志必须在中断服务程序中用指令对其清“0”。

(2)RI—串行口接收中断请求标志位。在串口接收完一个串行数据帧,硬件自动使RI中断请求标志置“1”。CPU在响应串口接收中断时,RI标志并不清“0”,须在中断服务程序中用指令对RI清“0”。

中断允许与中断优先级的控制

实现中断允许控制和中断优先级控制分别中断允许寄存器IE和中断优先级寄存器IP实现。下面介绍两个特殊功能寄存器。

中断允许寄存器IE

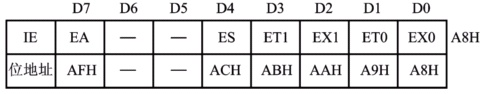

各中断源开放或屏蔽,是由片内中断允许寄存器IE控制。IE字节地址为A8H,可进行位寻址,格式见图。

IE对中断开放和关闭实现两级控制。两级控制就是有一个总的中断开关控制位EA(IE.7位),当EA=0,所有中断请求被屏蔽,CPU对任何中断请求都不接受;当EA=1时,CPU开中断,但5个中断源的中断请求是否允许,还要由IE中的低5位所对应的5个中断请求允许控制位的状态来决定。IE中各位的功能如下:

(1)EA—中断允许总开关控制位。EA=0,所有的中断请求被屏蔽。EA=1,所有的中断请求被开放。

(2)ES—串行口中断允许位。ES=0,禁止串行口中断。ES=1,允许串行口中断。

(3)ET1—定时器/计数器T1溢出中断允许位。ET1=0,禁止T1溢出中断。ET1=1,允许T1溢出中断。

(4)EX1—外部中断1中断允许位。EX1=0,禁止外部中断1中断。EX1=1,允许外部中断1中断。

(5)ET0—定时器/计数器T0的溢出中断允许位。ET0=0,禁止T0溢出中断。ET0=1,允许T0溢出中断。

(6)EX0—外部中断0中断允许位。EX0=0,禁止外部中断0中断。EX0=1,允许外部中断0中断。AT89S51复位后,IE被清“0”,所有中断请求被禁止。

IE中与各个中断源相应位可用指令置“1”或清“0”,即可允许或禁止各中断源的中断申请。若使某一个中断源被允许中断,除了IE相应位被置“1”外,还必须使EA位置“1”。

可由位操作指令来实现,即:SETB bit;CLR bit。

例如: 若允许片内2个定时器/计数器中断,禁止其它中断源的中断请求。编写设置IE的相应程序段

(1)用位操作指令来编写如下程序段:CLR ES ;

禁止串行口中断 CLR EX1 ;

禁止外部中断1中断CLR EX0 ;

禁止外部中断0中断SETB ET0 ;

允许定时器/计数器T0中断SETB ET1 ;

允许定时器/计数器T1中断SETB EA ;

CPU开中断

(2)用字节操作指令来编写: MOV IE,#8AH

或者用: MOV 0A8H,#8AH ;

A8H为IE寄存器字节地址

中断优先级寄存器IP

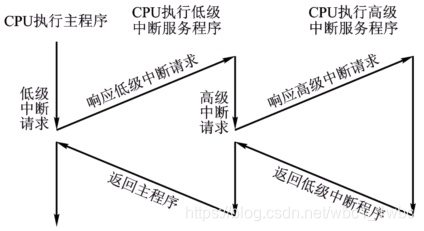

中断请求源有两个中断优先级,每一个中断请求源可由软件设置为高优先级中断或低优先级中断,也可实现两级中断嵌套。 所谓两级中断嵌套,就是AT89S51正在执行低优先级中断的服务程序时,可被高优先级中断请求所中断,待高优先级中断处理完毕后,再返回低优先级中断服务程序。两级中断嵌套见图:

各中断源的中断优先级关系,可归纳为下面两条基本规则:

各中断源的中断优先级关系,可归纳为下面两条基本规则:

(1)低优先级可被高优先级中断,高优先级不能被低优先级中断。

(2)任何一种中断(不管是高级还是低级)一旦得到响应,不会再被它的同级中断源所中断。如果某一中断源被设置为高优先级中断,在执行该中断源的中断服务程序时,则不能被任何其他的中断源的中断请求所中断。

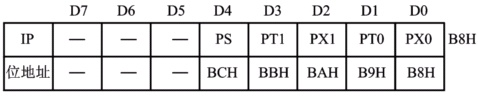

AT89S51片内有一个中断优先级寄存器IP,字节地址为B8H,可位寻址。只要用程序改变其内容,即可进行各中断源中断优先级设置,IP寄存器格式见图。

中断优先级寄存器IP各位含义:

中断优先级寄存器IP各位含义:

(1)PS—串行口中断优先级控制位,1—高级;0—低级。

(2)PT1—T1中断优先级控制位,1—高级;0—低级。

(3)PX1—外部中断1中断优先级控制位,1—高级;0—低级。

(4)PT0—T0中断优先级控制位,1—高级;0—低级。

(5)PX0—外部中断0中断优先级控制位,1—高级;0—低级。

中断优先级控制寄存器IP各位都可由程序置“1”和清“0”,用位操作指令或字节操作指令可更新IP的内容,改变各中断源的中断优先级。AT89S51复位后,各中断源均为低优先级中断。IP内容为00。

响应中断请求的条件

一个中断源中断请求被响应,须满足以下必要条件:

(1)总中断允许开关接通,即IE寄存器中的中断总允许位EA=1。

(2)该中断源发出中断请求,即该中断源对应的中断请求标志为“1”。(3)该中断源的中断允许位=1,即该中断被允许。

(4)无同级或更高级中断正在被服务。

中断响应就是CPU对中断源提出的中断请求的接受,当查询到有效的中断请求时,满足上述条件时,紧接着就进行中断响应。

中断响应过程:首先由硬件自动生成一条长调用指令“LCALL addr16”。即程序存储区中相应的中断入口地址。例如,对于外部中断1的响应,硬件自动生成的长调用指令为:

LCALL 0013H

生成LCALL指令后,紧接着就由CPU执行该指令。首先将程序计数器PC内容压入堆栈以保护断点,再将中断入口地址装入PC,使程序转向响应中断请求的中断入口地址。各中断源服务程序入口地址是固定的,见表

其中两个中断入口间只相隔8字节,一般情况下难以安放一个完整的中断服务程序。

其中两个中断入口间只相隔8字节,一般情况下难以安放一个完整的中断服务程序。

中断响应是有条件的,遇到下列三种情况之一时,中断响应被封锁: (1)CPU正在处理同级的或更高优先级的中断。

(2)所查询的机器周期不是所当前正在执行指令的最后一个机器周期。只有在当前指令执行完毕后,才能进行中断响应。

(3)正在执行的指令是RETI或是访问IE或IP的指令。需要再去执行完一条指令,才能响应新的中断请求。

如果存在上述三种情况之一,CPU将丢弃中断查询结果,不能对中断进行响应。

外部中断的响应时间

外部中断的最短的响应时间为3个机器周期:

(1)中断请求标志位查询占1个机器周期。

(2)子程序调用指令LCALL转到相应的中断服务程序入口,需2个机器周期。

外部中断响应的最长时间为8个机器周期:发生在CPU进行中断标志查询时,刚好是开始执行RETI或是访问IE或IP的指令,则需把当前指令执行完再继续执行一条指令后,才能响应中断,最长需2个机器周期。接着再执行一条指令,按最长指令(乘法指令MUL和除法指令DIV)来算,也只有4个机器周期。加上硬件子程序调用指令LCALL的执行,需要2个机器周期。所以,外部中断响应最长时间为8个机器周期。 如果已在处理同级或更高级中断,响应时间无法计算。在一个单一中断的系统里,MCS-51单片机对外部中断请求的响应的时间总是在3~8个机器周期之间。

外部中断的触发方式选择

两种触发方式:电平触发方式和跳沿触发方式。

(1)电平触发方式

CPU在每个机器周期采样到的外部中断输入线的电平。在中断服务程序返回之前,外部中断请求输入必须无效(即变为高电平),否则CPU返回主程序后会再次响应中断。适于外中断以低电平输入且中断服务程序能清除外部中断请求(即外部中断输入电平又变为高电平)的情况。

(2)跳沿触发方式

连续两次采样,一个机器周期采样到外部中断输入为高,下一个机器周期采样为低,则置“1”中断请求标志,直到CPU响应此中断时,该标志才清0。这样不会丢失中断,但输入的负脉冲宽度至少保持1个机器周期。

中断请求的撤消

1.定时器/计数器中断请求的撤消

中断请求被响应后。硬件会自动清TF0或TF1。

2.外部中断请求的撤销

(1)跳沿方式外部中断请求的撤消是自动撤消的。

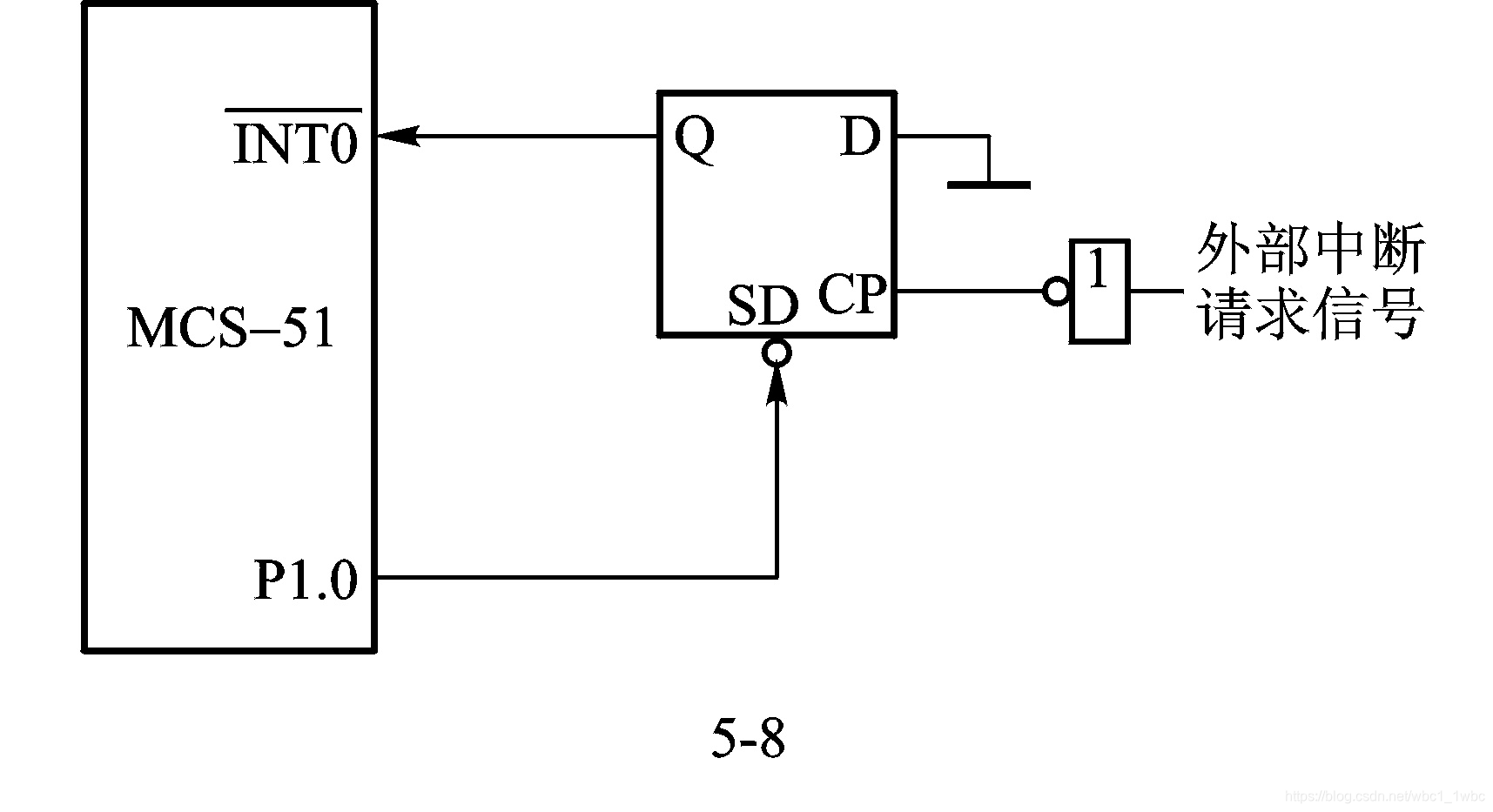

(2)电平方式外部中断请求的撤消。除了标志位清“0”之外,还需在中断响应后把中断请求信号引脚从低电平强制改变为高电平,如下图所示。

只要P1.0端输出一个负脉冲就可以使D触发器置“1”,从而撤消了低电平的中断请求信号。

只要P1.0端输出一个负脉冲就可以使D触发器置“1”,从而撤消了低电平的中断请求信号。

所需的负脉冲可增加如下两条指令得到:

ORL P1,#01H ;P1.0为“1”

ANL P1,#0FEH ;P1.0为“0”

电平方式的外部中断请求信号的完全撤消,是通过软硬件相结合的方法来实现的。

3.串行口中断请求的撤消

响应串行口的中断后,CPU无法知道是接收中断还是发送中断,还需测试这两个中断标志位的状态,以判定是接收操作还是发送操作,然后才能清除。所以串行口中断请求的撤消只能使用软件的方法

CLR TI ;清TI标志位

CLR RI ;清RI标志位

中断服务程序的设计

一、中断服务程序设计的任务

基本任务:

(1)设置中断允许控制寄存器IE。

(2)设置中断优先级寄存器IP。

(3)对外中断源,是采用电平触发还是跳沿触发。

(4)编写中断服务程序,处理中断请求。

前3条一般放在主程序的初始化程序段中。

例如:假设允许外部中断0中断,并设定它为高级中断,其它中断源为低级中断,采用跳沿触发方式。在主程序中编写如下程序段:

SETB EA ;CPU开中断

SETB ET0 ;允许外中断0产生中断

SETB PX0 ;外中断0为高级中断

SETB IT0 ;外中断0为跳沿触发方式

关于单片机中断系统的更加详细描述此文章属于转载

本文深入解析单片机中断系统的基本概念、中断请求的处理流程及中断服务程序设计。阐述了中断请求源、中断允许与优先级控制、中断响应条件及中断请求撤消等关键环节,帮助读者掌握中断系统的应用技巧。

本文深入解析单片机中断系统的基本概念、中断请求的处理流程及中断服务程序设计。阐述了中断请求源、中断允许与优先级控制、中断响应条件及中断请求撤消等关键环节,帮助读者掌握中断系统的应用技巧。

729

729

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?