最近跟着老师学习Verilog,做了中科大的练习题,将答案记录一下

Q1 输出1

题目描述

编写 Verilog 代码,使电路输出信号1

输入格式

无输入

输出格式

输出1,位宽为1

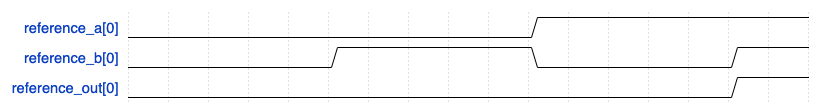

示例波形

代码

module top_module(

output out

);

// Write your code here

wire out;

assign out =1;

endmoduleQ2 输出0

题目描述

编写 Verilog 代码,使电路输出信号0

输入格式

无输入

输出格式

输出0,位宽为1

示例波形

代码

module top_module(

output out

);

// Write your code here

assign out=0;

endmoduleQ3 wire

wire

题目描述

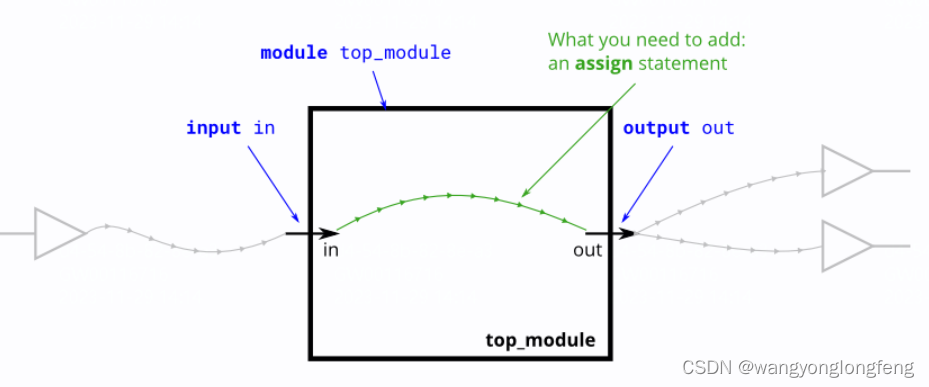

wire 是 Verilog 的关键字,用于表征信号类型的,其含义是线网。wire 可理解为物理连线,但又有所不同,因为 Verilog 中的 wire 是有方向的。例如设计一模块,模块名命名为 top_module,输入信号名为 in,输出信号名为 out,使 in 与 out 直连,如下图所示:

请使用 assign 语句将代码补充完整,使其实现上述电路图的功能。

输入格式 任意

输出格式 与输入完全相同

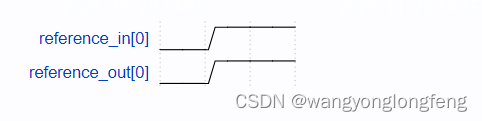

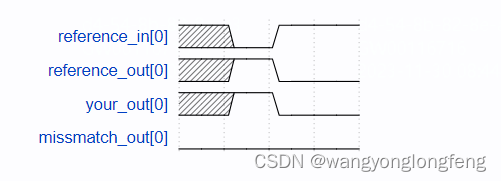

示例波形

代码

module top_module(

input in, output out

);

// Write your code here

assign out = in;

endmoduleQ4 多个端口的模块

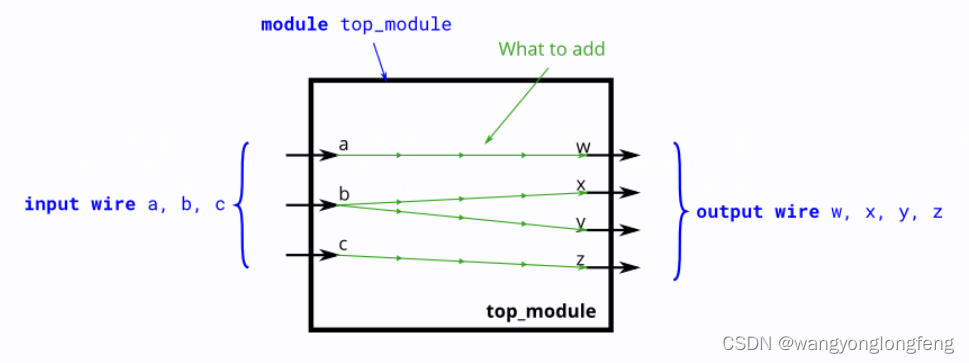

题目描述 wire是Verilog的关键字,用于表征信号类型的,其含义是线网,wire可理解为物理连线,但又有所不同,因为verilog中的wire是有方向的,例如设计一模块,模块名命名为top_module,输入信号名为in,输出信号名为out,使in与out直连,如下图所示:

请使用assign语句将代码补充完整,使其实现上述电路图的功能

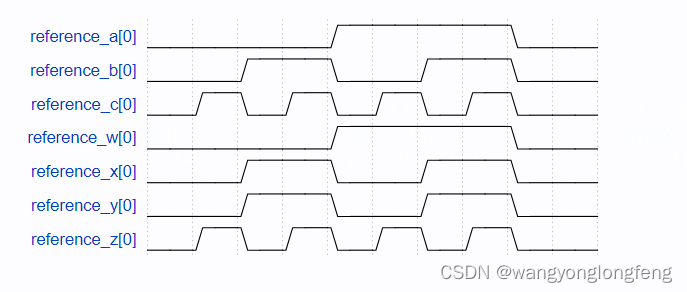

输入格式 1 1 1 输出格式 1 1 1 1 示例波形

代码

module top_module(

input a,b,c,

output w,x,y,z );

// 请用户在下方编辑代码

assign w=a,x=b,y=b,z=c;

//用户编辑到此为止

endmoduleQ5 非门

题目描述 创建一个名为top_module的Verilog模块,实现非门的功能

输入格式 无 输出格式 无 示例波形

代码

module top_module( input in, output out );

// 请用户在下方编辑代码

assign out=~in;

//用户编辑到此为止

endmoduleQ6 与门

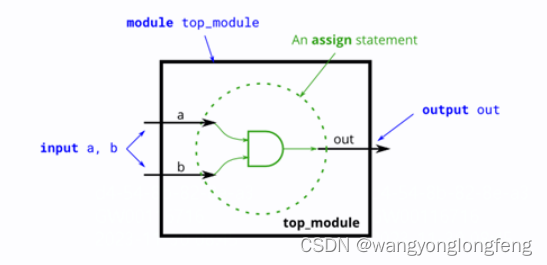

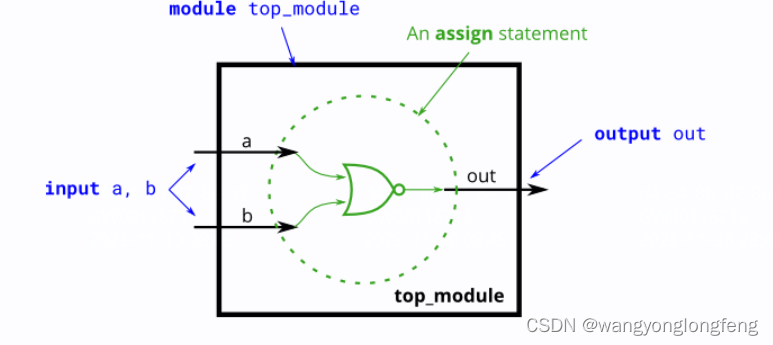

题目描述 创建一个Verilog模块,实现与门的逻辑功能,如下图所示:

输入格式 1bit a, 1bit b 输出格式 1bit out, 为 a and b 的结果 示例波形

代码

module top_module(

input a,

input b,

output out );

// 请用户在下方编辑代码

assign out=a&b;

//用户编辑到此为止

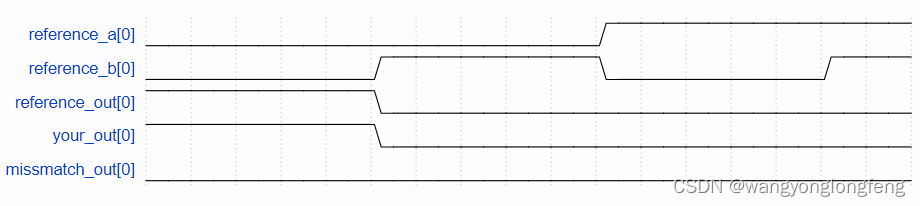

endmoduleQ7 或非门

题目描述 创建一个Verilog模块,实现或非门的逻辑功能,如下图所示:

输入格式 输入a,b均为1位 输出格式 输出out也为1位 示例波形

代码

module top_module(

input a,

input b,

output out );

// 请用户在下方编辑代码

assign out=~(a|b);

//用户编辑到此为止

endmodule

博主跟随老师学习Verilog,记录了中科大练习题的答案。涵盖输出1、输出0、wire使用、逻辑门实现、向量操作、模块例化等多种类型题目,包含各题的题目描述、输入输出格式及对应代码。

博主跟随老师学习Verilog,记录了中科大练习题的答案。涵盖输出1、输出0、wire使用、逻辑门实现、向量操作、模块例化等多种类型题目,包含各题的题目描述、输入输出格式及对应代码。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章