一,vivado硬件环境搭建:

1,修改 CPU 的时钟配置,将 FCLK_CLK2 修改为 65MHz,并将时钟引出两路,提供给两个 AD9226 芯片时钟使用:

2,连接好其余信号,保存,点开 Address Editor,查看地址配置,如果有些模块没有配置地址,

点击 Auto Assign Address。然后Generate Output Products 和 Create HDL Wrapper,在 XDC 中绑定 AD9226 引脚,之后生成 bit文件

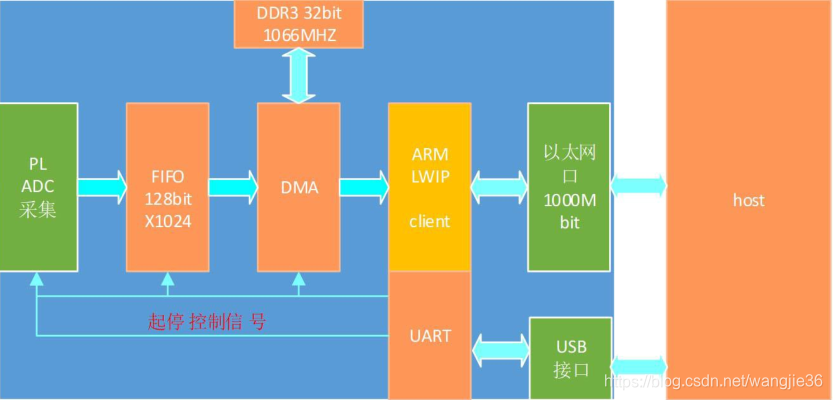

3,整个控制流程:

二,

本文详细介绍了如何在ZYNQ FPGA平台上,通过DMA和AXIS接口实现AD9226 ADC数据采集,并将数据传输至Linux内核。涉及内容包括硬件环境搭建、数据处理流程、块设备访问及内核驱动编写,特别讨论了Linux内核内存管理、设备驱动的内核分离思想以及地址映射方法。

本文详细介绍了如何在ZYNQ FPGA平台上,通过DMA和AXIS接口实现AD9226 ADC数据采集,并将数据传输至Linux内核。涉及内容包括硬件环境搭建、数据处理流程、块设备访问及内核驱动编写,特别讨论了Linux内核内存管理、设备驱动的内核分离思想以及地址映射方法。

订阅专栏 解锁全文

订阅专栏 解锁全文

6277

6277