引言

pipeline流水线设计是一种典型的面积换性能的设计。一方面通过对长功能路径的合理划分,在同一时间内同时并行多个该功能请求,大大提高了某个功能的吞吐率;另一方面由于长功能路径被切割成短路径,可以达到更高的工作频率,如果不需要提高工作频率,多出来的提频空间可以用于降压降功耗,进可攻退可守。今天这篇文章将小小总结一下流水线设计的一些关键点。

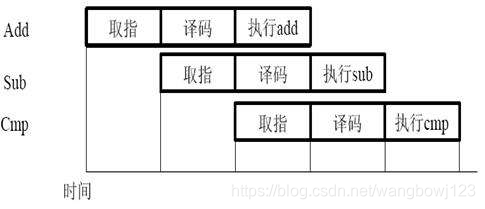

流水线设计是完美的时间并行。因为流水线上每一级的处理都是一个时钟周期的延时,并且一动则全动,每一级的延时可以完美的掩盖起来,最高实现与流水级数相同数量的请求并行度。

如上图所示,在现代经典的cpu处理中,流水线级数被广泛应用,cpu的各个处理环节可以看作流水线上的一个stage。在单发射单处理单元的最简单处理器中,同一时间内最高同时可以支持5条指令的执行。如果没有指令冲突,资源冲突等可能导致断流的场景,基本可以认为每一个时钟周期都可以完成一条指令的处理。

当然,除了CPU,只要是一个周期无法完成的功能,在性能优先的设计中,为了提高吞吐率,都可以采用流水线技术来对功能路径进行切分,比如乘法器等。

流水线的stage划分

我们知道,流水线的分割线是一组寄存器,这条分割线放在哪个位置完全由设计者决定。一般来说,划分流水线的时候主要有以下三点考虑:

-

如果流水线切割的子功能抽象层次较高,最好按完整的功能来进行流水线划分,比如CPU的各个执行环节。

-

流水线最好划分在数据通路上位宽较小的地方,以节省寄存器数量和面积。在流水线上可以有许多的数据路径,数据路径会有中间结果和最终结果。那么这个时候就可以选择性地进行切割。比如一个1024bit 2选1的数据选择器,如果将流水线划分划在选择器的输入端,那么将占用2x1024=2048bit的寄存器以及1个1bit的选择信号。而如果将流水线划分在选择器的输出端,那么只需要1024bit的寄存器,显然面积的收益十分巨大。

-

流水线每一级的关键路径延时最好接近,这样利于获得最大的timing margin,频率可以跑到最高。这点很好理解,假设一条关键路径在切割流水线之前延时为a,时钟周期近似为a,将其切割成2级流水线。假设切割之后的新关键路径仍然在该关键路径上,那么新的时钟周期将取决于切割后的关键路径延时。很明显,a/2是最小的,如果不是均分,那么总有一级大于a/2,那么时钟周期将大于a/2。当然,也有可能切割流水线之前的关键路径被切割之后不再是关键路径。假设一条非关键路径b,在切割之后变成1/3b和2/3b。并且2/3b >1/2a,那么2/3b将会成为新的关键路径,新的时钟周期将接近2/3b。这种情况下,如果对于路径b的这种切割不是必要的(比如出于功能完整性和面积考虑),那么完全可以将b切成1/2b和1/2b,1/2b<1/2a<2/3b,时钟频率依然可以以1/2a为准。

流水线设计的简单例子

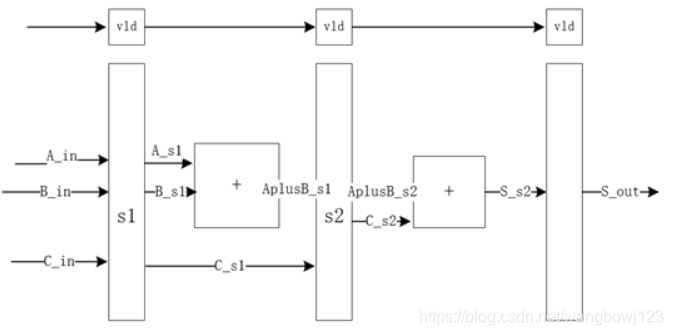

那么怎么设计一个流水线呢?其实从结构上来讲,流水线很简单,无非是一个原本完整的功能,中间插了几级寄存器,每级寄存器的输出做不一样的功能,每一拍都进行一次更新,把上一级的结果打到下一级。比如一个最简单的例子,假设一个周期只能完成一个1bit加法,那么要实现3个操作数加法s=a+b+c,并且保证每个周期都有一个结果寄存器输出,可以使用3级流水实现:

实现代码如下:

`timescale 1ns / 1ps

//==================================================================================================

// Filename : pipeline.v

// Created On : 2020-07-08 18:34:17

// Last Modified : 2020-07-08 19:05:15

// Revision : 1.6

//

// Description :

//

//

//==================================================================================================

module PIPELINE_ADDER#(

parameter DATA_WIDTH = 16

)

(

input clk,

input rst_n,

input [DATA_WIDTH-1:0] a_in ,

input [DATA_WIDTH-1:0] b_in,

input [DATA_WIDTH-1:0] c_in ,

input vld_in,

output reg [DATA_WIDTH-1:0] s_out ,

output reg vld_out

);

// 这里没有必要都定义成reg类型

wire [D

本文深入探讨了流水线设计在提高功能吞吐率和工作频率方面的作用,详细讲解了流水线设计的关键点,包括stage划分的原则,如何处理下游反压信号,以及解决逐级反压串扰的方法。

本文深入探讨了流水线设计在提高功能吞吐率和工作频率方面的作用,详细讲解了流水线设计的关键点,包括stage划分的原则,如何处理下游反压信号,以及解决逐级反压串扰的方法。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+