因最近想通过FPGA把数据从光纤传到PC,借此机会和大家一起学习Aurora、XDMA结合DDR

制作不易,记得三连哦,给我动力,持续更新!!!

完整工程文件下载:XDMA读写DDR工程 提取码:4sxh

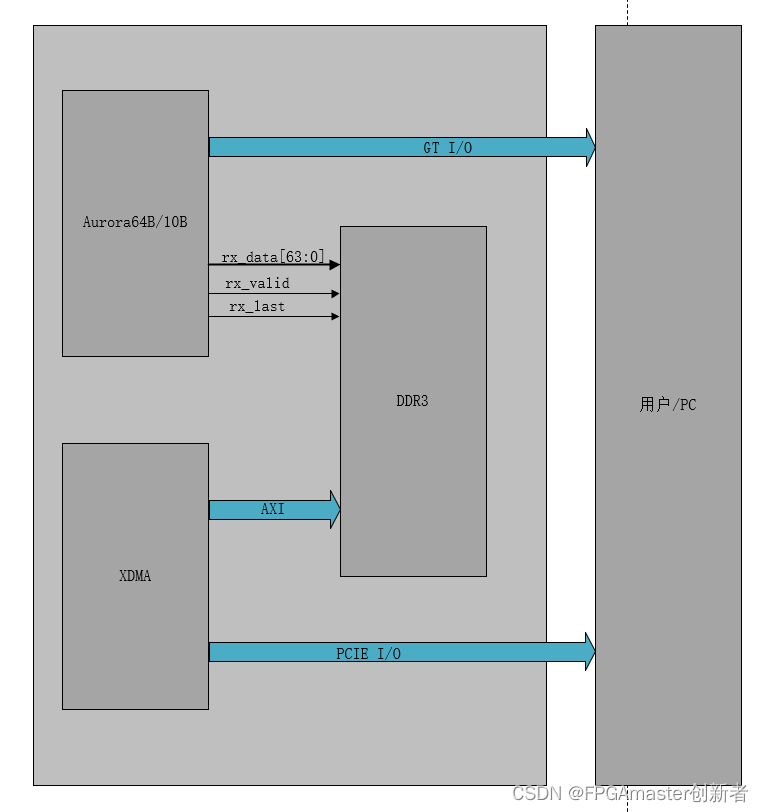

根据前几个章节的学习,已经把DDR、XDMA的相关介绍和设置,已经配置完成了,接下来就再次升华一下,再把一个高速接口Aurora添加进来,完全实现一个 光纤-> PCIE 高速传输通路,此设计适用于各大进行高速数据传输的项目,最大速度可以达到10G。

太多了理论知识,我也不想在这里废话,咱们直接来干货!!

为了此次设计,可以进行下板测试,咱们需要把Aurora的发送和接收连接在一起,然后通过FPGA产生数据,通过Aurora发送,同时Aurora接受过来,然后把数据存储到DDR,并且通过XDMA连接到PCIE,通过XDMA驱动,在主机端读出数据,最终来验证读出来的数据是否和自己产生的数据匹配,通过添加ILA,抓取各个状态的数据状态。

测试环境介绍:

1、FPGA主芯片:zynq7100

2、光纤连接线

3、PCIE主机(Windows10系统)(linux也可以,但是本文采用的Windows)

4、vivado版本:2019.2

一、设计框图

二、设计思路

2.1 Aurora数据产生模块设计

2.1.1 代码设计

此模块就需要借助之前的文章,Aurora的配置说明,不会的小伙伴记得去我的主页翻一下,然后就得到了一个官方的Aurora例子,咱们通过修改这个个例子,进行数据产生、发送、接受,该说不说xilinx真的很良心,再次点赞!!!!

配置介绍:

1、Aurora速度:10.125Gbps

2、Aurora时钟:156.25Mhz

3、接口模式:Framing模式

先分析一下官方例子中的各个模块作用:

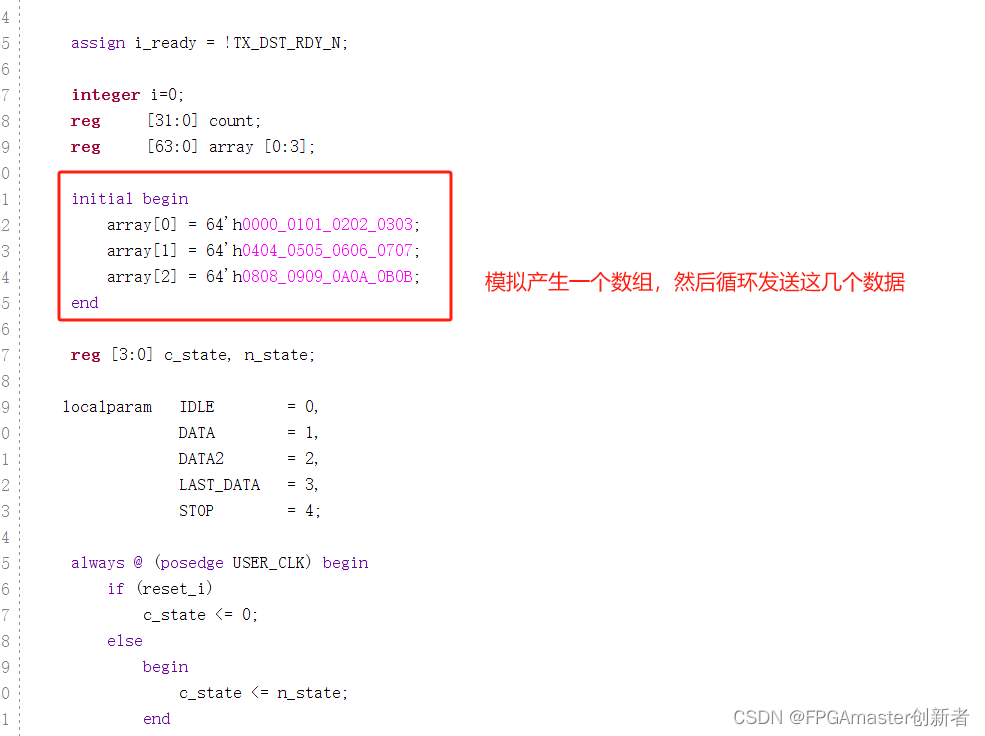

我们只需修改FRAME_GEN模块即可产生自己的数据,(AXI协议数据) 下面是具体修改的内容:

部分代码:

assign reset_i = RESET || (!CHANNEL_UP);

assign RESET_ii = RESET ;

assign resetUFC = reset_i;

assign i_ready = !TX_DST_RDY_N;

integer i=0;

reg [31:0] count;

reg [63:0] array [0:3];

initial begin

array[0] = 64'h0000_0101_0202_0303;

array[1] = 64'h0404_0505_0606_0707;

array[2] = 64'h0808_0909_0A0A_0B0B;

end

reg [3:0] c_state, n_state;

localparam IDLE = 0,

DATA = 1,

DATA2 = 2,

LAST_DATA = 3,

STOP = 4;

always @ (posedge USER_CLK) begin

if (reset_i)

c_state <= 0;

else

begin

c_state <= n_state;

end

end

always @(*) begin

case (c_state)

IDLE : begin

n_state = DATA;

end

DATA : begin

if (i == 2 && i_ready)

n_state = LAST_DATA;

else

n_state = DATA;

end

LAST_DATA : begin

if(i_ready)

n_state = STOP;

else

n_state = LAST_DATA;

end

STOP : begin

if (count >=200_000_000)

n_state = DATA;

else

n_state = STOP;

end

default : ;

endcase

end然后再自己建立一个顶层,(因为开发板的时钟和复位可能不符合Aurora协议),然后把这个设计例化到顶层,添加好约束文件,综合、实现、生成、bit文件。

2.1.2 发送数据验证

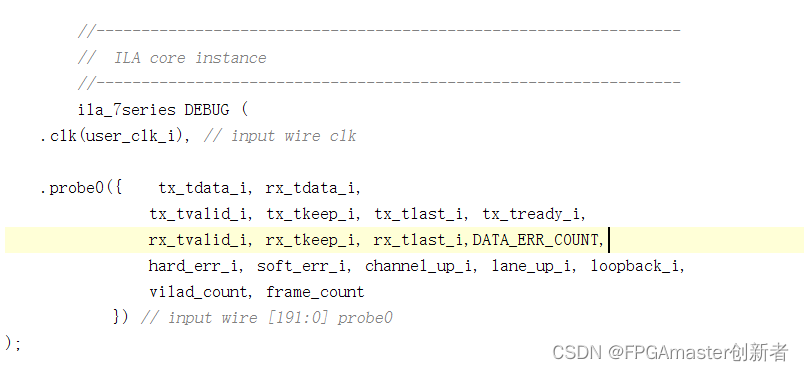

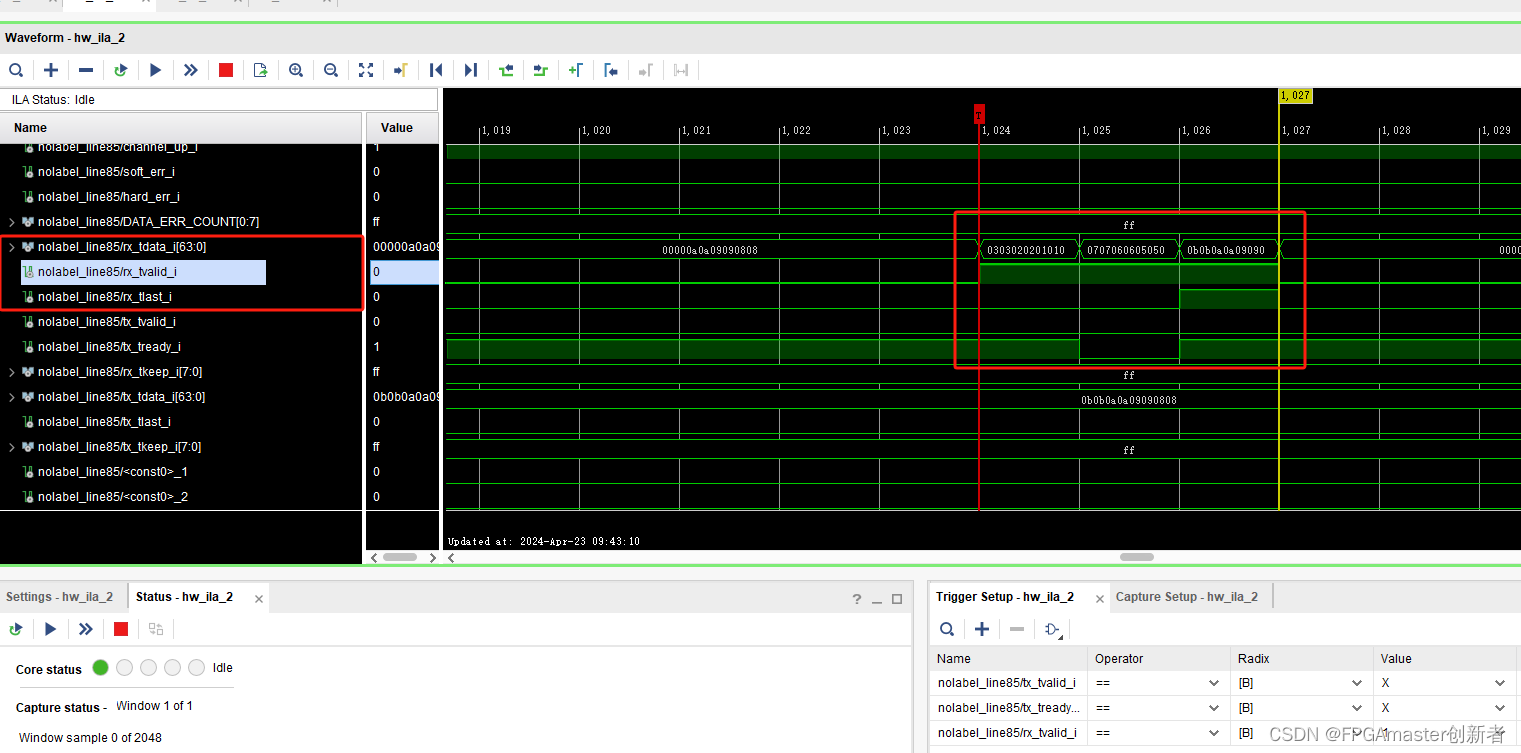

添加ILA到工程,具体采集的几个信号如下:(包括了发送数据部分、接受数据部分、Aurora状态部分)

然后重新编译工程,下载bit文件到开发板

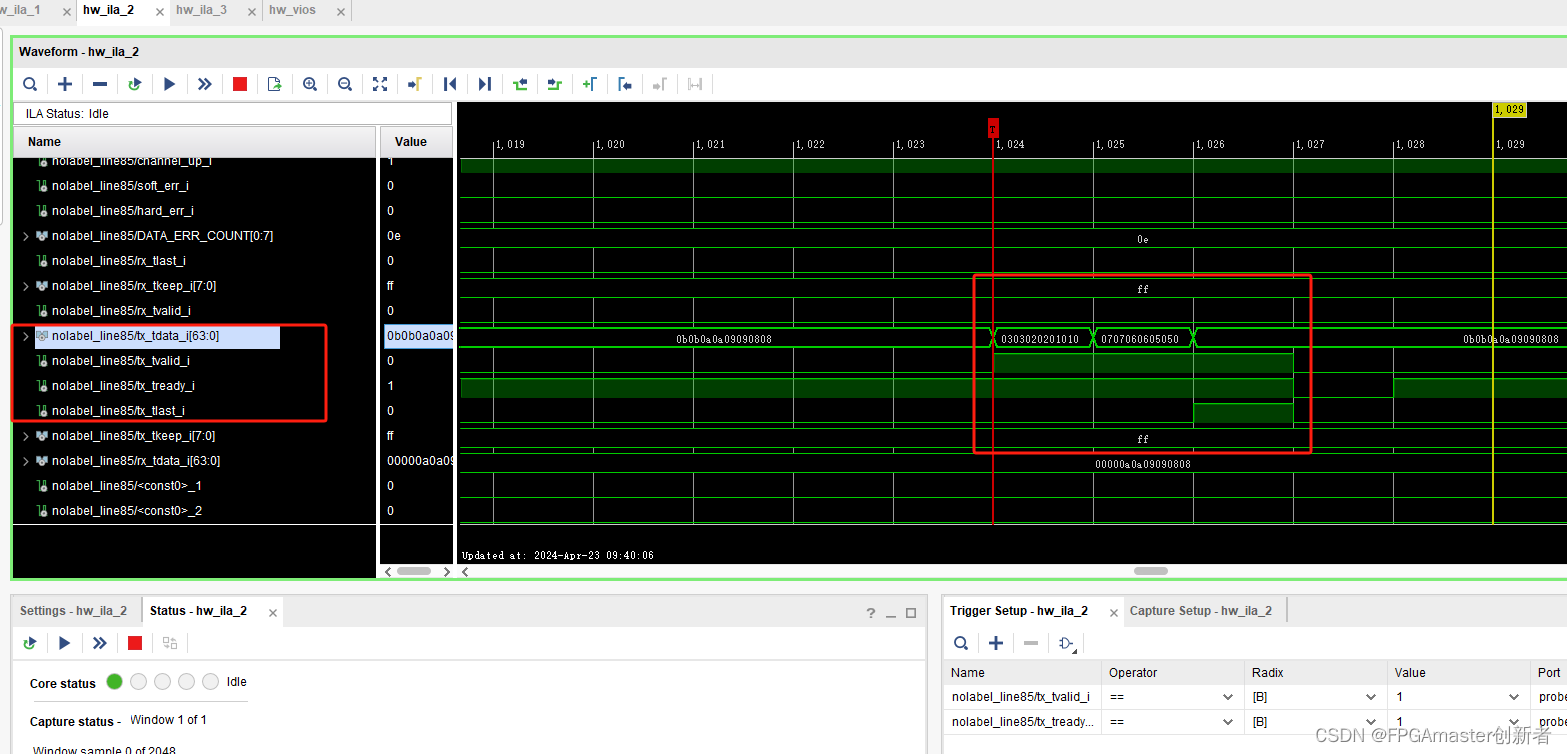

打开ILA界面,抓取tx_valid和tx_ready同时为高电平的时候的触发:(此时光纤必须回环连接)

如上图可以发现,就是按照咱们代码里的一样,发送出来三组数据00--0B

由此可以验证发送数据没问题!!

2.1.3 接受数据验证

紧接着我们可以来验证一下接受数据信号,同样在刚刚的ILA里,把接受数据的一些列信号移动到一起:

如上图可以发现,接受的数据和发射的数据完全一致,因为是Framing模式,所以数据接收并没有ready信号。

由此可以验证发送数据没问题!!

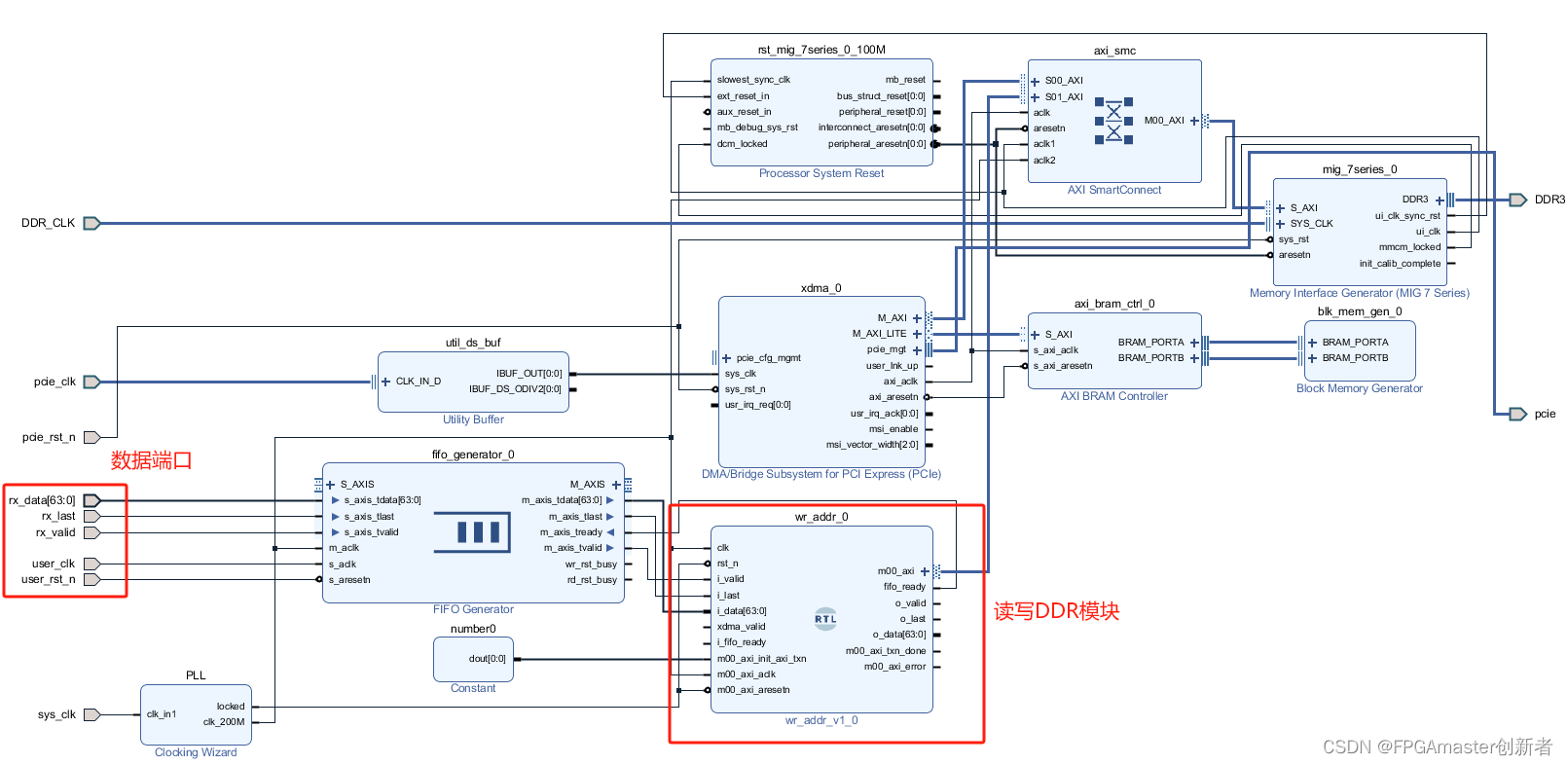

2.2 xdma、DDR链路模块设计

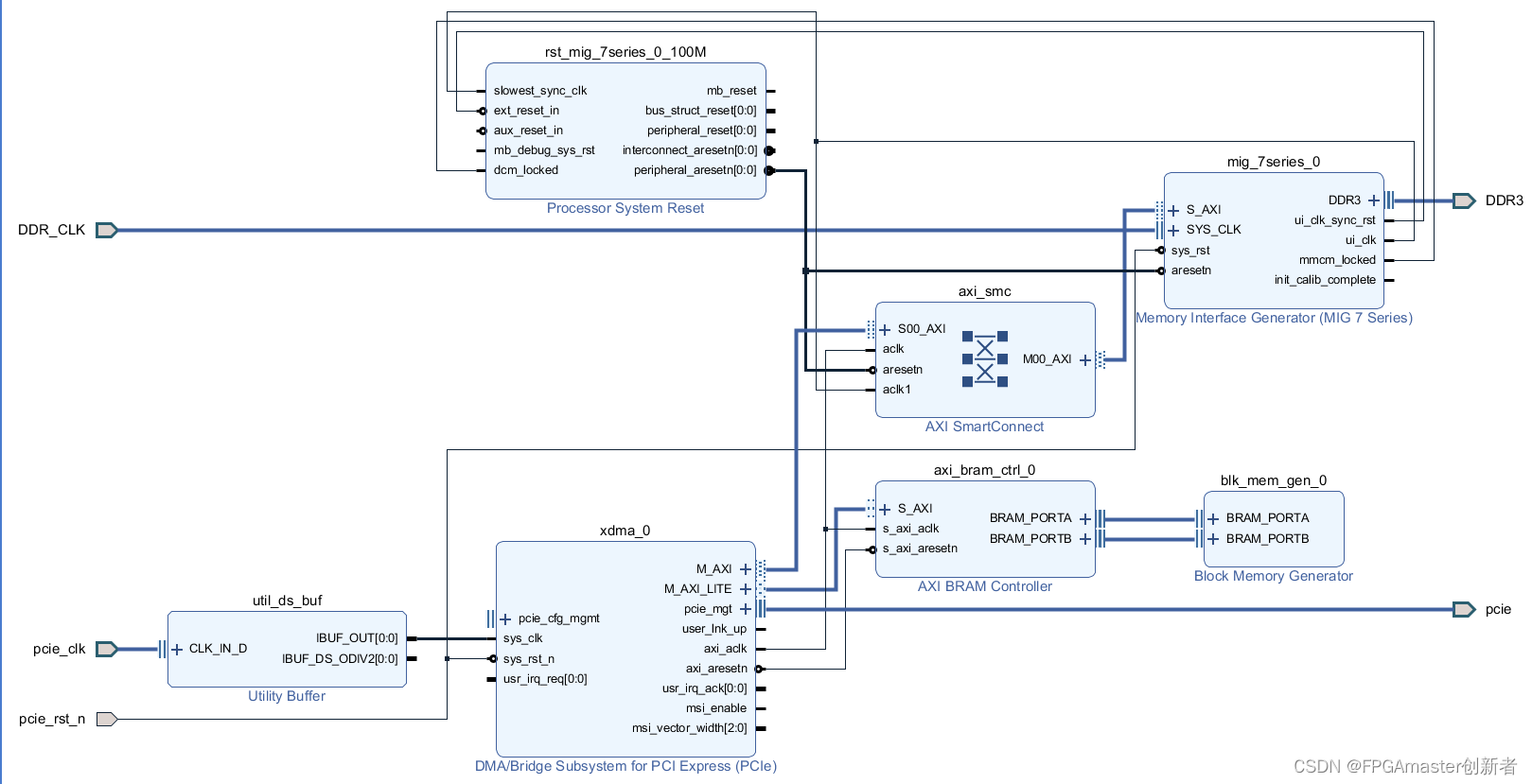

xdma、DDR链路本次设计采用block design设计

配置介绍:

1、PCIE链路速度:x4 5.0T

2、PC操作系统:Windows10

3、DDR:DDR3

2.2.1 代码设计

首先先建立一个BD设计文件:

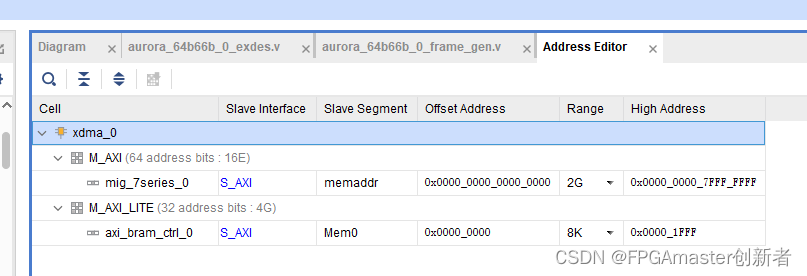

然后可以基于以前的XDMA读写DDR系列文章,来根据你的硬件搭建,我这边就不过多介绍了,直接展示搭建完成的截图。

别忘了给分配地址:

然后把BD设计生成verilog代码,并且置为顶层:

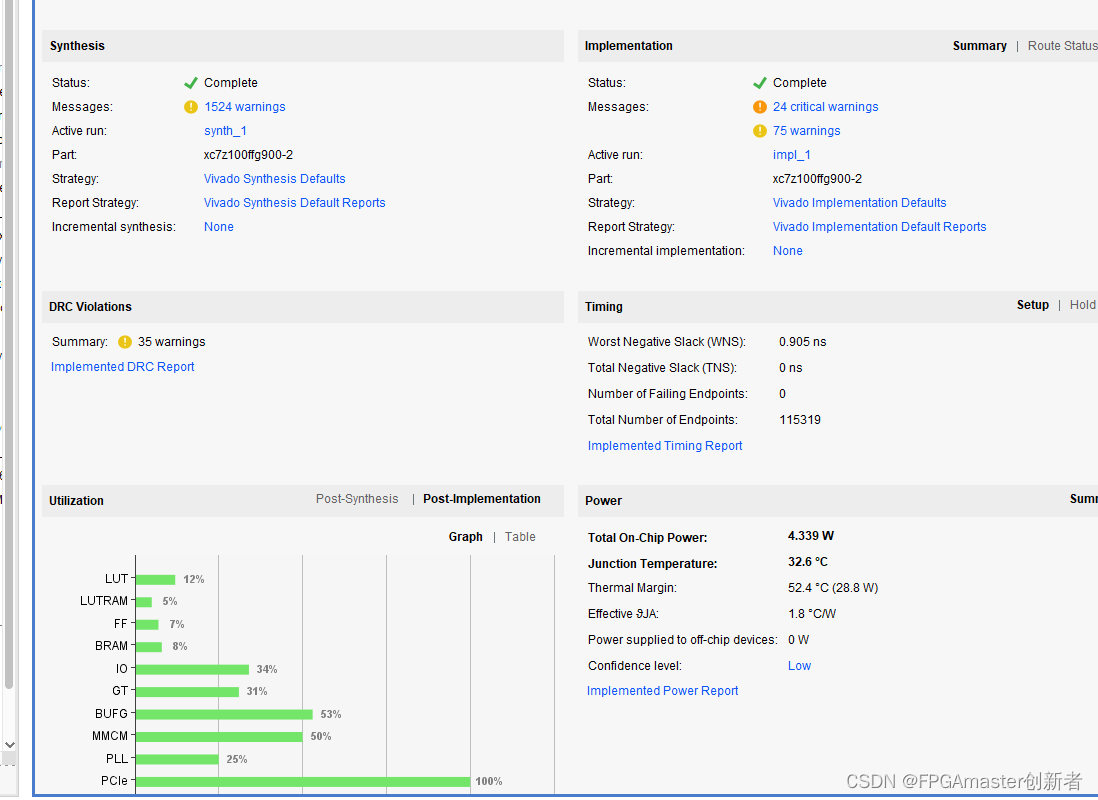

添加好约束文件,综合、实现、生成、bit文件。

2.2.2 XDMA读写DDR验证

下载bit文件到开发板,并且重启主机

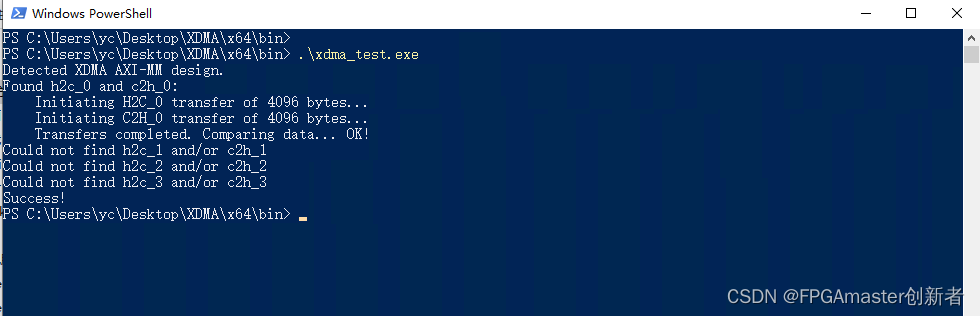

在powershell打开xdma驱动文件夹,并运行test.exe文件:

如上图所示,表示PCIE 向DDR写入4096字节,然后又从DDR读出4096字节,对比数据,数据一致。

由此可以验证XDMA读写DDR没问题!!

2.3 Aurora、XDMA、DDR连接设计

Aurora和XDMA模块,在前面都是单独测试的,现在我们需要把他们连接起来,实现完整的通路,也是我们这篇文章的重点内容

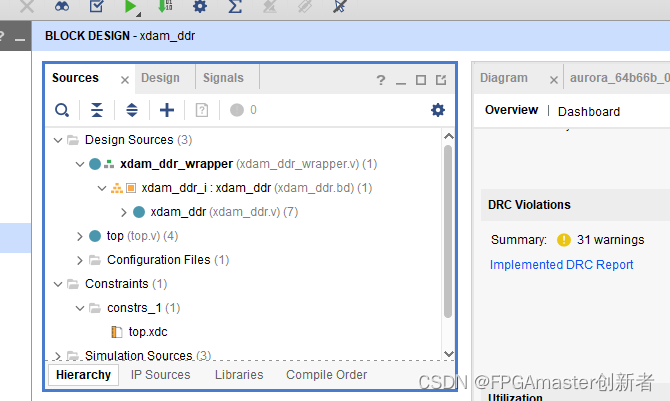

(1)首先把Aurora的文件置为顶层

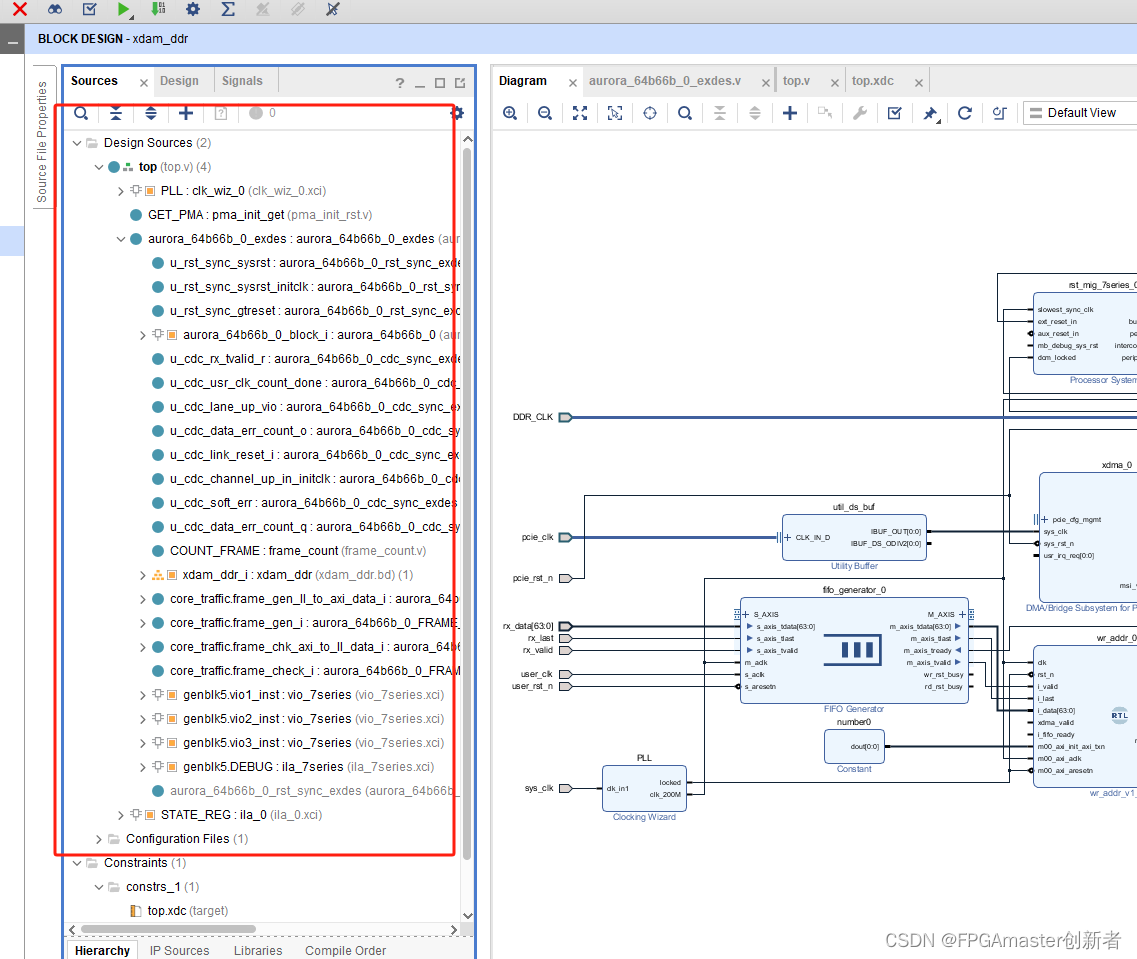

(2)在BD设计中添加数据接口,以及读写DDR部分代码,如下图所示

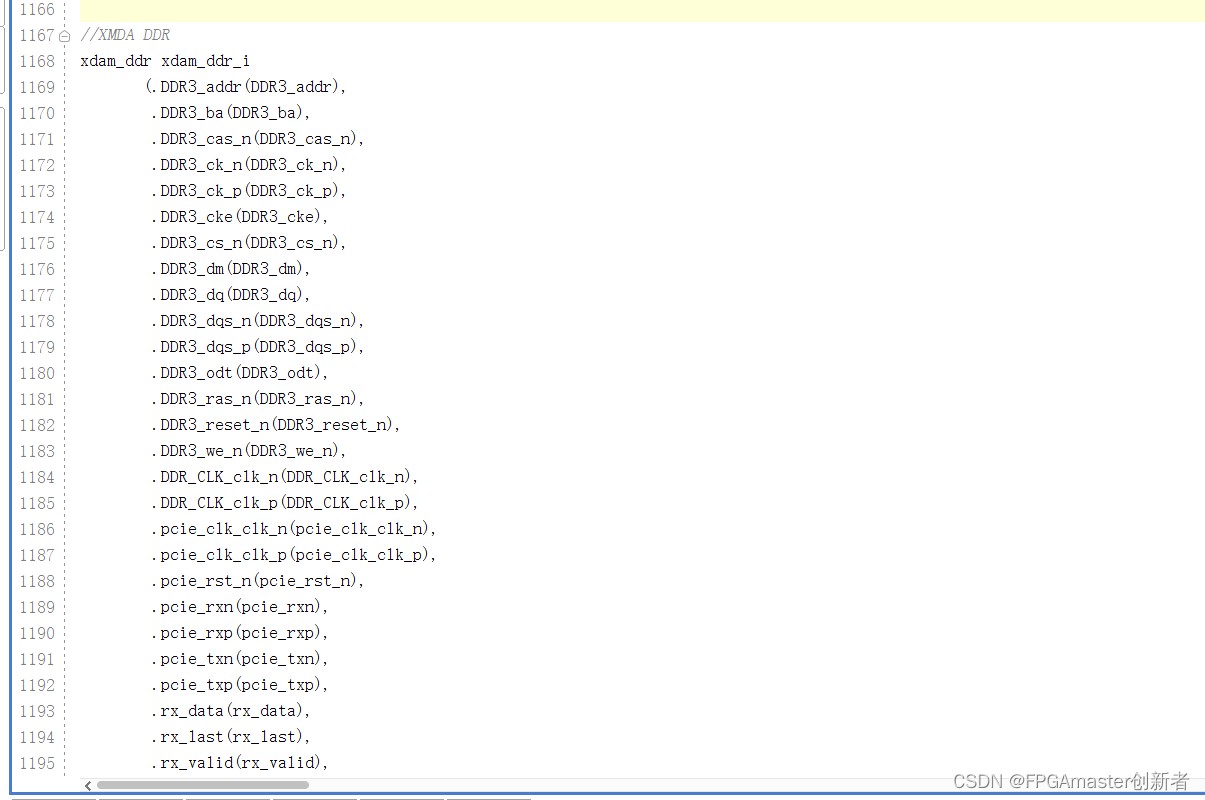

(3)编译一下BD文件,然后把BD设计例化到,Aurora的代码中,如下图所示

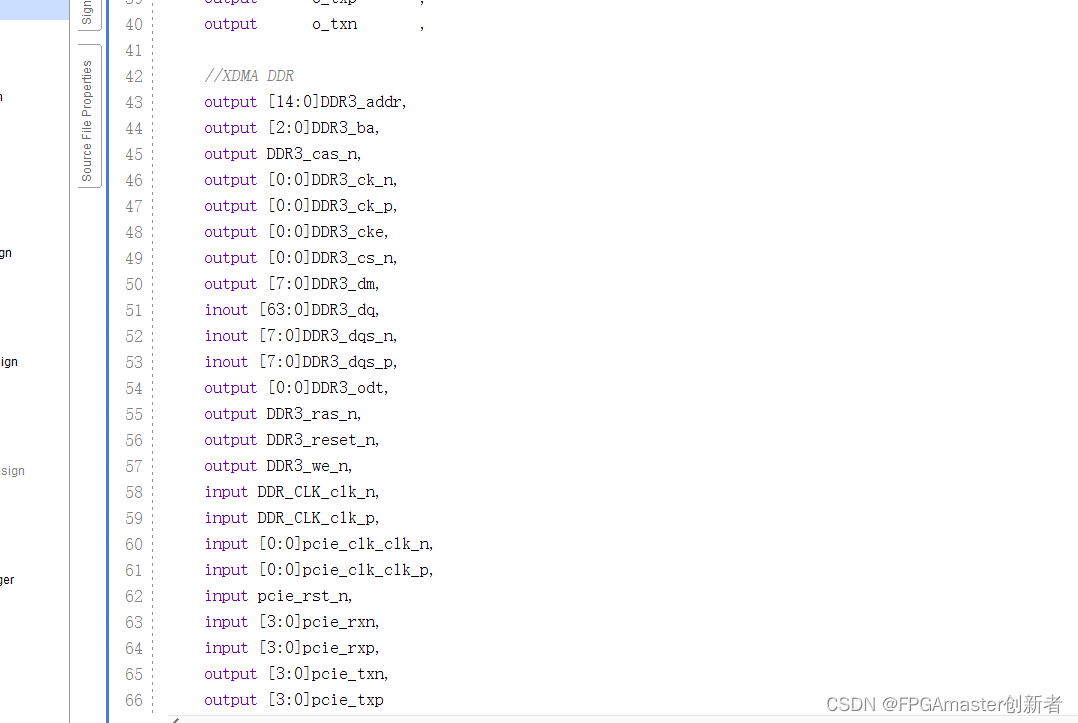

(4)同时也需要把DDR3,PCIE的端口添加到Aurora的顶层上面

(5)最终的工程层次关系如下:

(6)然后添加约束文件,综合、实现、生成、bit文件。

三、设计测试

3.1 modelsim仿真测试

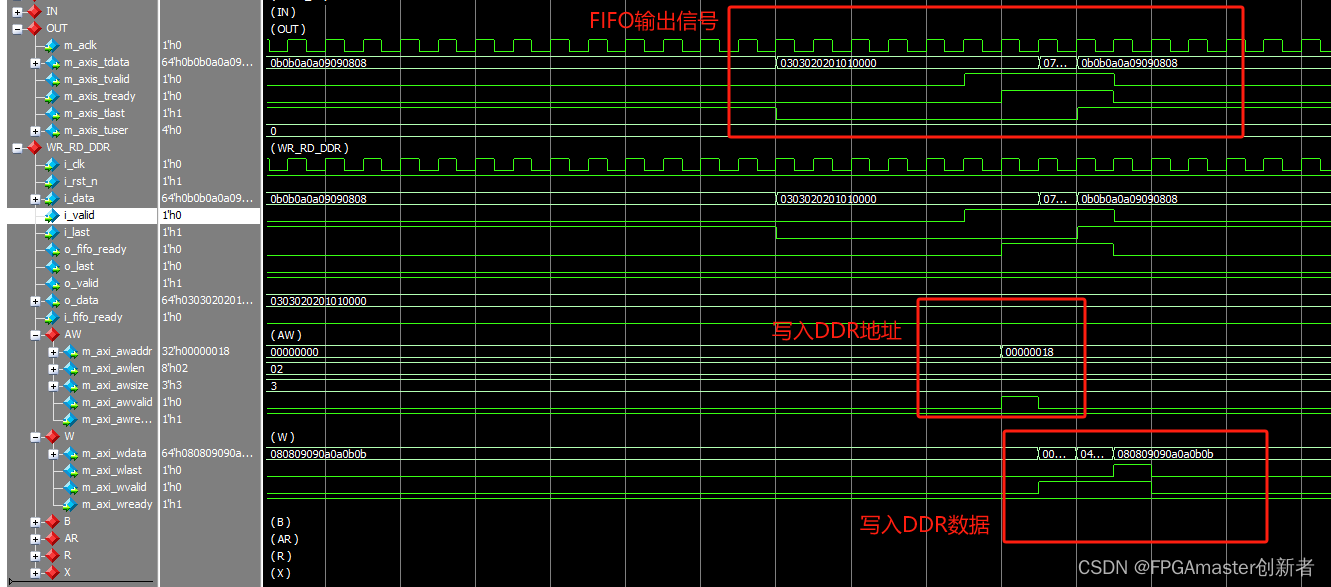

首先先对设计进行仿真测试,确保读写DDR模块无误,此次测试需要我们重新创建一个工程,单独仿真使用,这个我们的工程文件里面也包括。

由上图可以看见,数据从产生到FIFO,然后再写入到DDR整个链路的数据完整无丢失,这样可以确认我们的写入DDR模块没问题,接下来就可以下班进行测试,相信应该也没什么大问题!!

3.2 下板测试

经过上面的设计,以及单独的测试,相信离我们的目标已经很接近了,下面就来展示一下测试的结果。

将最终的bit文件下载到开发板,然后重启主机

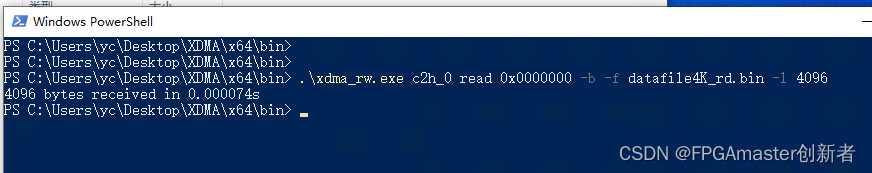

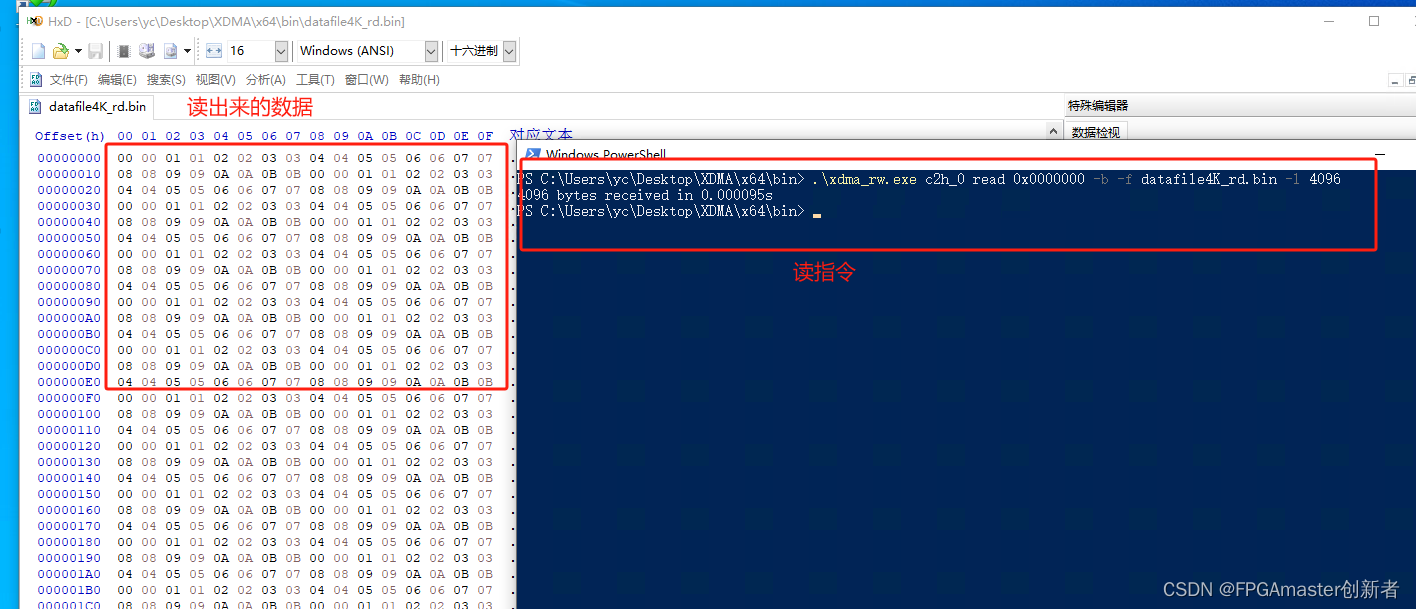

还是和刚刚的一样,使用XDMA驱动,来读取数据,读取从0地址4096个字节的数据,读取指令:

.\xdma_rw.exe c2h_0 read 0x0000000 -b -f datafile4K_rd.bin -l 4096

然后使用二进制查看软件,查看datafile4k_rd.bin这个文件即可,作者使用的软件是HxD.exe,需要的小伙伴自行去下载即可。

如上图看出来,读出来的数据和写入的数据完全一致

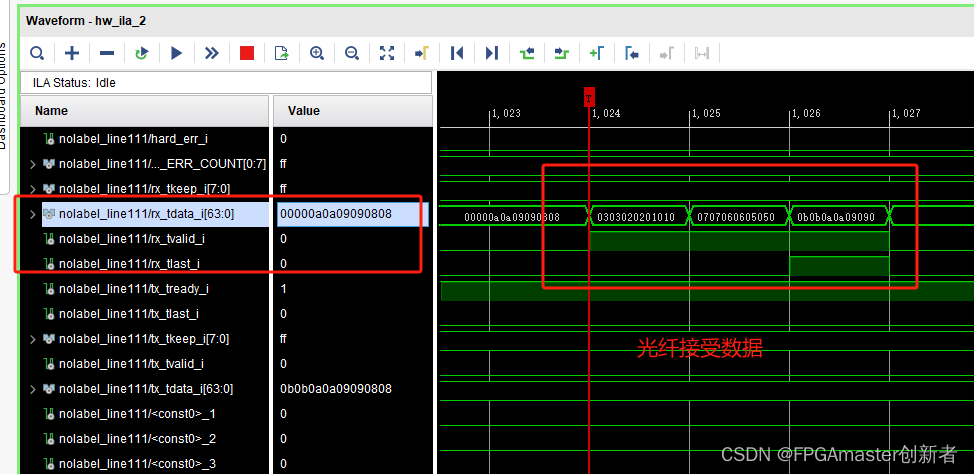

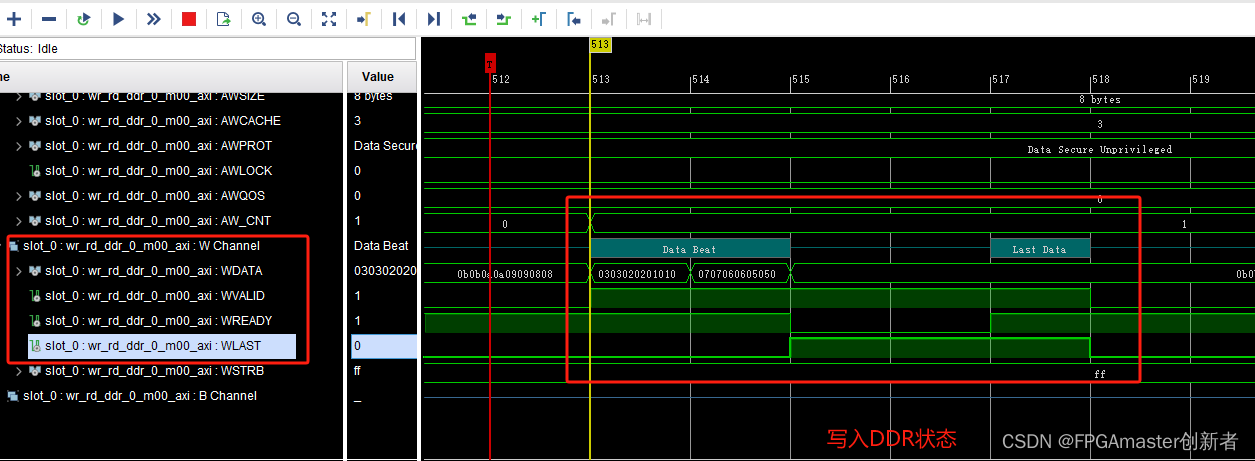

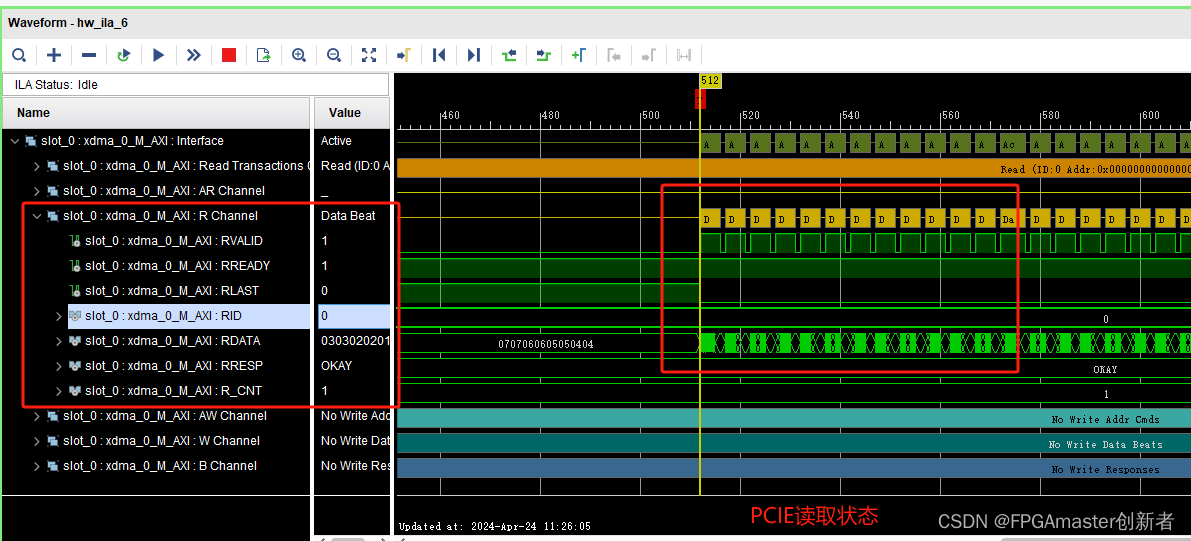

还可通过ILA观察数据的写入过程,这边添加几个ILA的状态截图

光纤接受数据:

读写DDR状态:

PCIE读取状态:

由此可以验证本次设计整体没问题!!,终于大功告成啦!!!

如果感觉文章对您有用,麻烦三连支持一下,方便下次用到的时候,就可以快速找到我,非常感谢您的支持!!!

本文详细介绍了如何使用FPGA将数据从光纤传输到PCIE,通过Aurora和XDMA模块结合DDR进行高速数据传输,涉及设计步骤、代码修改、模型验证和实际测试,旨在实现10Gbps的高速通道应用。

本文详细介绍了如何使用FPGA将数据从光纤传输到PCIE,通过Aurora和XDMA模块结合DDR进行高速数据传输,涉及设计步骤、代码修改、模型验证和实际测试,旨在实现10Gbps的高速通道应用。

2038

2038

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?