基于STM32微控制器的无线视频传输系统设计

摘要

本文设计了一种基于STM32的无线视频传输系统,该系统以STM32F103VET6微处理器为核心,通过视频采集模块采集视频数据,并将视频数据经无线发射模块发送至接收端,接收端将接收到的数据在LCD屏幕上显示。介绍了发射器和接收端的软件设计过程。实验结果证明,该系统实现了无线视频传输功能。

关键词 :STM32;无线视频传输;NRF24L01;OV7670。

引言

随着移动通信的发展,无线通信已得到广泛应用。面向无线通信的视频编码与传输技术已成为信息科学技术的前沿课题[1]。目前,无线视频传输系统成本较高,难以满足社会需求。本文设计了一种以STM32微处理器为核心的低成本视频传输系统。通过视频采集模块、无线传输模块和LCD模块,实现了高性价比且效果良好的无线视频传输。

系统总体设计

视频传输系统分为数据采集发射端和接收显示端。采集发射器的硬件资源包括以STM32F103ZET6芯片作为主控制器,以OV7670摄像头作为视频数据采集模块[2],以及NRF24L01模块作为视频数据发射器。接收显示端采用STM32F103ZET6芯片作为主控制器,NRF24L01模块作为视频数据接收器,LCD显示器用于显示视频数据[2]。系统总体设计如图1所示:视频采集模块采集视频数据,由STM32F103控制的采集发射器通过NRF24L01无线传输模块发送数据;接收显示终端通过NRF24L01接收无线数据并传送给STM32F103,再通过LCD屏幕显示数据。

硬件设计

微处理器选择

采用STM32F103ZET6的ST芯片作为发射器和接收端的主控制器,其内部闪存容量为512千字节,内存64千字节,包含2个基本定时器、4个通用定时器、2个高级定时器、2个DMA控制器、3个SPI、2个IIC、5个串行端口USB、3个CAN、12个模数转换器、1个12位数模转换器、1个SDIO接口和1个FSMC接口。系统集成度高,易于开发,可缩短产品开发周期。STM32还具有低功耗、小尺寸、性价比高、资源配置丰富且灵活配置、高可靠性等优点,有利于工业级产品的生产和使用。

硬件电路设计

采集发射器的主控制器通过SCCB总线接口与OV7670模块通信,完成对OV7670模块的初始化,并控制OV7670的工作模式。通过操作FIFO读取并利用I/O端口直接读取FIFO中的临时图像数据,实现对图像数据存储指针OV7660的写入。当VSYNC(帧同步信号)到来时,触发主控制器的外部中断,通知主控制器开始输出图像数据,主控制器使能FIFO写指针,将图像数据写入FIFO。当下一个VSYNC(帧同步信号)到来时,表示该帧信号结束,主控制器禁止FIFO写指针,同时启动FIFO读指针,通过I/O端口读取FIFO中刚存入的临时图像数据,并通过NRF24L01发送出去。由于FIFO不能同时进行读写操作,因此会丢弃一帧的数据。

为了提高LCD屏幕刷新率并减少数据更新延迟,对于存储在先进先出队列中的每帧图像数据,仅显示其中的1/4,即四帧图像数据在LCD上显示为完整的一帧图像。但由于拍摄速度较高,若无剧烈晃动,画面质量仍可达到清晰程度。

视频采集模块

采集发射器OV76760是OmniVision(OV)公司生产的一款1/6英寸CMOS VGA图像传感器,具有小尺寸、低工作电压的特点,提供单芯片VGA摄像头和图像处理器的全部功能。通过SCCB总线控制,可输出整帧、子采样以及窗口裁取等多种分辨率的8位图像数据。在VGA屏幕下每秒最高可达30帧。用户可完全控制图像质量、数据格式和传输模式。所有图像处理过程,包括伽马曲线、白平衡、颜色等,均可通过SCCB接口进行程序化设置。

OV7670的图像数据输出格式支持VGA(分辨率为640x480)、QVGA(分辨率为320x240)和QQVGA(分辨率为160x120),输出3个时钟信号:PCLK(像素时钟,每个PCLK时钟输出一个像素)、VSYNC(帧同步信号)和HREF/HSYNC(行同步信号)。OV7670的图像数据输出(在D[7:0]端口)受PCLK、VSYNC、HREF/HSYNC控制。

本文采用QVGA输出格式,图像为RGB565格式,即每2个字节构成一个像素颜色(高字节在前,低字节在后)[4]。

由于OV7670d的像素时钟(PCLK)高达24兆赫,使用主控制器的I/O端口获取像素数据非常困难。因此本方案在摄像头模块中采用自带FIFO芯片的方式,用于临时存储图像数据。该FIFO芯片容量为384KB,足以存储2帧QVGA图像数据。该模块的原理图如下:

OV7670的OV_XCLK外部时钟输入引脚需要提供外部12M晶体。OV7670的OV_HREF和STM32F103的FIFO_WEN通过一个逻辑电路输出FIFO_WE,用于控制FIFO芯片的写使能引脚,只有当两个输入均为1时,输出才为低电平,从而启用FIFO写指针。

主控制器的PG13和PD3引脚构成SCCB总线,用于控制OV7670的初始化并配置STM32F103的内部寄存器。摄像头输出像素时钟为OV_PCLK,连接至FIFO芯片输入端以提供时钟信号,FIFO根据该时钟将摄像头输出的每个像素数据写入内部RAM。

OV7670的像素数据通过OV_D[0‐7]连接到先进先出队列,先进先出队列的数据输出通过FIFO_D[0‐7]与STM32F103连接至PC[0‐7]。FIFO_WRST为写信号复位信号输入引脚,当其为0时,先进先出队列的写指针被复位。FIFO_RRST为先进先出队列的读指针复位引脚,当其为0时,读指针被复位。FIFO_OE为输出使能引脚,当其为低电平时,允许先进先出队列输出数据。

无线收发模块

使用NRF24L01作为无线视频数据收发器,基于SPI接口的2.4G无线模块最高工作速度为2Mbps,无线数据传输、多点通信和跳频通信。高效的GFSK调制,抗干扰能力强,特别适用于工业控制场合。低功耗1.9V‐3.6V工作,待机模式下为22微安;掉电模式下为900纳安。通信距离:无损或小损耗50米[3]。

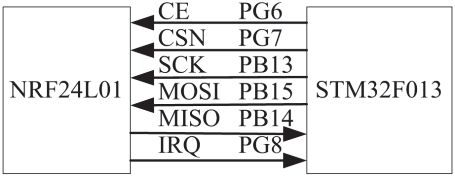

CE引脚为模式控制输入引脚。CSN模块为芯片选择信号线,当其处于低电平时,芯片将开始工作。时钟信号线由SCK主控制器提供。MOSI为芯片控制数据线(主从输入),MISO为芯片控制数据线(主从输出),IRQ中断信号引脚用于输入。该模块通过SPI总线与主控制器通信。

视频显示模块

使用 ILI9341 LCD模块驱动器 作为 视频显示终端,尺寸为 2.8英寸,内存大小为 172800字节,分辨率为 320 * 240。

液晶显示屏 模块中的 显示像素 将根据预先设定的方向进行设置,包括 左右 和 上下 方向,例如设置从左到右、从上到下的方向,则 液晶控制器 将按照该方向扫描 液晶屏,依次填充每个像素的 像素数据。此外还需设置显示的 光标坐标,即 液晶控制器 将从该位置开始填充 像素数据。

软件设计

无线视频发射器的工作流程为:当采集终端启动并完成STM32控制器的初始化、OV7670模块初始化、NRF24L01模块初始化后,进入一个死循环,主控制器循环发送命令给OV7670模块以采集视频数据,并将一帧图像的1/4存储在内存中,然后主控制器将数据发送给NRF24L01模块,由NRF24L01模块传输视频数据,如此循环。

在图像采集过程中,为了确定ov_sta的值,当进行图像数据采集时,ov_sta的初始值为0。当进入由摄像头输出场中断信号触发的中断服务程序时,ov_sta的值会发生变化。当ov_sta小于2(即为0或1)时,若ov_sta为0,表示摄像头一帧数据采集完成(此时产生场中断信号),可将该帧图像数据写入FIFO,然后将ov_sta加1。此时再次发生中断时,需根据ov_sta的值进行判断(注意此时摄像头已准备好第二帧数据)。FIFO中存放的是第一帧图像,此时应禁止向FIFO写入数据,而在主程序中读取FIFO中的数据。当ov_sta为1时,中断程序将禁止FIFO写入,并将ov_sta加1,使ov_sta变为2,随后主程序进入读取FIFO数据阶段。

在读取先进先出队列的过程中,并未将完整的240x320图像存储到内存中,其原因有两个:一是无线视频传输不需要过于精确的数据,只要能清晰看到传感器数据即可,因此为保持连续视频的传输,只能牺牲部分精度;二是保存一帧图像需要较大的内存空间,会增加控制器的处理负担。为了最大限度地利用控制器的处理能力,图像被分割为多种传输方式。每列的320像素数据被完整读取,但240行并非按顺序全部读取,而是每隔一行读取一行,共读取60x320数据,保存至ImageData[60][240][2]数组中。发送完这些数据后,将ov_sta清零,以便程序重新执行前端操作,若存在场中断信号也不会造成干扰。

发送数据时,以数据包的形式发送,每次发送32个U8元素,即16个像素的数据。每次发送所谓的帧图像之前(实际上是1/4帧),会有一个数字标明这是第几个1/4帧被发送,接收端将根据该数字判断如何将数据组合成屏幕上的图像。具体而言,程序会根据每次接收到的图像是第几个1/4帧来确定填充到屏幕的哪些行:当接收到第一个1/4帧时,接收端会将数据填充到第1、5、9⋯⋯237行,共60行;当接收到第二个1/4帧图像时,接收端会将数据填充到第2、6、10⋯⋯238行,共60行;当接收到第三个1/4帧图像时,数据将被填充到第3、7、11⋯⋯239行,共60行;当接收到第四个1/4帧图像时,数据将被填充到第4、8、12⋯⋯240行,共60行。

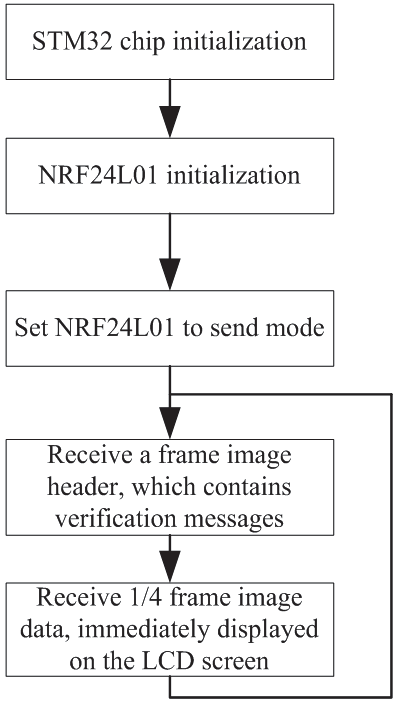

摄像头输出场中断信号导致主控制器中断程序流程如图4所示:接收端上电启动后,STM32主控制器完成初始化、LCD模块初始化以及NRF24L01初始化后进入死循环,在该循环中主控制器将NRF24L01模块接收到的无线视频数据保存至内存,然后主控制器将内存中的数据发送至LCD模块中的LCD控制芯片进行数据显示。具体过程如图5所示:

接收端每次接收到1/4帧图像时,都会接收一个数据头,该数据头包含校验信息以及表示前1/4帧图像的信息。当校验正确后,主机控制器将让无线接收模块把1/4帧图像保存到内存中,然后在LCD屏幕上显示。

实验验证

发送和接收终端如图6所示:

图片上方是无线ss传输端,摄像头正对商标文本。以下是接收显示端,可以看到摄像头采集到的文本。无线模块拍摄的物体可以在接收端的LCD屏幕上显示。

本文设计了一种基于STM32的无线视频传输系统,由视频采集模块、无线收发模块和STM32显示模块组成。该系统适用于工业环境,整体系统设计简单、高可靠性,实现了短距离无线视频传输。存在的问题是图像刷新率较慢,因为图像数据未进行压缩,导致无线收发的是原始图像数据,数据量较大。这需要更快的处理器以及采用视频数据压缩方案。

9795

9795

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?