在学习期间发现有的基础知识点没记牢,特发此帖用于整理基础知识。

更新时间:2025/8/24

逻辑门

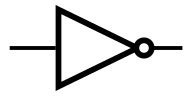

1. NOT 门(非门,反相器)

-

符号:~A 或 A′

| 输入 A | 输出 ~A |

|---|---|

| 0 | 1 |

| 1 | 0 |

Verilog 代码:

module NOT_gate (

input A,

output Y

);

assign Y = ~A; // 按位取反

endmodule

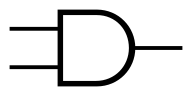

2. AND 门(与门)

-

符号:A · B

| A | B | A · B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Verilog 代码:

module AND_gate (

input A, B,

output Y

);

assign Y = A & B; // 按位与

endmodule

3. OR 门(或门)

-

符号:A + B

| A | B | A + B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Verilog 代码:

module OR_gate (

input A, B,

output Y

);

assign Y = A | B; // 按位或

endmodule

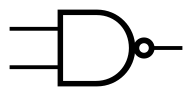

4. NAND 门(与非门)

-

符号:(A · B)′

| A | B | (A · B)′ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Verilog 代码:

module NAND_gate (

input A, B,

output Y

);

assign Y = ~(A & B);

endmodule

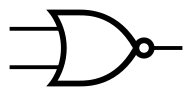

5. NOR 门(或非门)

-

符号:(A + B)′

| A | B | (A + B)′ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Verilog 代码:

module NOR_gate (

input A, B,

output Y

);

assign Y = ~(A | B);

endmodule

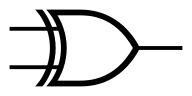

6. XOR 门(异或门)

-

符号:A ⊕ B

| A | B | A ⊕ B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Verilog 代码:

module XOR_gate (

input A, B,

output Y

);

assign Y = A ^ B; // 按位异或

endmodule

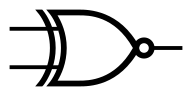

7. XNOR 门(同或门)

-

符号:(A ⊕ B)′

| A | B | (A ⊕ B)′ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Verilog 代码:

module XNOR_gate (

input A, B,

output Y

);

assign Y = ~(A ^ B);

endmodule

802

802

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?