重庆交通大学信息科学与工程学院

《嵌入式系统基础A》课程

作业报告(第十周)

班 级: 物联网工程2002

姓名-学号 : 吴泽霖-632007060217

实验项目名称: 数字电路基础与Quartus入门

实验项目性质: 设计性

实验所属课程: 《嵌入式系统基础》

实验室(中心): 南岸校区语音大楼

指 导 教 师 : 娄路

完成时间: 2022 年 11 月 14 日

一、实验内容和任务

1、在 Quartus中自己用门电路设计一个D触发器,并进行仿真,时序波形验证; 在 Quartus 中直接调用一个D触发器电路,进行仿真,时序波形验证,与1做比较;在 Quartus 中用Verilog语言写一个D触发器,进行仿真验证,与2做比较;

二、实验要求

1. 分组要求:每个学生独立完成,即1人1组。

2. 程序及报告文档要求:具有较好的可读性,如叙述准确、标注明确、截图清晰等。

3.项目代码上传github,同时把项目完整打包为zip文件,与实验报告(Markdown源码及PDF文件)、作业博客地址一起提交到学习通。

三. 实验过程介绍 (此处可以填博客内容)

一、创建D触发器原理图并仿真

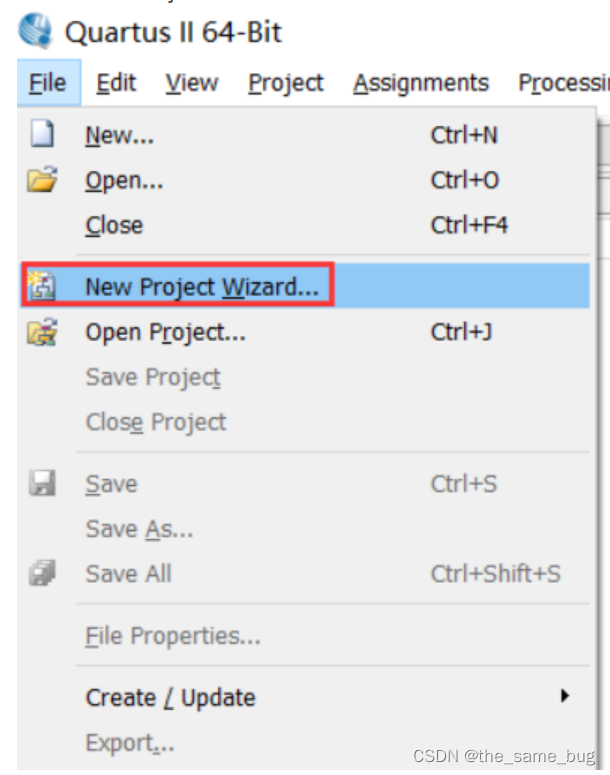

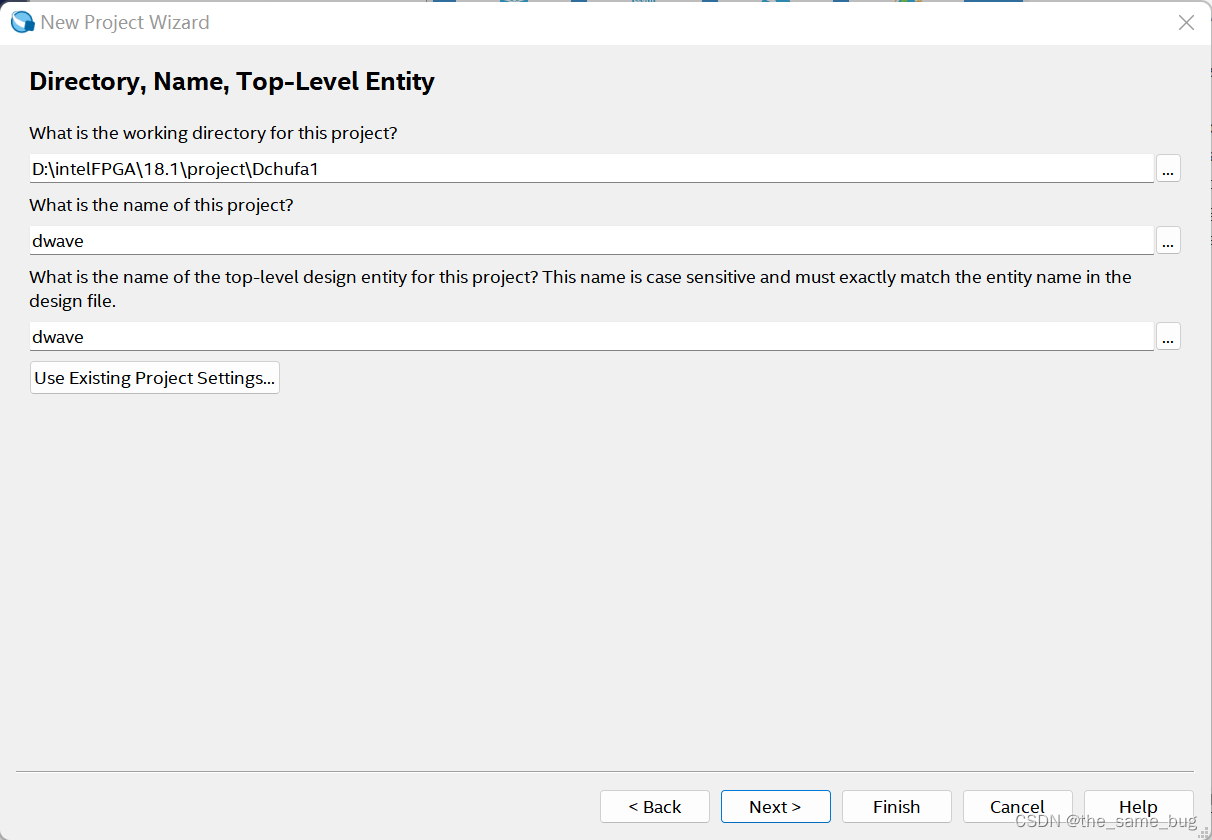

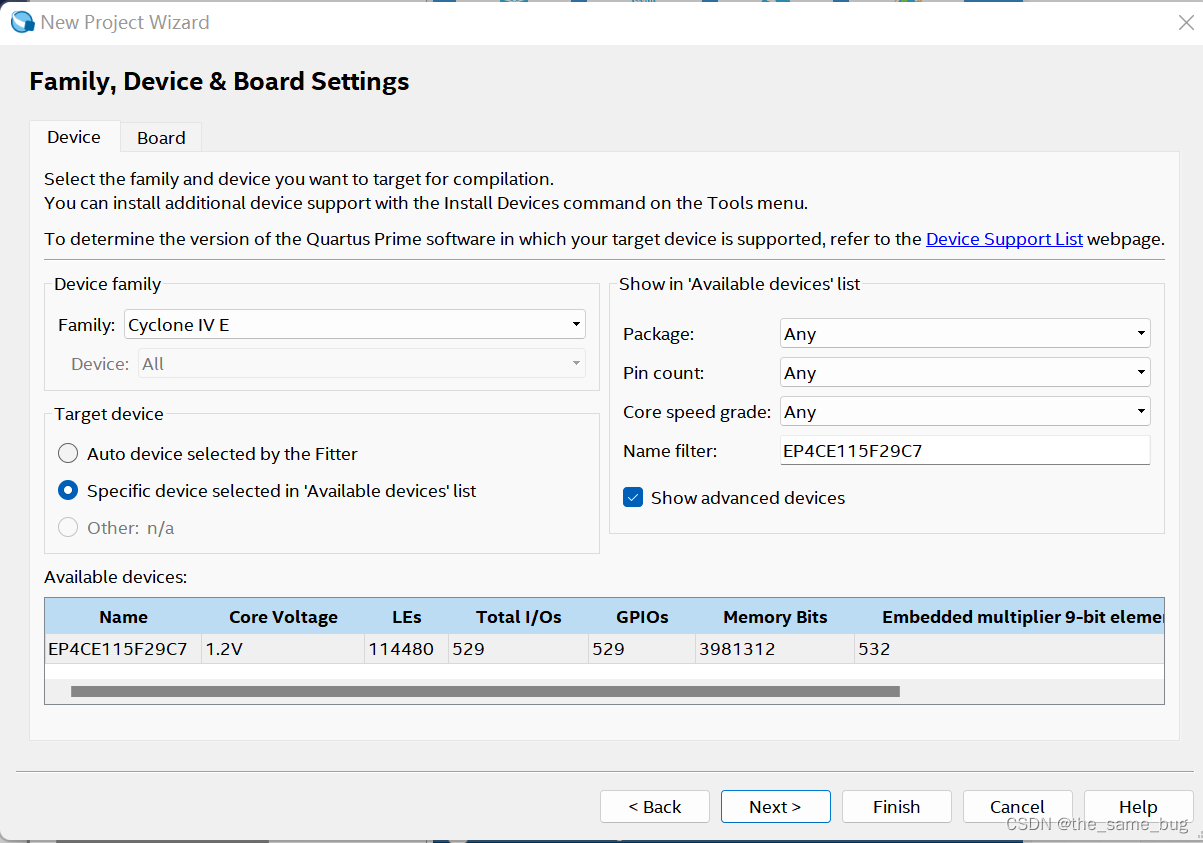

1、创建工程

之后一直点next,直到finish。

2.新建原理图文件

新建文件

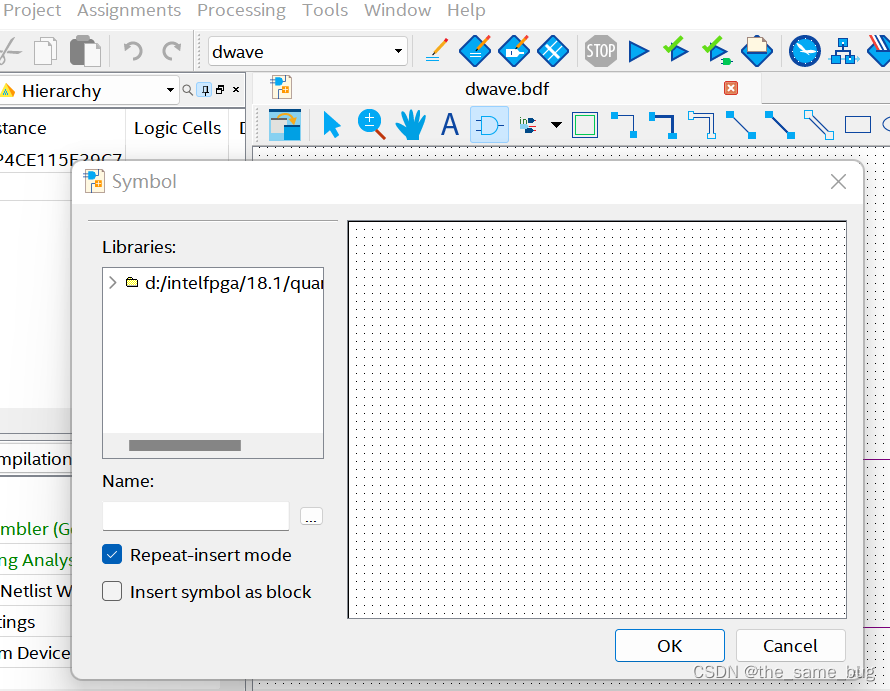

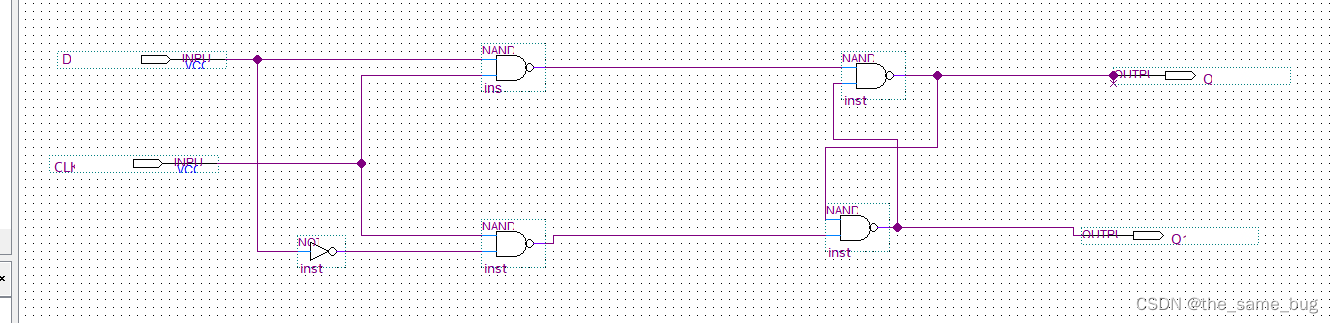

点击按纽“ Symbol Tool”或直接双击原理图空白处,从“ Symbol”窗中选择

4 个 nand2 与非门,1 个 not 非门,2个输入管脚和2个输出管脚,并连线,最终如下图:

3.编译

编译成功后,查看硬件

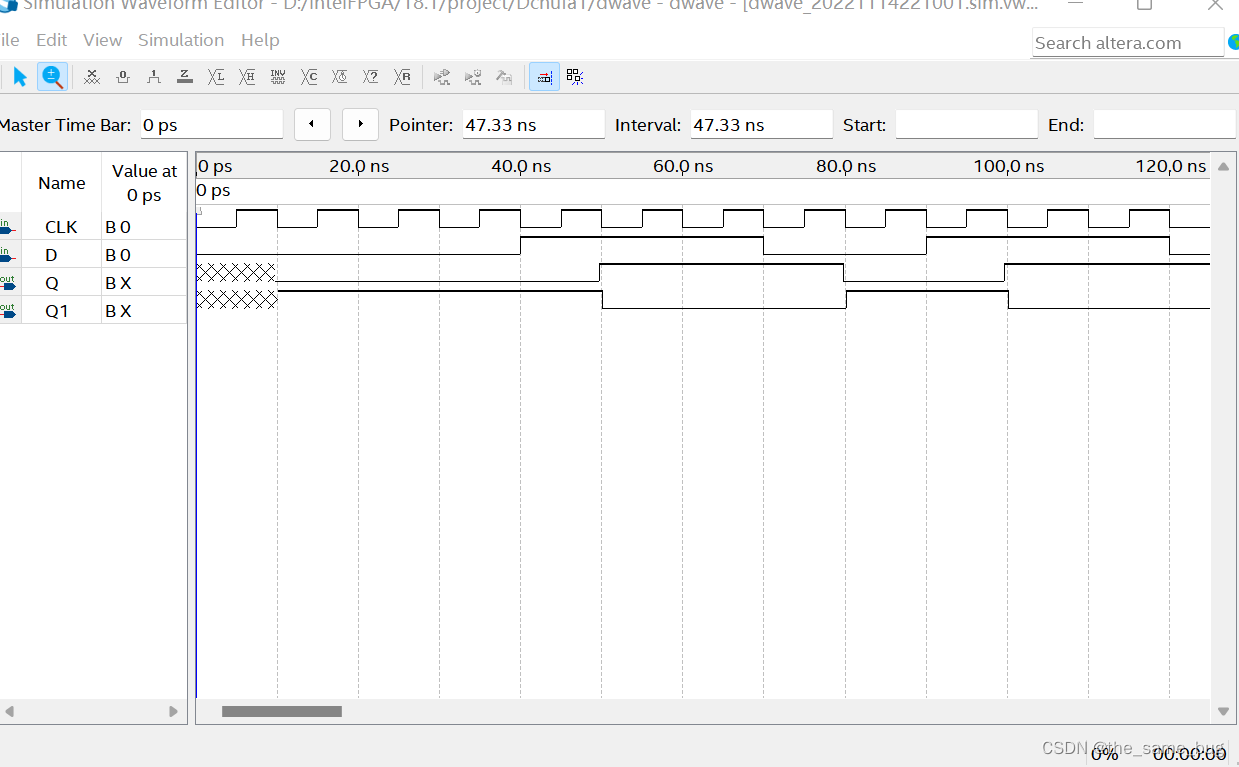

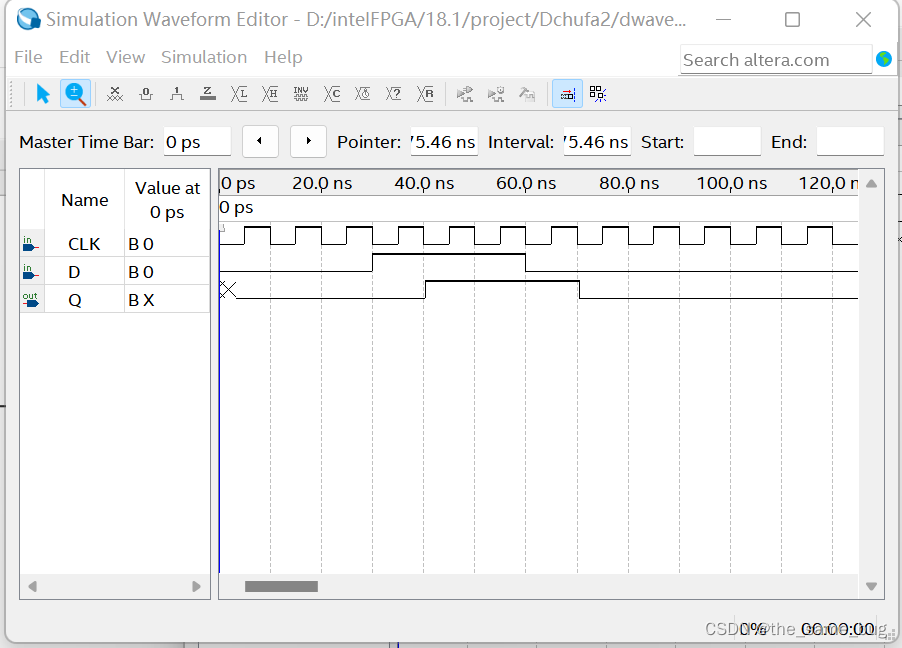

4.仿真波形图

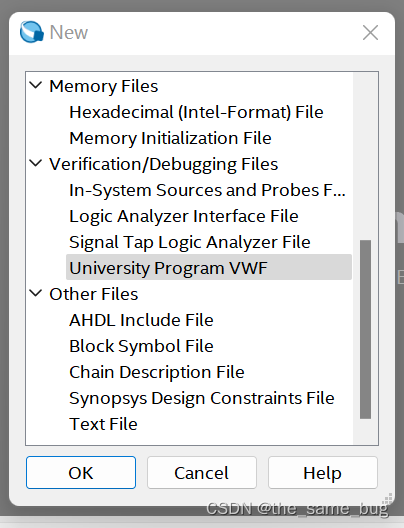

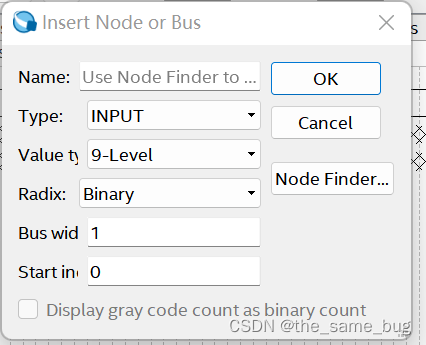

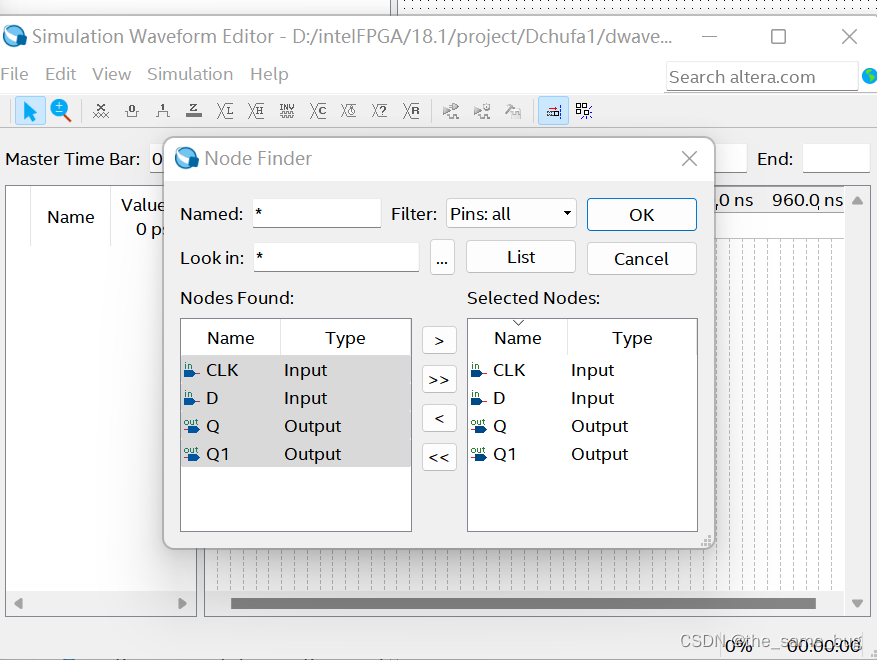

新建波形文件。如上面新建图形文件的方法,从“file”中选择“new”,然后从出现的对话框中选择“university program VWF”。

点击“OK”。

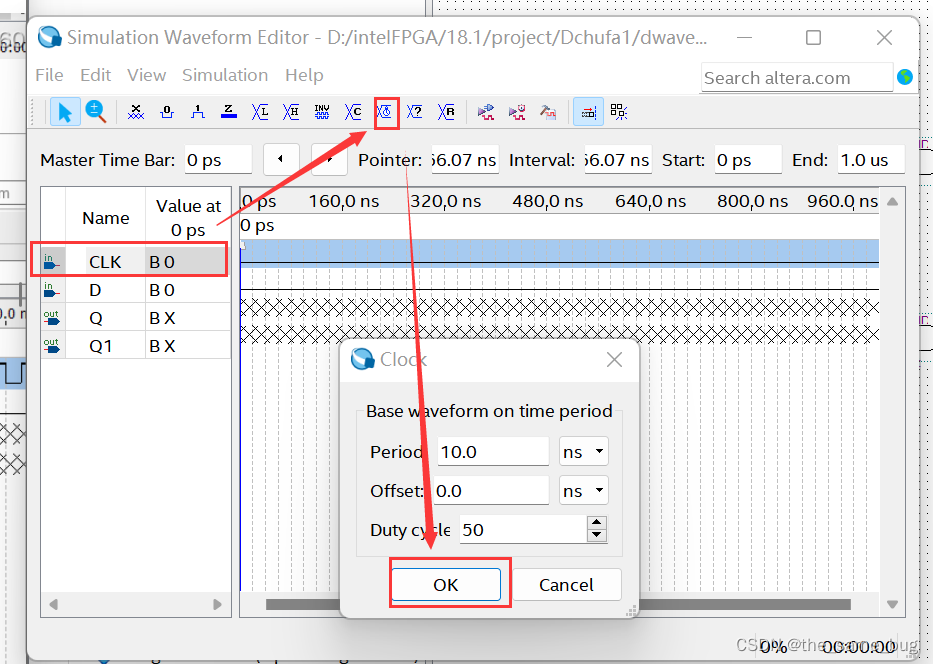

把输入D随便设置几个低电平和高电平 功能仿真

功能仿真

延时半个周期

时序仿真

延时一个周期

二、调用D触发器并仿真

1.创建工程

与上一步一致

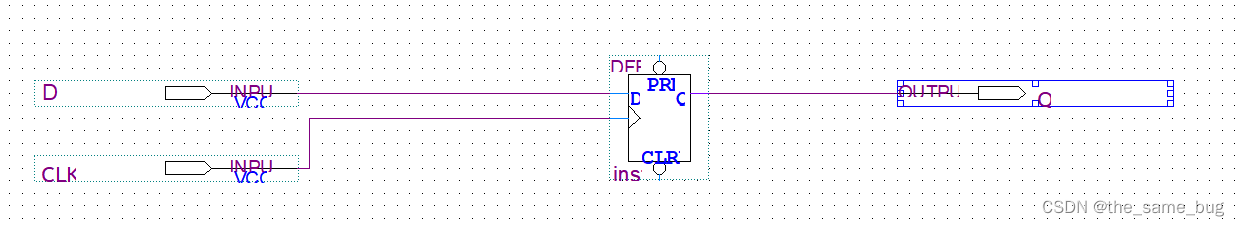

2.新建原理图文件

与上一步一致

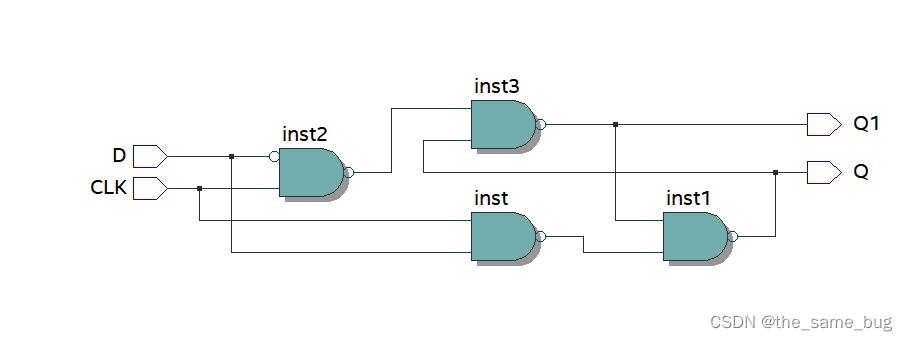

这时,不再画D触发器的内部结构了,而是直接调用D触发器,元件名:dff

查看原理图

3.仿真波形图

具体步骤与上一个相同

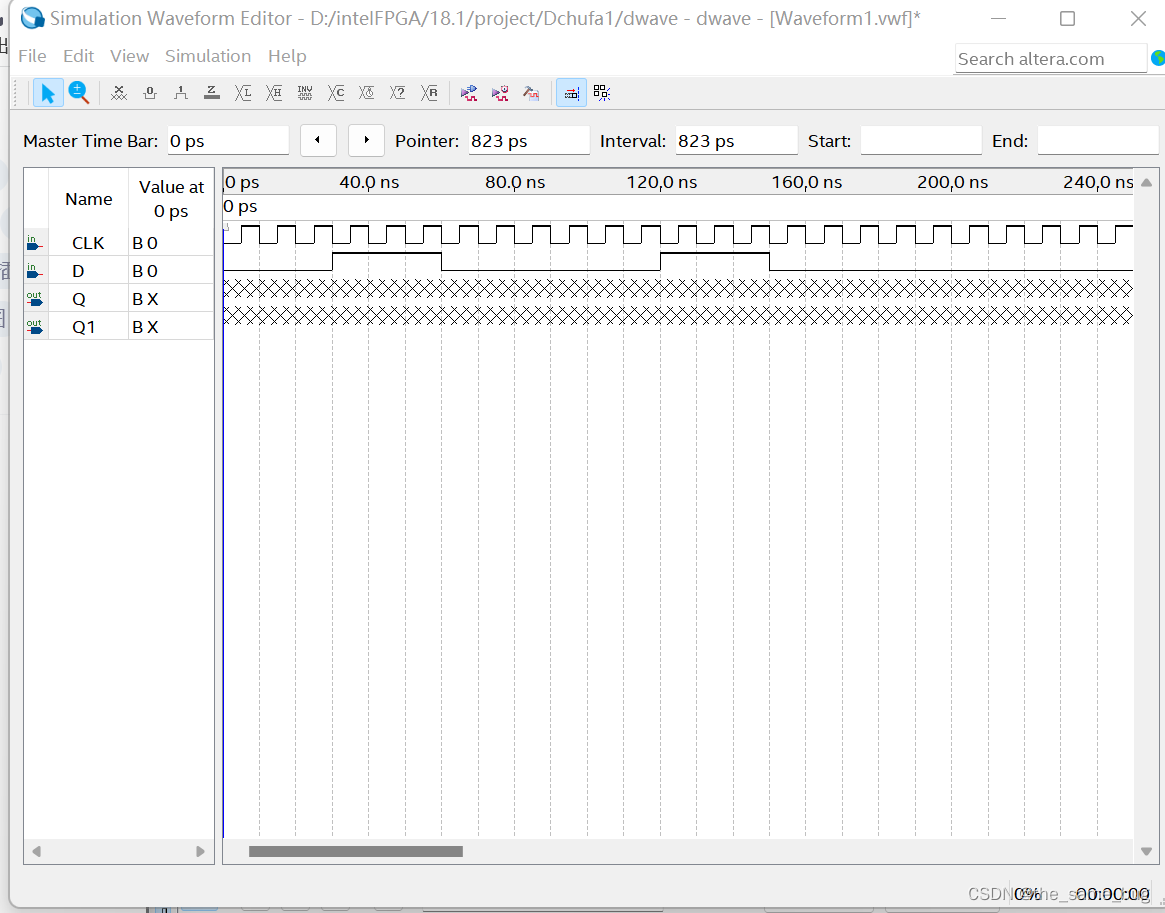

功能仿真

时序仿真

三、用Verilog语言实现D触发器及时序仿真

1.创建工程

与上一步相同

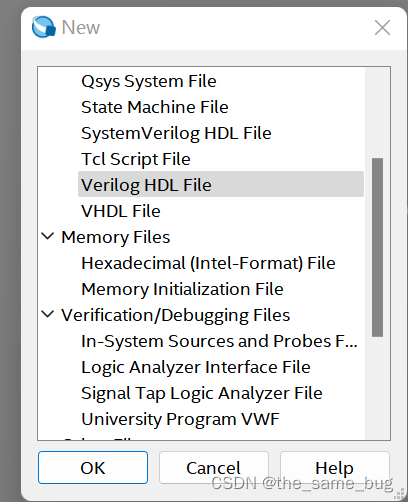

2.创建Verilog HDL 文件

【File】→【New】→【Verilog HDL File】

编写代码:

//dwave是文件名

module dwave(D,CLK,Q);

input D;

input CLK;

output Q;

reg Q;

always @ (posedge CLK)//我们用正的时钟沿做它的敏感信号

begin

Q <= D;//上升沿有效的时候,把d捕获到q

end

endmodule

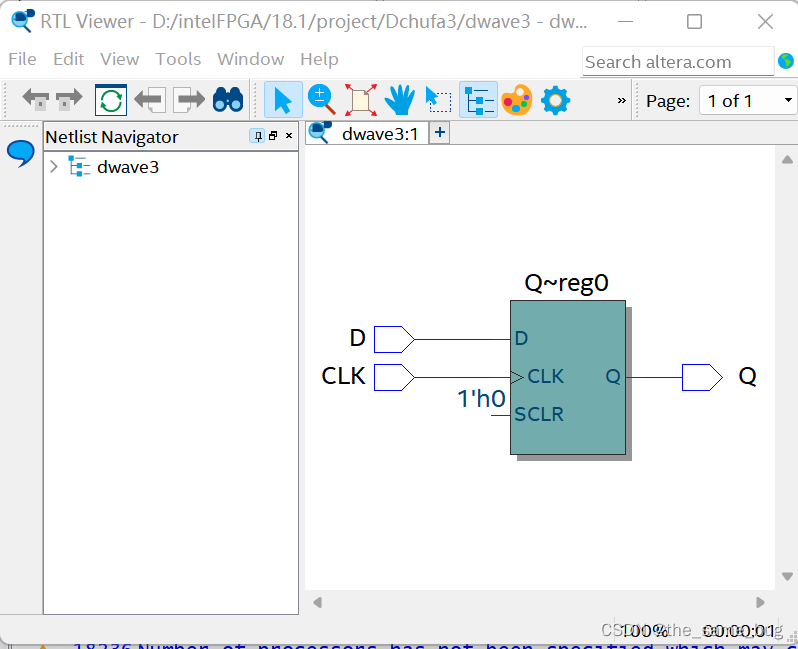

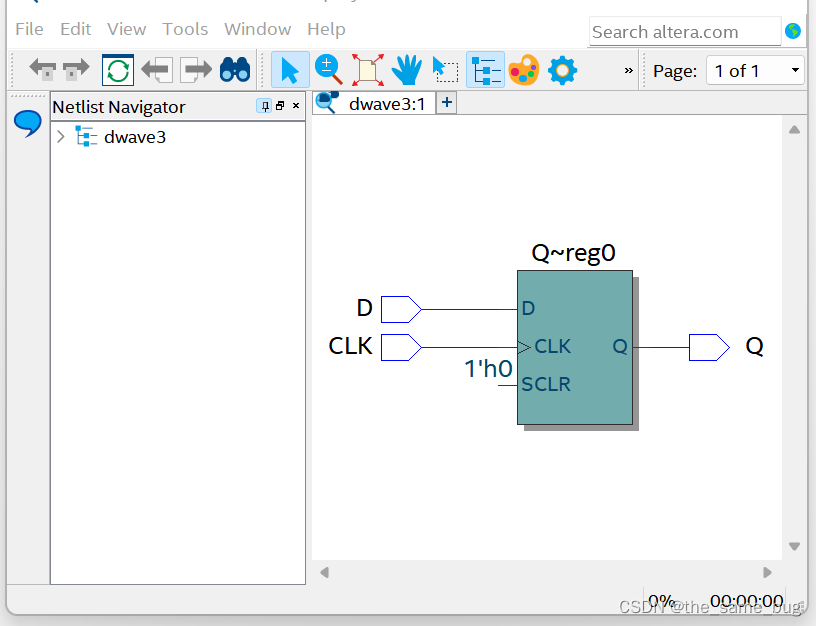

3.编译

保存文件并编译.

使用rtl viewer查看硬件电路图

硬件电路图

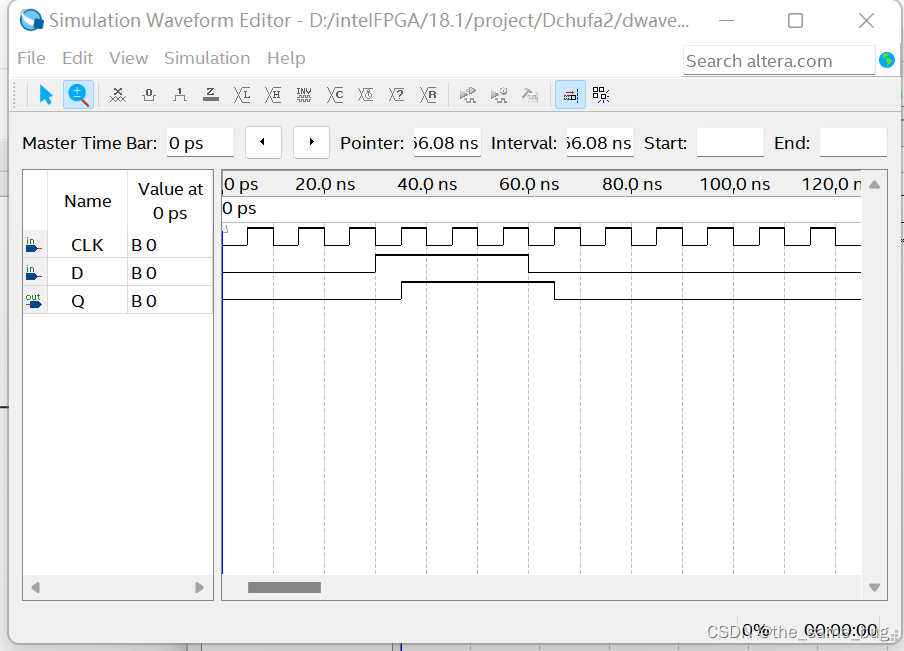

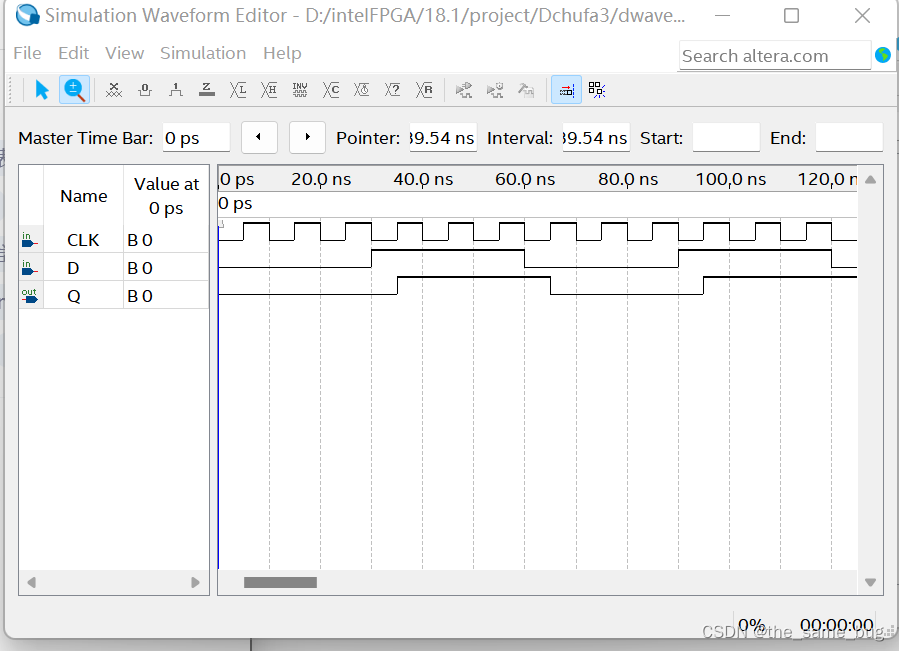

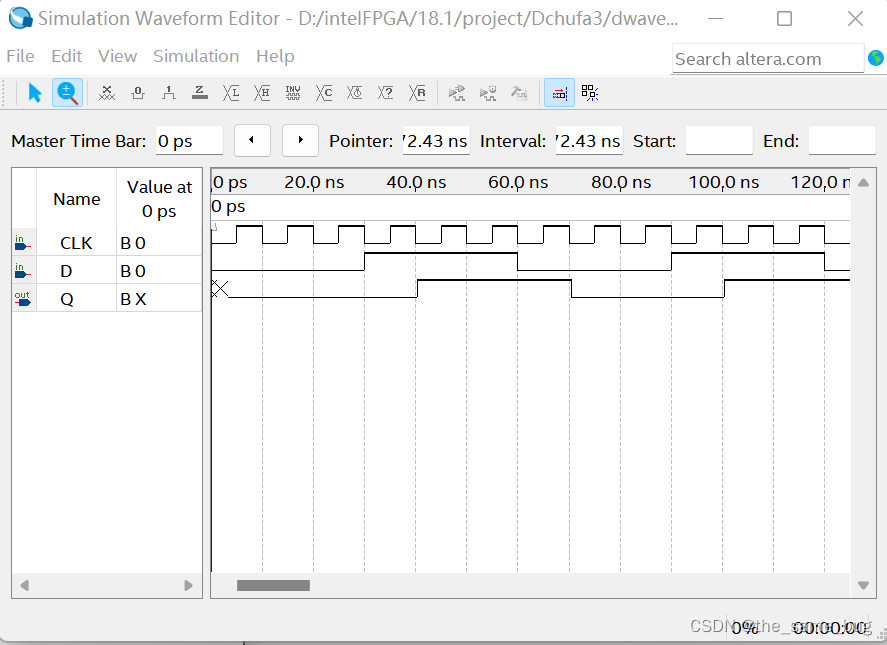

4.仿真

与上一步相同的仿真

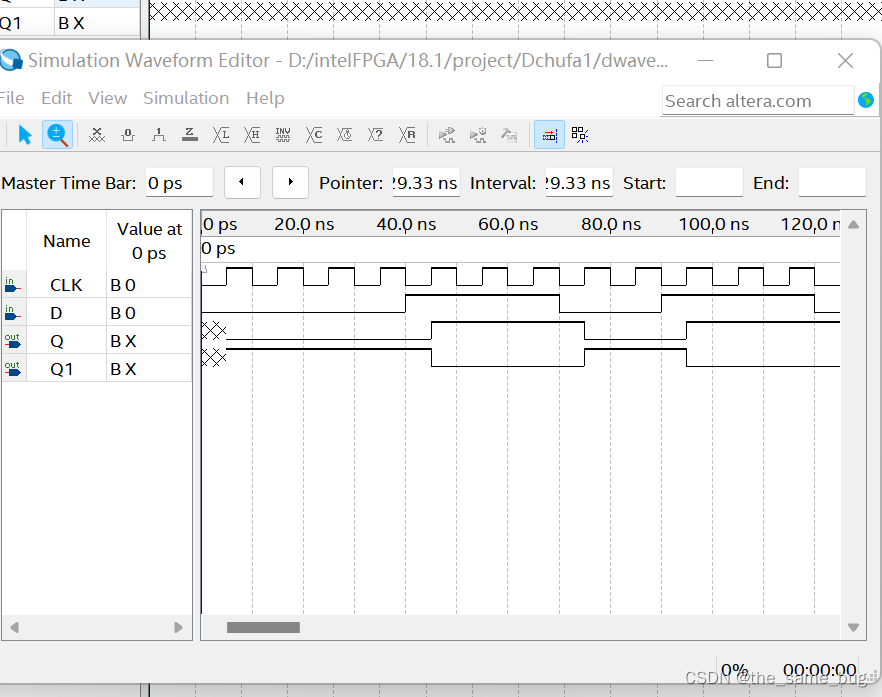

功能仿真

时序仿真

时序仿真

该博客详细记录了在Quartus软件中使用门电路、直接调用D触发器以及用Verilog语言设计D触发器的过程,并进行了仿真验证。通过创建工程、绘制原理图、编写Verilog代码,展示了数字电路基础与嵌入式系统设计的基础步骤。

该博客详细记录了在Quartus软件中使用门电路、直接调用D触发器以及用Verilog语言设计D触发器的过程,并进行了仿真验证。通过创建工程、绘制原理图、编写Verilog代码,展示了数字电路基础与嵌入式系统设计的基础步骤。

3933

3933

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?