偶数次分频(占空比50%)

工作原理:

要实现2n分频,使用一个计数器计数到n-1时,输出信号电平翻转。

例:系统时钟50MHz,需要10k的时钟输出。

需要对系统时钟进行5000分频,计数器计数到2499,out信号翻转,即可实现out为10k。

RTL:

module divider_even

#(parameter even_number = 'd5000)

(

input wire clk ,

input wire rst_n,

output reg clkt

);

reg[11:0] cnt;

//counter to even_number-1

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt <= 12'd0;

else if(cnt == even_number/2-1)

cnt <= 12'd0;

else

cnt <= cnt + 1'b1;

end

//clkt logic

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

clkt <= 1'b0;

else if(cnt == even_number/2-1)

clkt <= ~clkt;

else

clkt <= clkt;

end

endmoduleTb:

`timescale 1ns/1ns

`define clk_period 20

module tb();

reg clk ;

reg rst_n;

wire clkt ;

initial

begin

clk <= 1'b0;

rst_n<= 1'b0;

#50

rst_n<= 1'b1;

#1000

$stop;

end

always #(`clk_period/2) clk <= ~clk;

divider_even

#(.even_number(10))

u1

(

.clk (clk ),

.rst_n(rst_n),

.clkt (clkt )

);

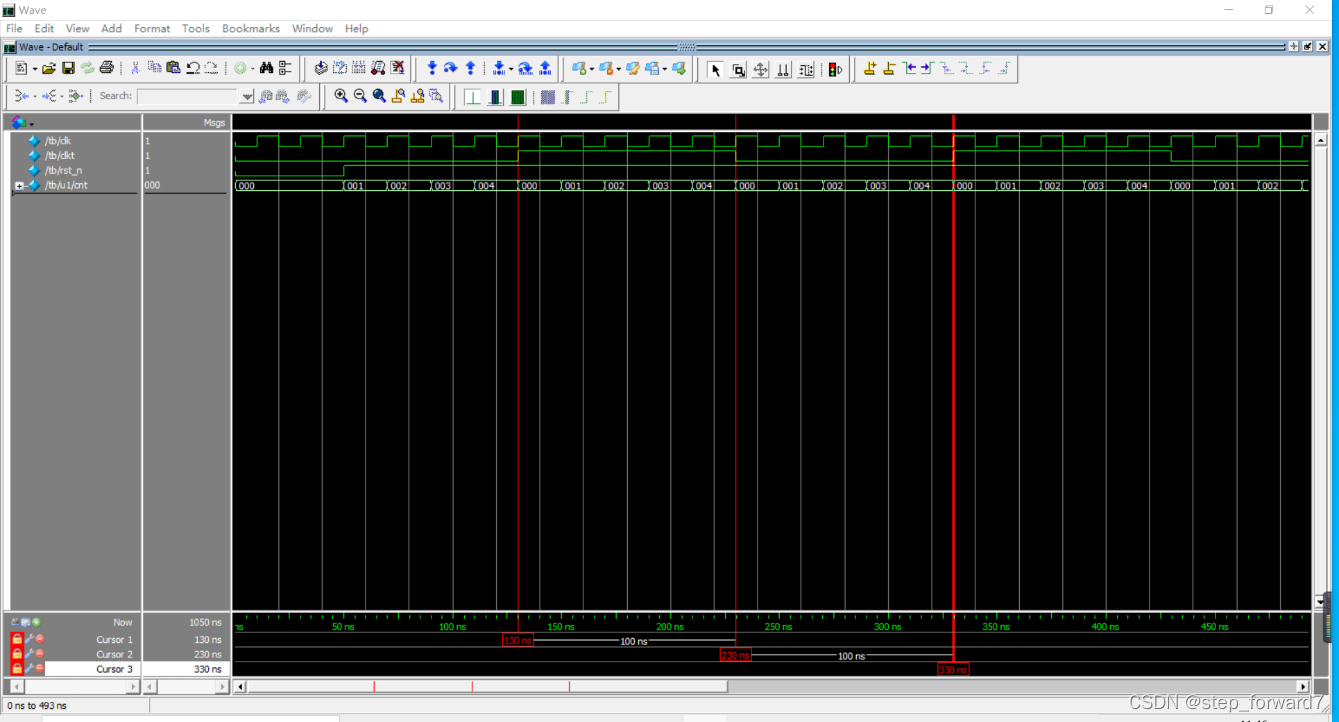

endmoduleModelsim仿真实现10分频

图1

Quartus综合后的电路

本文详细介绍了Verilog设计中偶数次和奇数次分频器的工作原理,通过实例展示2n和2n+1分频器的RTL代码、Tb测试以及Quartus综合结果。讨论了信号赋值策略和时序逻辑的重要性,并分享了避免latch陷阱的方法。

本文详细介绍了Verilog设计中偶数次和奇数次分频器的工作原理,通过实例展示2n和2n+1分频器的RTL代码、Tb测试以及Quartus综合结果。讨论了信号赋值策略和时序逻辑的重要性,并分享了避免latch陷阱的方法。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

743

743

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?