CSI-SRAM:用于低功耗应用的基于 CMOS施密特触发反相器的SRAM单元设计

摘要

在现代数字系统中,随着晶体管数量的增加,功耗也在急剧上升。为了降低功耗,可以考虑采用多个电源电压。本文提出了一种面向低压功能的抗辐射静态随机存取存储器(SRAM)位单元,同时保持高软错误鲁棒性。该提出的SRAM采用一种新颖的双驱动分离反馈机制,并结合多电源电压,在500 mV的低电源电压下仍能有效抵抗因电荷沉积引起的翻转。本文提出了一种基于CMOS施密特触发反相器的新型改进型静态随机存取存储器(SRAM)单元,适用于需要高软错误鲁棒性的存储器架构。与基本CMOS反相器相比,CMOS施密特触发反相器具有更高的稳定性。与基于13T SRAM单元的存储器架构相比,提出的SRAM单元延迟降低了65-70%,功耗减少了80-85%,读取稳定性提高了60-70%。相关结果已在Cadence平台上使用Virtuoso工具,基于45纳米CMOS技术进行了验证。

关键词 —临界电荷,静态随机存取存储器(SRAM),抗辐射加固,6T SRAM单元,13T SRAM单元,CMOS施密特触发反相器。

引言

存储器是用于存储数字数据的电路。现代数字系统能够以更快的速度存储和读取大量数据。为了降低延迟、功耗以及温度波动的影响,采用低电压电路设计,即工作在亚阈值区。当电路在亚阈值区运行时,由于降低了静态和动态功耗,可实现超低功耗[1]。

在数字电路中,地面环境中的α粒子、宇宙射线会产生高能离子,从而引发软错误[2]。当敏感节点处收集的电荷(Qcoll)超过临界电荷(QCrit)时,数据可能翻转或损坏。

降低软错误的有效方法是引入额外的电路以实现错误检测/纠错[3]。临界电荷的值受反相器的栅极/衬底电容以及给定电压[4-6]的影响。一个SRAM单元包含四个可能的敏感打击位置,这通常会减少软错误。如果降低任何SRAM的 VDD ,则可节省漏电功率,从而降低功耗。

本文提出了一种采用CMOS施密特触发反相器设计的抗辐射位单元,适用于低电压操作。该改进型SRAM采用双驱动分离反馈位单元结构,结合多种新颖技术,实现了强健的单粒子翻转抑制并保持了高读取稳定性。

本文组织如下:第二节描述了6T SRAM单元及其缺点。第三节描述了13T SRAM单元。第四节描述了一种提出的SRAM单元,该单元降低了功率和延迟,并提高了读取稳定性。第五节描述了结果与比较。第六节描述了结论。

II. 6T SRAM单元

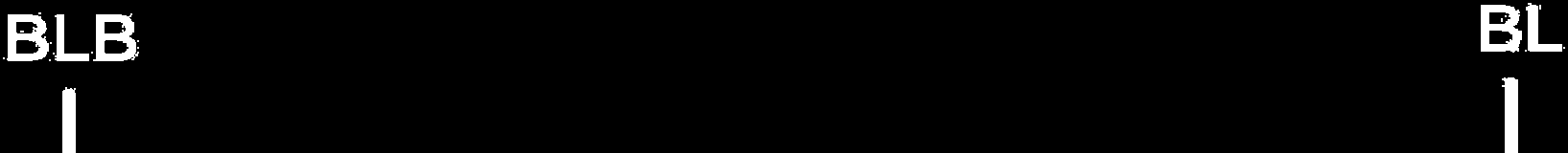

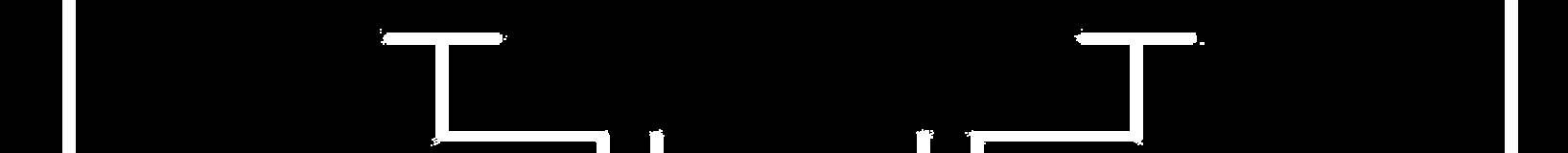

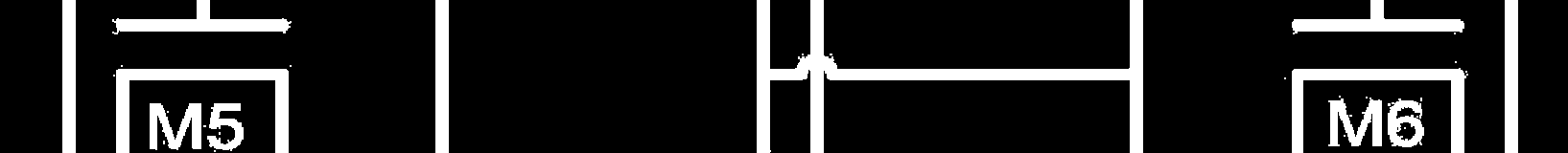

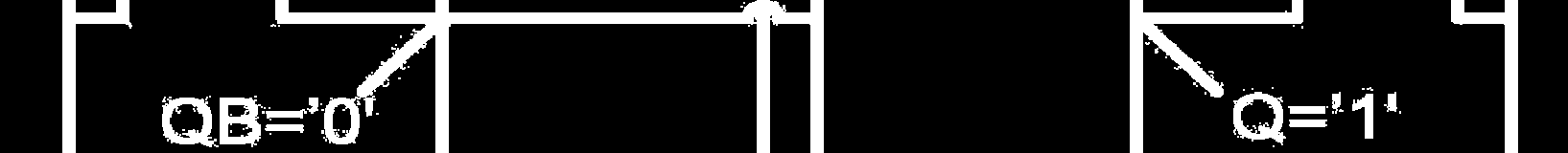

6T SRAM 是一种利用双稳态锁存电路存储单比特信息的存储设备。本节详细描述了标准 6T SRAM 及其工作原理。位单元包含两个相同的 CMOS反相器(INV1 和 INV2),并构成一个正反馈环路。这形成了一个基本的存储设备,即触发器或锁存器,用于存储一位信息,值为 1 或 0。内部节点( Q 和 QB)始终具有互补值。

该交叉耦合对包含两个上拉晶体管(M3和M4)以及两个下拉晶体管(M1和M2)。M5和M6作为访问晶体管,根据WL的值连接反相器和互补对[7]。BL和BLB称为数据线,用于位单元的读写操作,如图1所示。

当WL=0时,由于无内部连接,发生保持操作。当 WL=1时,执行读或写操作。写入时,必须强制两条位线为特定值;读取时,需考虑感知放大器的输出。

A. 6T SRAM局限性

由于不存在反馈节点,标准SRAM容易受到单粒子翻转(SEU)的影响。如果电路中发生任何扰动,该节点处的临界电荷会增加,从而导致位翻转。当器件在低电压下工作时,vt降低,导致软错误概率增加。以下示例说明了 SEU如何导致6T SRAM单元失效。假设一个高能粒子打击了一个逻辑值为1的电路(Q = VDD ,QB = 0 V),并击中截止状态的pMOS晶体管M3的漏极,将产生电荷,从而暂时改变QB的值。因此,6T SRAM单元的抗辐射加固能力极低。为了克服这一问题,必须考虑采用一种替代的 13T SRAM拓扑结构。

III. 13T SRAM单元

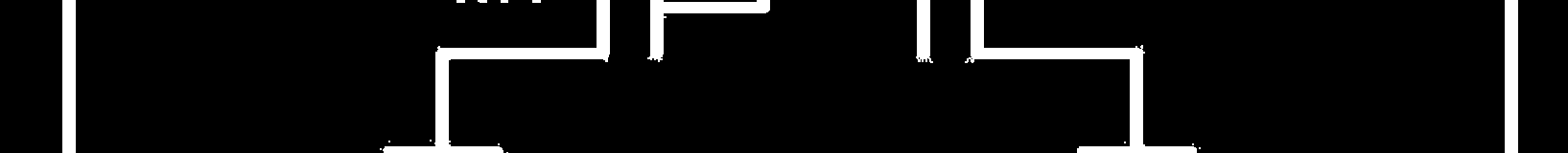

13T SRAM 位单元被用于降低低电压、低功率情况下的软错误概率。该存储可在五个独立节点:Q、QB1、QB2、 A 和 B 中实现,其中以 Q 节点的值为准,如图2所示。输出节点 Q 由一对 CMOS反相器构成,该反相器由晶体管 N3、 P3、N4 和 P4 组成,并由在 QB1 和 QB2 处捕获的取反数据电平驱动。QB1 和 QB2 通过器件 P1、P2、N1 和 N2 连接到 VDD 或 GND,这些器件由弱反馈节点 A 和 B 控制,而 A 和 B 通过由 QB2[8] 控制的一对互补器件(P5 和 N5)连接到 Q 节点。通过将数据值输入至这对强驱动的 CMOS反相器,电路实现了对单粒子翻转(SEU)的防护。

A. 13T SRAM 的操作

13T位单元通过弱反馈节点(A和B)实现写入。使用一对写访问晶体管(N6和N7)将写位线(WBL)连接到节点A和B。访问晶体管由写字线(WWL)控制。当 WWL升高时,A和B被拉向WBL驱动的电平。这种A与B之间的虚假连接使晶体管对N1、P1和N2、P2形成反相器,从而将QB1和QB2驱动至与WBL相反的电平。

13T位单元具有一个单独的读取访问晶体管(N8)。N8由独立的读字线控制,并连接到列共享的读位线,该读位线在读取操作之前被预充电,并根据Q点存储的电压条件性放电。由于存在双驱动反馈,Q点的电压值将保持稳定。该操作比标准SRAM位单元的读取操作更可靠且速度快。

当粒子打击导致位单元的任意节点发生位翻转时,其他四个内部节点的设计能够抑制这种翻转。数据从Q节点读出,因此其他节点上的任何瞬态扰动均可被容忍。例如,由于我们采用了双驱动机制,Q节点上的扰动将迅速被抑制[9][10]。由于QB1和QB2具有独立的特性,QB1和QB2上的扰动无法改变Q节点的状态,并将尽快恢复到原始状态。

B. 13T SRAM 局限性

由于13T SRAM位单元中采用了双分离反馈,其抗辐射加固能力得到提升。但由于晶体管数量增多,导致功耗和延迟增加。为了进一步降低功率和延迟,必须采用一种替代技术,即用CMOS施密特触发反相器取代基本标准 CMOS交叉耦合反相器。

IV. 提出的SRAM单元

A. 位单元设计

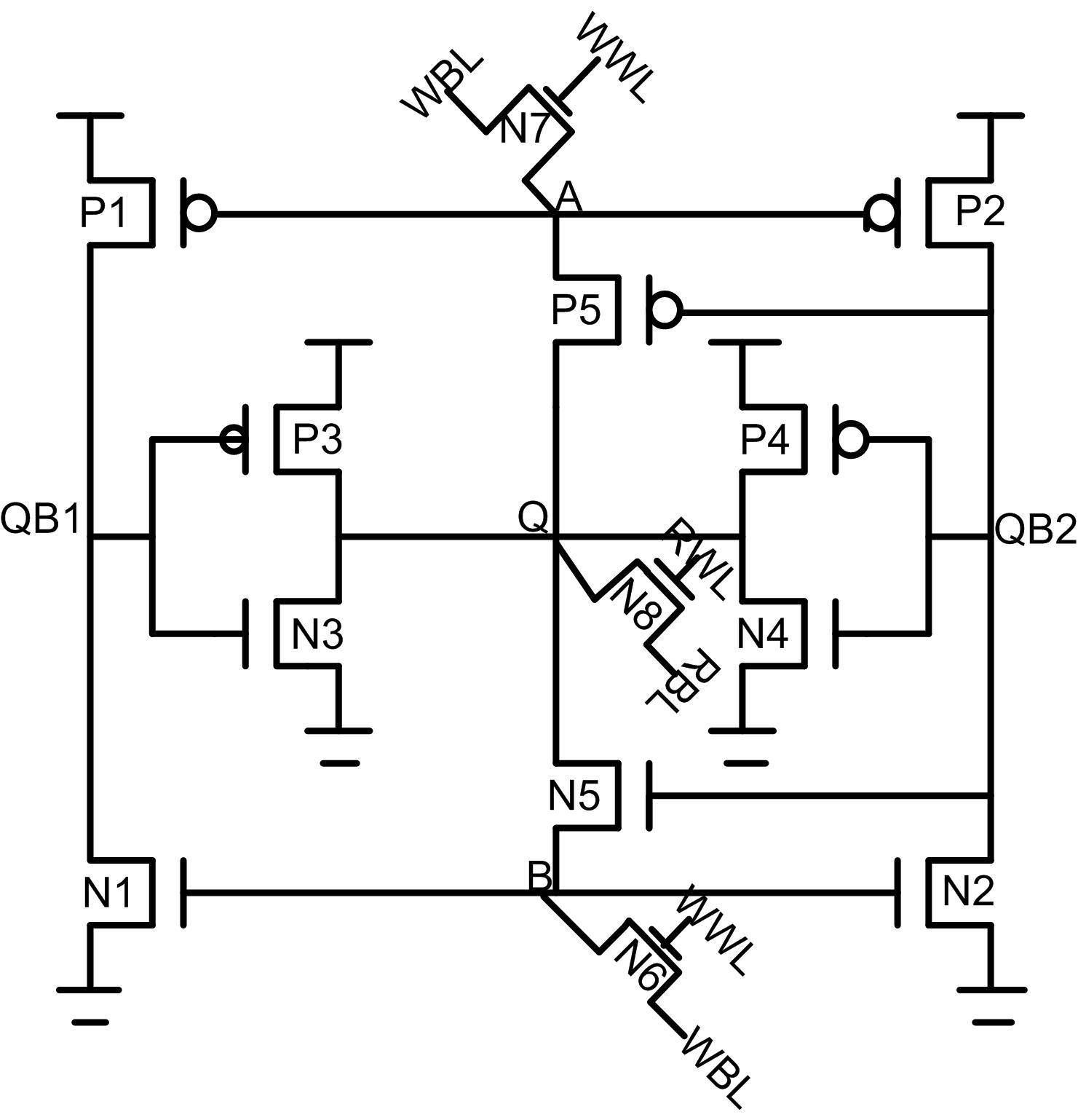

用于低电压操作的SRAM设计已变得越来越流行。提出的位单元专门设计为执行与13T位单元相同的功能,同时降低功耗和延迟,并提高读取稳定性。提出的由21个晶体管组成的SRAM单元的电路图如图4[11-14]所示。该电路的存储机制包含五个独立节点:Q、QB1、QB2、A和 B,其中确切值存储在Q节点上。该节点由一对CMOS施密特触发反相器驱动,该反相器由晶体管P4、P5、P6、P7、P8、P9、N4、N5、N6、N7、N8和N9组成,分别由存储在QB1和QB2处的反相数据电平驱动。QB1和QB2分别通过由弱反馈节点A和B控制的器件P1、P2、N1和N2被驱动至VDD或GND,而A和B通过由QB2控制的一对互补器件(P5和N5)连接到Q。该电路的操作类似于13T位单元。

但为了降低功耗、延迟并提高读取稳定性,我们选用如图 4所示的由3对CMOS施密特触发反相器构成的21T比特单元。N9、N10和N11用作读写访问晶体管。

由于敏感节点处的数据可能被翻转,我们可以通过附加电路中存在的其他节点来减少电路中的单粒子翻转。通过这种方式,与没有反馈节点的传统6T SRAM单元相比,我们可以容忍扰动。如果电路中存在的节点数量更多,数据将不会被翻转。

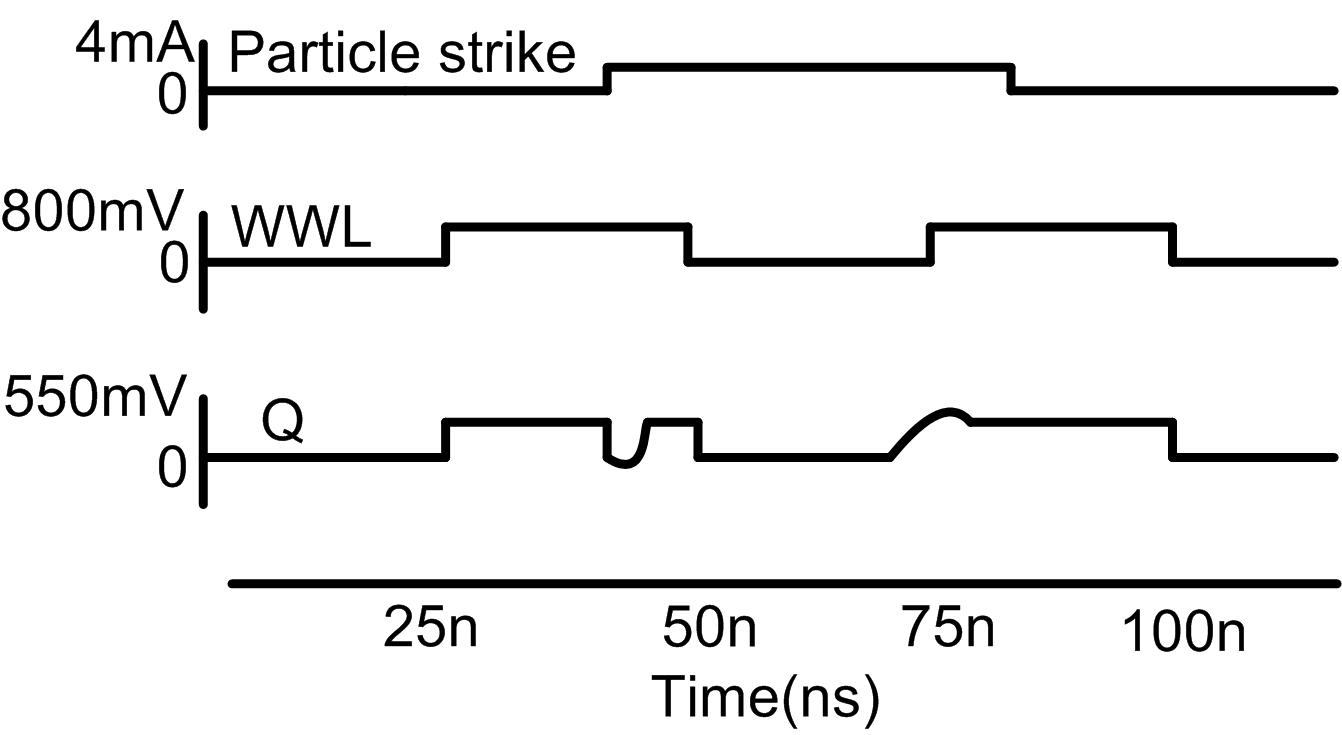

B. 提出的SRAM单元操作

21T比特单元的操作与13T位单元类似。由于与之前的拓扑结构相比晶体管数量增加,功耗将增加。因此,为了降低功耗,我们可以应用多个电源电压连接到如图5所示的电路图。与13T位单元相比,21T比特单元的抗辐射加固能力更强,并且延迟也比13T位单元降低,如图6所示。

V. 结果与比较

A. 功率、延迟和读取稳定性

表I显示了6T、13T、提出的21T位单元以及带有多电源电压的21T位单元的功率、传播延迟和读取稳定性。该表显示了不同拓扑结构下功率、延迟的降低以及读取稳定性的提高。通过该表可以说明,21T位单元是比6T和13T位单元更优的替代拓扑结构。表III显示了6T、13T、提出的21T位单元以及带有多电源电压的21T位单元在不同电源电压下的功率。图7、8、9分别显示了不同拓扑结构的功耗、传播延迟和读取稳定性。

| 参数 | 6T位单元 | 13T位单元 | 提出的位单元 | 提出的位单元与多个电源 |

|---|---|---|---|---|

| 消耗功率 | 3.864微瓦 | 2.786微瓦 | 1.107微瓦 | 0.545微瓦 |

| 传播延迟 | 40.04纳秒 | 60.13纳秒 | 20.2纳秒 | 20.2纳秒 |

| 读取稳定性 | 347.7毫英寸 dB | 495.5毫英寸 dB | 666.2毫英寸 dB | 1023毫英寸 dB |

| 漏电功率 | 60.17纳瓦 | 41.49纳瓦 | 20.11纳瓦 | - |

表II展示了在不同电源电压下的功耗表现:

| 电源电压 / | 6T位单元 | 13T位单元 | 提出的位单元 |

|---|---|---|---|

| 0.8V | 3.864微瓦 | 2.786微瓦 | 1.107微瓦 |

| 0.7V | 2.179微瓦 | 1.767微瓦 | 0.517uW |

| 0.6V | 0.767uW | 0.507uW | 0.153微瓦 |

| 0.5V | 0.148微瓦 | 0.116微瓦 | 0.032微瓦 |

B. 理论计算

本文中使用的不同拓扑结构的平均功耗通过公式(1)进行理论计算。

$$

P_{avg} = \alpha FC_L V_{DD}^2 n \tag{1}

$$

表III给出了不同拓扑结构中功耗的理论值和实际值的比较,其中$V_{DD}$=电源电压(800mV),$C_L$=负载电容,$F$=输入频率,$n$=晶体管数量。

| 参数 | 6T位单元 | 13T位单元 | 提出的位单元 |

|---|---|---|---|

| 理论功率 | 0.363微瓦 | 0.248微瓦 | 0.102微瓦 |

| 实际功率 | 3.864微瓦 | 2.786微瓦 | 1.107微瓦 |

VI. 结论

本文提出了一种用于鲁棒性、低电压和超低功耗应用的21T SRAM位单元。所提出的电路采用了一种新颖的双驱动分离反馈机制,结合具有多电源电压的双CMOS施密特触发反相器,以实现高软错误容限,支持低至500毫伏的稳定操作。进行了粒子打击抑制,显示出在高达500毫伏工作电压下的翻转容忍能力。功耗从3.864微瓦降低至0.545微瓦,最高降低了85%。延迟从60.13纳秒减少到20.2纳秒,最多减少了66.40%。读取稳定性从347.7毫英寸 dB 增加到1023毫英寸 dB,增幅接近65%。漏电功率也从60.17纳瓦降至20.11纳瓦,约降低了70%。

基于施密特触发器的低功耗SRAM

基于施密特触发器的低功耗SRAM

34

34

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?