用于低功耗查找表设计的增强稳定性的静态随机存取存储器单元

S.M. Swamynathan a,b,*,V.Bhanumathi a,b

a印度泰米尔纳德邦哥印拜陀SNS科技学院电子与通信工程系

b印度泰米尔纳德邦哥印拜陀安娜大学区域校区电子与通信工程系

关键词

查找表 SESRAM现场可编程门阵列晶体管

摘要

现场可编程门阵列(FPGA)是用于安全和多媒体处理等实时应用的最新平台。在FPGA映射中,由于使用了可编程互连,存在一定的能耗开销。为了缓解这些限制,设计了一种高能效的六输入查找表(LUT),该查找表采用仅需七个晶体管的稳定性增强型静态随机存取存储器(SESRAM)单元。提出的SESRAM单元通过将读取访问晶体管的尺寸最小化为2nm,并将写入访问晶体管的尺寸最大化为3nm,从而减小了面积、功耗、能耗和延迟,并提高了读取稳定性和写入稳定性。与先前的SRAM设计(如C6T、D2AP8T、LP8T、ST10T和PFC10T)相比,提出的SE7T在0.4伏特下分别将写‘0’延迟和写‘1’延迟降低了62.5%、57.14%、50%、40%、25%以及70%、62.5%、57.14%、50%、40%。采用SE7T的查找表与使用ST10T、D2AP8T和PFC10T的查找表设计相比,写‘0’功耗降低了93.4%、68%、21.21%,写‘1’功耗降低了2%、50.16%、10.13%。

1. 引言

现场可编程门阵列(FPGA)是一种可重构平台,适用于高能效的应用映射。由于其低成本、低功耗、高速度以及在应用映射中的灵活性,FPGA主要被用于数字信号处理(DSP)、多媒体和安全应用中。它与中央处理器(CPU)结合,作为协处理器平台,以满足高性能的实时处理需求[1]。然而,由于可编程互连(PI)的使用及其带来的面积开销,导致能效较低。在近年来的工艺缩放技术中,80%的功耗和60%的延迟来源于可编程互连(PI)[2]。因此,有必要通过降低功耗来减少能耗,从而实现资源高效的嵌入式系统,同时不牺牲其灵活性和性能。

为了提高FPGA器件的能效,研究人员基于阈值电压变化以及聚类、近似和优化等架构改进开展了相关工作[3]。在大多数计算密集型应用中,这些方法无法有效满足能耗需求的精确解决方案。通过高效的映射设计,有可能减少传统FPGA中的互连,从而降低能耗。近年来的FPGA器件设计了大量嵌入式存储块(EMB),这些嵌入式存储块(EMB)用于存储输入、中间和输出数据。但在大多数应用中,大量内存未被使用[4]。

现场可编程门阵列(FPGA)架构有两种类型,即细粒度和粗粒度FPGA。细粒度现场可编程门阵列架构无法执行需要大量逻辑和布线资源存储空间的粗粒度应用,例如滤波和复杂功能。然而,FPGA中的数字信号处理模块(DSP blocks)能够有效映射高比特流下的粗粒度功能。在低比特流情况下,由于资源使用减少,能耗改善略有提升[5]。以往的研究工作映射了MCNC和ISCAS基准电路,这些被视为细粒度功能。这些复杂功能被映射为嵌入式存储块(EMB)中的二维查找表,以有效降低能耗[6,7]。

本文中,我们设计了一种利用低功耗存储模块并基于125nmCMOS技术实现的具有高读写稳定性的SESRAM单元。分析表明,与现有方法相比,所提出的六输入查找表在功耗和延迟方面表现更优。

1.1. 相关工作

最近,FPGA的使用有所改进,被用于在嵌入式平台上实现大多数计算密集型应用的高速度和高性能。谢磊等人提出了一种基于忆阻器交叉阵列布尔逻辑的映射方法和优化技术[8]。忆阻器交叉阵列是CMOS技术的替代方案,涉及可靠性、非易失性和增益等参数。它采用布局布线方法,以实现电路设计在交叉阵列上的高效映射。申楚瑜等人提出了一种划分方法[9]来执行并行操作,该方法通过对子电路应用技术映射来提高速度。

S. 纳维德·沙鲁齐(S. Navid Shahrouzi)等人提出了一种多端口存储器架构[10],该架构利用具有随机数量读/写端口的块状存储器(BRAM)。哈桑·阿尔·阿塔特(Hassan Al Atat)等人提出了一种新方法[11],该方法利用传统嵌入式存储块(EMB)将变量映射到存储器块中。在此方案中,每个存储体均包含一个读端口和一个写端口。但此前大多数FPGA中的存储体采用的是双读/写端口。Somnath Paul 和 Saibal Mukhopadhyay 提出了一种协同设计方法[12],其中选择非对称二维存储器阵列,在空间计算中将应用映射到查找表(LUT)中。所使用的映射是一种内容感知方法,专注于改善查找表(LUT)中的逻辑0或逻辑1。Sparsh Mittal 针对嵌入式应用提出了多种电源管理技术[13],其采用动态电压频率调节技术以实现节能。阿南达鲁普·戈什(Anandaroop Ghosh)等人提出了在FPGA中利用数字信号处理器(DSP)与逻辑映射相结合的异构应用映射[14]。通过对处理单元(PI)中的操作进行分解、融合和打包,并通过截断输入的位宽来略微降低精度,从而减少能耗和面积。

在参考文献[15]中提出了时序约束的内存映射和关键路径延迟模型。T‐Map用于计算存储器块的数量,并将其划分为关键部分和非时序关键部分。参考文献[16]中提出了内存映射输入输出(MMIO),其优选使用双端口BRAM。通过将存储器映射到外部闪存,减少了BRAM的数量。Maryam Nobakht等人提出了一种具有交织结构的7T SRAM单元[17],以减小面积并实现低延迟开销下的高性能。单级查找表采用专用多路复用器[18]设计,基于部分确认机制以减小查找表的尺寸。这可以通过从完成检测(CD)模块中移除输入来实现。参考文献[19]中提出了适用于物联网(IoT)应用的读写外设辅助方法。

2. 背景

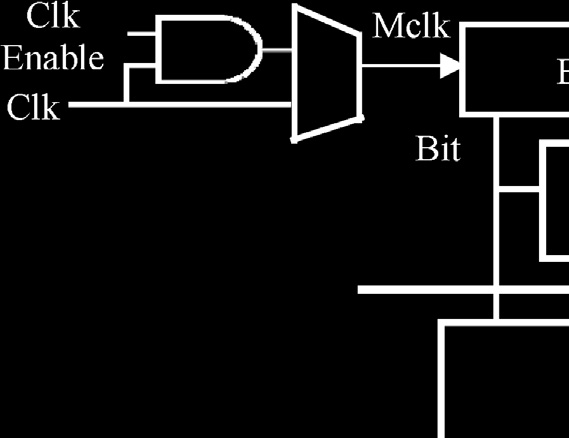

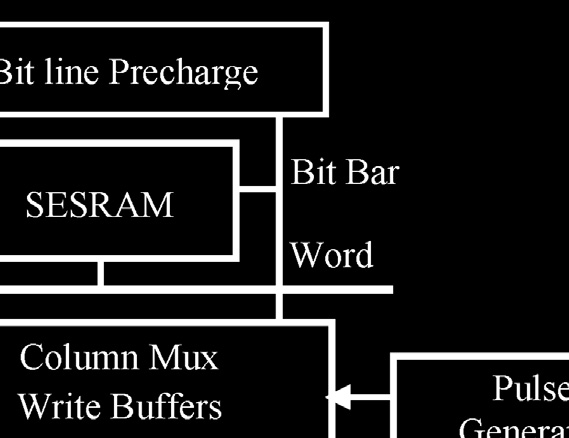

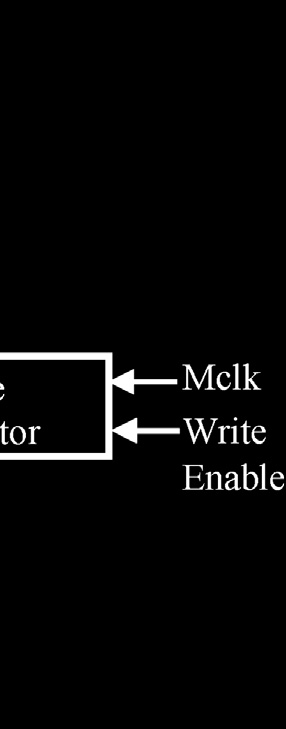

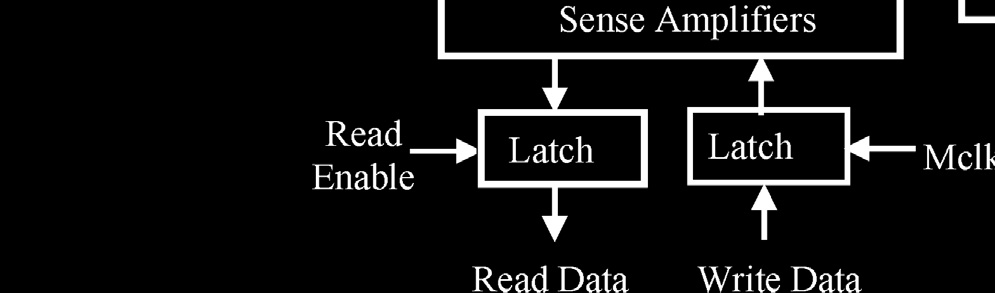

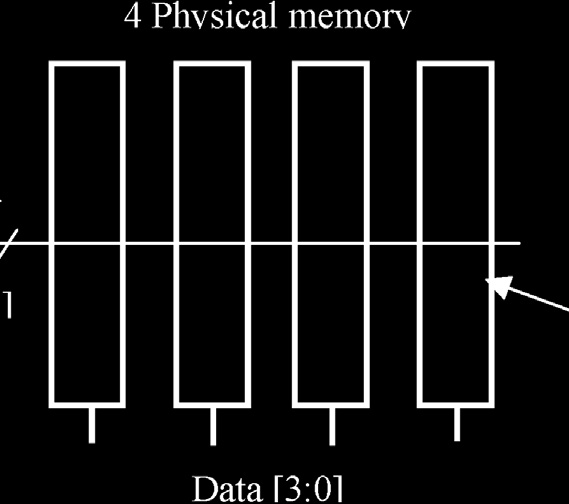

通常,静态随机存取存储器在读和写操作期间的有功功率[20,21]消耗在位线的充放电上。降低静态随机存取存储器有功功率[22]的最佳方法是选择先进工艺。同步SRAM的特性导致高效的嵌入式存储器映射。每个EMB端口由一个或多个读/写(R/W)信号和时钟信号控制。嵌入式存储器的内部架构如图1所示。嵌入式存储器中的数据移动由使能信号直接或间接控制。

在读操作期间,当存储器端口时钟(Mclk)被使能为高电平时,位线预充电至Vcc,地址被解码并激活字线。感测放大器检测到位线之间的差异,并将读取的数据锁存到列多路复用器中,该过程由读使能信号触发。在写操作期间,位线预充电至Vcc,然后写使能信号和Mclk生成脉冲并传递给写缓冲器。根据写地址的解码结果,字线被激活,数据被存储到RAM单元中。

位线的预充电降低了读写操作中的动态功耗[23]。时钟使能信号用于消除字线解码和内部预充电。通过禁用时钟信号,可降低嵌入式存储器端口的动态功耗。大多数先进的FPGA使用嵌入式存储块(EMB)。Cyclone II、Altera Stratix II、Virtex II和Virtex IV具有时钟使能和写使能作为控制信号,但没有为读操作提供单独的使能信号。

2.1. 提出的方法

在FPGA实现中,将应用程序映射到多端口存储器是一个具有挑战性的问题,因为BRAM只有两个端口。如果需要超过两个端口,则必须构建多端口存储器。它用于形成存储体,以获得需要高带宽的完整存储空间。它有两列,并因其具有独立的读端口和写端口而充当双端口存储器。它也可用作单端口存储器。它适用于不同的数据宽度,例如16Kx1、8Kx8、4Kx4等。

2.2. 典型RAM映射流程

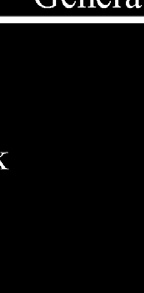

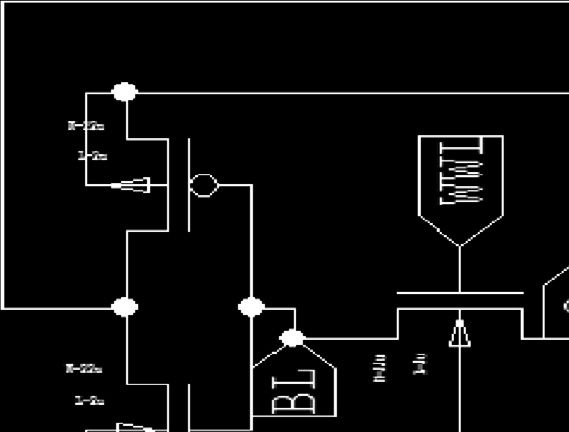

移位寄存器、FIFO、单端口和双端口存储器等RAM组件通过EMB实现。RAM在寄存器传输级(RTL)中表示,其映射如图2所示。

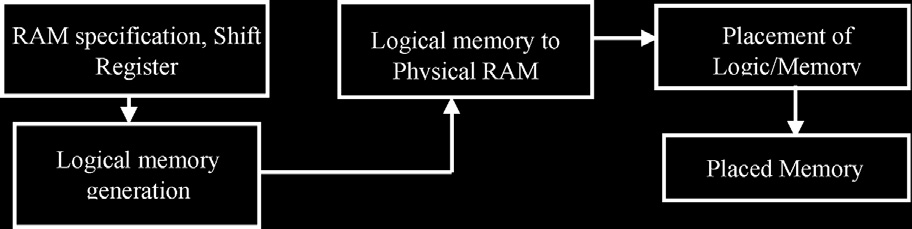

逻辑存储器由FPGA编译器创建,具有某些期望的行为。这些逻辑RAM被转换为多个RAM块,与嵌入式存储块(EMB)的大小相匹配。这些RAM块和控制逻辑被放置在嵌入式存储块(EMB)和逻辑资源中。EMB的大小基于地址的位置,称为深度,每个存储器的数据输出位数称为宽度。嵌入式存储块(EMB)通过编码实现深度与各种宽度配置的组合,以达到灵活性。

在许多情况下,逻辑存储器的大小与EMB的大小并不匹配。因此,RAM映射流程主要考虑延迟优化和资源利用率。例如,图3描述了将一个4K × 4逻辑存储器映射到四个4K × 1嵌入式存储块(EMB)的过程。单个存储器块被视为4K × 1,因此每个地址位置位于各自的块中。它不需要任何外部电路。在访问每个逻辑存储器期间,四个存储器块被激活(见图4)。

2.3. 提出的SESRAM单元

所提出的SESRAM单元具有高读取稳定性和写入稳定性,同时实现低功耗。它利用低功耗存储块来存储当前信息。由于该提出的SESRAM单元具有最快的读写访问时间,因此设计了高效的内存阵列。该单元克服了亚阈值SRAM的局限性,例如噪声容限低、漏电功耗高以及对工艺、电压和温度(PVT)变化的敏感性。

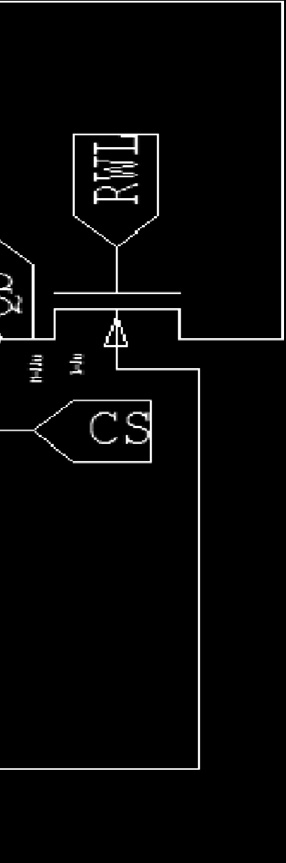

3. 单元架构

提出的SESRAM单元包含两个n型MOS晶体管M1和M2作为写入访问晶体管,如图4所示。通过这些访问晶体管,向SRAM单元提供输入。位线用于写入一位信息,BLB则执行其互补操作。两者同时工作。锁存器由晶体管M3、M4、M5、M6和M7构成。其中M3和M4是连接到电源电压Vdd的PMOS晶体管,M6和M7是接地的NMOS晶体管。M5是一个反馈钳位晶体管,用于切断Vdd与地之间的通路。控制信号(CS)用于控制晶体管M5的导通。利用该晶体管可提高噪声容限并降低漏电功耗。

电路的漏电功耗取决于晶体管的阈值电压(Vth)、晶体管的宽长比(W/L)以及电源电压(Vdd)。漏电功耗定义如下,

$$

P_{leakage} = V_{dd} \times I_{leakage}

$$

其中$P_{leakage}$表示漏电功耗,$I_{leakage}$表示漏电流。在深亚微米技术中,大部分功耗主要由漏电流引起,可通过以下公式计算

$$

I_{leakage} = I_0 e^{\frac{V_{GS} - V_{THf} - \eta V_{DS} + \gamma V_{BS}}{n V_T}} \left(1 - e^{-\frac{V_{DS}}{V_T}}\right)

$$

$$

I_0 = \mu C_{ox} \frac{W}{L} V_T^2 e^{1.8}

$$

$$

V_T = \frac{K T}{q}

$$

其中,$V_T$为热电压,$K$为玻尔兹曼常数,$q$为电子电荷,$\mu$为载流子迁移率,$C_{ox}$为栅氧化层电容,$V_{THf}$为由偏置电压引起的阈值电压,$V_{GS}$为栅源电压,$V_{DS}$为漏源电压,$V_{BS}$为体源电压。

为了增强读写稳定性,读取访问时优先采用最小尺寸晶体管,写入稳定性则优先采用最大尺寸晶体管。SESRAM的读和写操作的真值表如表1所示。

| 操作 | WWL | RWL | BL | BLB | CS |

|---|---|---|---|---|---|

| 写1 | 1 | 0 | 1 | 0 | 0 |

| 写0 | 1 | 0 | 0 | 1 | 1 |

| 读1 | 0 | 1 | 1 | 1 | 0 |

| 读0 | 0 | 1 | 1 | 1 | 1 |

| 保持1 | 0 | 0 | 0 | 0 | 0 |

| 保持0 | 0 | 0 | 0 | 0 | 1 |

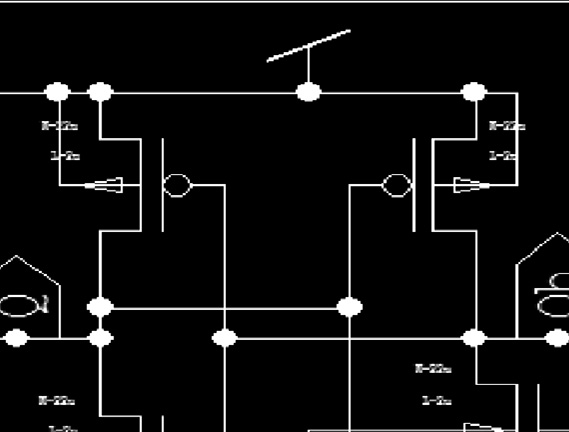

4. 控制信号生成

控制信号生成的逻辑图如图5所示。它用于生成反馈控制信号。通过真值表实现控制信号生成的工作操作如表2所示。控制信号基于WWL、数据输入(D)以及D锁存器中存储的前一输出Q(n−1)。Q(n−1)的值等于D(n−1)的值。如果WWL的值为零,则D锁存器保持输出的先前状态,如公式(5)所示。

$$

CS = ((\overline{WWL}) \& (\overline{Q})) | (WWL \& (\overline{D}))

$$

$$

Q(n−1) = D(n−1)

$$

| 数据D | WWL | Q (n−1) | D (n−1) | CS |

|---|---|---|---|---|

| 0 | X | 0 | 0 | 1 |

| 0 | X | 1 | 1 | 0 |

| 0 | X | 0 | 0 | 1 |

| 0 | X | 1 | 1 | 0 |

| 1 | 0 | X | X | 1 |

| 1 | 1 | X | X | 0 |

| 1 | X | X | X | — |

5. SESRAM阵列

存储器阵列是一个二维阵列的SRAM单元,每次存储单比特。它包含M个数据位和N个地址位,即具有2^N行和M列。行数或字数称为深度,字长和列数称为宽度。因此,阵列大小通过深度和宽度相乘得到,即 2^N × M。CS作为总线架构,由所提出的存储器阵列共享。2 kb(32 × 64)存储器阵列如图6所示。

如果执行写操作,CS将保持其先前的状态。只有在下一次写操作时,其位置才会改变。因此,在读操作和保持操作中,CS保持相同的位置。在写操作期间,WWL和BL从SRAM阵列中选择SESRAM单元,并将信息写入该单元。类似地,通过读取特定的位线来执行读操作。灵敏放大器检测电源电压Vdd与位线电压之间的电压差,从而识别SRAM单元中存储的位。

6. 六输入查找表

采用提出的SESRAM单元基于125 nm CMOS技术设计了六输入查找表,如图7所示。为了实现高噪声容限和低漏电功耗,在查找表设计中优选控制逻辑电路以激活每一个SESRAM单元。该设计需要64个SES-RAM单元和一个64:1多路复用器。

可重构逻辑是现场可编程门阵列中使用的基本原理。如果数字系统被编程后,与输入对应的输出将存储在查找表的SRAM单元中。

7. 结果与讨论

提出的SESRAM单元在Tanner EDA中采用125纳米技术并使用1000次蒙特卡洛仿真进行仿真。通过版图后仿真确定了漏电功耗、读写功耗、延迟、读静态噪声容限、写静态噪声容限和保持静态噪声容限等各种参数。这些参数在慢‐慢(SS)、快‐快(FF)、典型‐典型(TT)、慢‐快(SF)和快‐慢(FS)角下,于温度范围250°C–1250°C内变化进行取值。放大器检测电流下降及其漏电流的情况如图8所示。

不同静态随机存取存储器单元在变化电源电压下的漏电功耗如图9所示。当静态随机存取存储器单元处于保持模式或静态模式时,电流从电源电压流向地,这种电流称为漏电流。设计中的漏电流与该设计的漏电功耗成正比,即保持模式下的功耗。现有的静态随机存取存储器单元,如C6T SRAM和LP8T SRAM,并未利用堆叠效应来减少漏电流,且其噪声容限较低。PFC10T SRAM单元[24]使用两个不同的控制信号,需要两个外部晶体管来驱动这些控制信号。使用外部晶体管会导致功耗。为解决这些问题,提出了SESRAM单元,其漏电流可通过堆叠效应和控制信号进行控制。堆叠是指多个串联的晶体管,通过关断其中任意一个堆叠晶体管来降低亚阈值漏电流。在保持模式下,借助反馈控制信号可实现漏电流的减少,因为它切断了电源电压与地之间的通路。

与传统6T SRAM(C6T)、差分数据感知8T SRAM(D2AP8T)、低功耗8T SRAM(LP8T)、基于施密特触发器的10T SRAM(ST10T)和正反馈控制10T SRAM(PFC10T)相比,提出的SESRAM单元在0.4伏特下分别将漏电流和漏电功耗降低了5.55%、38.88%、10%、8.33%和20%、50%、40%、30%、20%。

各种SRAM单元在温度从25 °C变化到 125 °C时的漏电功耗如图10所示。与C6T、ST10T和PFC10T相比,提出的SESRAM单元在125 °C时的漏电功耗分别降低了82.85%、20%和70%。

图11 显示了不同SRAM单元在读、写和保持模式下的噪声容限对应的电源电压值。读静态噪声容限(RSNM)通过在其中一个存储节点施加直流噪声电压源进行计算,并在读取模式下测量其对另一个存储节点的影响,同时保持WWL为‘0’且RWL为‘1’。保持静态噪声容限(HSNM)是在保持模式下进行测量。反馈控制信号使SRAM单元形成非对称架构。在写入模式下,通过施加带有噪声的直流电压来测量写静态噪声容限(WSNM),其计算方式与RSNM类似。从该对比图可以看出,与现有SRAM单元相比,所提出的SESRAM提升了RSNM、WSNM和HSNM。

通过将电源电压从0.2变化到0.4,计算了多种静态随机存取存储器单元的写0延迟和写1延迟,其比较图如图12所示。与C6T、D2AP8T、LP8T、ST10T和PFC10T等先前的SRAM设计相比,提出的SE7T在0.4伏特时分别将写‘0’延迟和写1延迟降低了62.5%、57.14%、50%、40%、25%以及70%、62.5%、57.14%、50%、40%(见图13)。

写‘0’功耗和各种SRAM单元的写‘1’功耗如图13所示。与之前的SRAM单元设计相比,所提出的SESRAM在读取和写入稳定性有所改善的同时,降低了写‘0’功耗和写‘1’功耗。

表3 描述了不同类型SRAM单元的写入‘0’ PDP和写入‘1’ PDP。与C6T、D2AP8T、LP8T、ST10T、PFC10T相比,提出的SESRAM单元将写入‘0’ PDP和写入‘1’ PDP分别降低了76%、71.5%、64%、50.90%、22.85%以及59.34%、33%、46.82%、39.9%。

| SRAM设计 | 写‘0’功耗延迟积(飞焦) | 写‘1’功耗延迟积(飞焦) |

|---|---|---|

| C6T | 0.225 | 0.246 |

| D2AP8T | 0.19 | 0.1 |

| LP8T | 0.15 | 0.126 |

| ST10T | 0.11 | 0.11 |

| PFC10T | 0.07 | 0.09 |

| SE7T | 0.054 | 0.067 |

使用SESRAM的六输入查找表的延迟和功耗分析,表4。

| 使用的技术 | 写入1延迟(纳秒) | 写入1功耗(纳瓦) | 漏电功耗 (nW) |

|---|---|---|---|

| ST10T | 32.2 | 93.18 | 12.07 |

| D2AP8T | 6.5 | 183.2 | 8.13 |

| PFC10T | 2.64 | 101.6 | 11.35 |

| SE7T | 2.08 | 91.3 | 9.05 |

表4 展示了采用SRAM单元的六输入查找表的漏电功耗、写入‘1’功耗和写入‘1’延迟对比。设计一个六输入查找表需要一个64:1多路复用器和64个SRAM单元。与采用ST10T、D2AP8T和PFC10T的查找表设计相比,采用SE7T的查找表将写入‘1’延迟降低了93.4%、68%、21.21%,写入‘1’功耗降低了2%、50.16%、10.13%。

各种查找表设计的PDP(功耗延迟积)与电源电压对比图如图14所示。使用SESRAM的提出的查找表相较于D2AP8T、ST10T和PFC10T,PDP分别降低了33.33%、25.92%、16.66%和10%。

8. 结论

本文提出了一种采用单控制信号的SESRAM单元。该提出的SESRAM单元用于实现六输入查找表。所提出的查找表基于125纳米技术设计。实验结果表明,在0.4伏特下,与传统C6T、D2AP8T、LP8T、ST10T和PFC10T相比,所提出的查找表分别将漏电流和漏电功耗降低了5.55%、38.88%、10%、8.33%和20%、50%、40%、30%、20%。与先前的SRAM设计(如C6T、D2AP8T、LP8T、ST10T和PFC10T)相比,所提出的SE7T在0.4伏特下分别将写‘0’延迟和写1延迟降低了62.5%、57.14%、50%、40%、25%和70%、62.5%、57.14%、50%、40%。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?