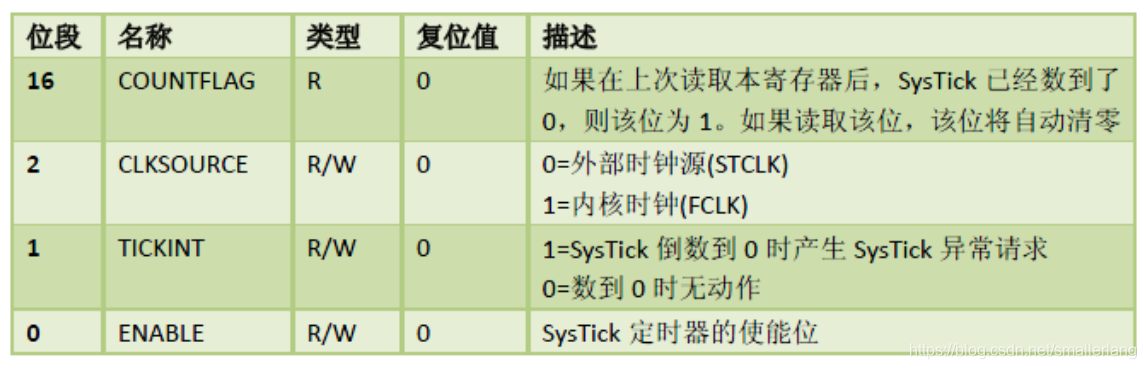

SysTick->CTRL的各位定义如下:

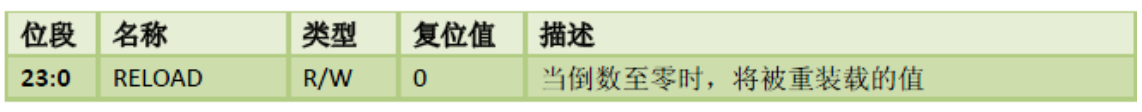

SysTick->LOAD的各位定义如下:

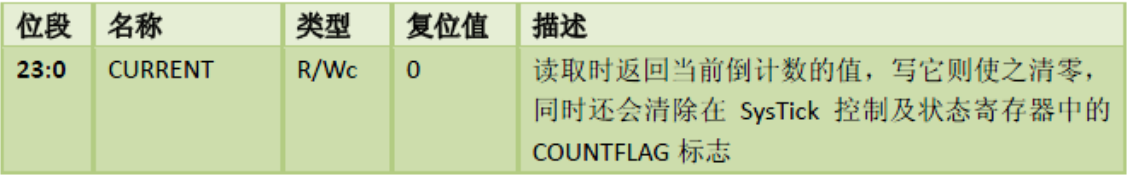

SysTick->VAL的各位定义如下:

/**

* @brief System Clock Configuration

* @retval None

*/

void SystemClock_Config(void)

{

RCC_OscInitTypeDef RCC_OscInitStruct = {0};

RCC_ClkInitTypeDef RCC_ClkInitStruct = {0};

RCC_PeriphCLKInitTypeDef PeriphClkInitStruct = {0};

/** Configure the main internal regulator output voltage

*/

__HAL_RCC_PWR_CLK_ENABLE();

__HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE1);

/** Initializes the RCC Oscillators according to the specified parameters

* in the RCC_OscInitTypeDef structure.

*/

RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSE;

RCC_OscInitStruct.HSEState = RCC_HSE_ON;

RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON;

RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSE;

RCC_OscInitStruct.PLL.PLLM = 25;

RCC_OscInitStruct.PLL.PLLN = 432;

RCC_OscInitStruct.PLL.PLLP = RCC_PLLP_DIV2;

RCC_OscInitStruct.PLL.PLLQ = 2;

if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK)

{

Error_Handler();

}

/** Activate the Over-Drive mode

*/

if (HAL_PWREx_EnableOverDrive() != HAL_OK)

{

Error_Handler();

}

/** Initializes the CPU, AHB and APB buses clocks

*/

RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_HCLK|RCC_CLOCKTYPE_SYSCLK

|RCC_CLOCKTYPE_PCLK1|RCC_CLOCKTYPE_PCLK2;

RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK;

RCC_ClkInitStruct.AHBCLKDivider = RCC_SYSCLK_DIV1;

RCC_ClkInitStruct.APB1CLKDivider = RCC_HCLK_DIV4;

RCC_ClkInitStruct.APB2CLKDivider = RCC_HCLK_DIV2;

if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_7) != HAL_OK)

{

Error_Handler();

}

PeriphClkInitStruct.PeriphClockSelection = RCC_PERIPHCLK_USART1;

PeriphClkInitStruct.Usart1ClockSelection = RCC_USART1CLKSOURCE_PCLK2;

if (HAL_RCCEx_PeriphCLKConfig(&PeriphClkInitStruct) != HAL_OK)

{

Error_Handler();

}

/** Enables the Clock Security System

*/

HAL_RCC_EnableCSS();

}

void SystemClock_Config(void) --> HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_7)

HAL_StatusTypeDef HAL_RCC_ClockConfig(RCC_ClkInitTypeDef *RCC_ClkInitStruct, uint32_t FLatency)

{

uint32_t tickstart = 0;

/* Check Null pointer */

if (RCC_ClkInitStruct == NULL)

{

return HAL_ERROR;

}

/* Check the parameters */

assert_param(IS_RCC_CLOCKTYPE(RCC_ClkInitStruct->ClockType));

assert_param(IS_FLASH_LATENCY(FLatency));

/* To correctly read data from FLASH memory, the number of wait states (LATENCY)

must be correctly programmed according to the frequency of the CPU clock

(HCLK) and the supply voltage of the device. */

/* Increasing the CPU frequency */

if (FLatency > __HAL_FLASH_GET_LATENCY())

{

/* Program the new number of wait states to the LATENCY bits in the FLASH_ACR register */

__HAL_FLASH_SET_LATENCY(FLatency);

/* Check that the new number of wait states is taken into account to access the Flash

memory by reading the FLASH_ACR register */

if (__HAL_FLASH_GET_LATENCY() != FLatency)

{

return HAL_ERROR;

}

}

/*-------------------------- HCLK Configuration --------------------------*/

if (((RCC_ClkInitStruct->ClockType) & RCC_CLOCKTYPE_HCLK) == RCC_CLOCKTYPE_HCLK)

{

/* Set the highest APBx dividers in order to ensure that we do not go through

a non-spec phase whatever we decrease or increase HCLK. */

if (((RCC_ClkInitStruct->ClockType) & RCC_CLOCKTYPE_PCLK1) == RCC_CLOCKTYPE_PCLK1)

{

MODIFY_REG(RCC->CFGR, RCC_CFGR_PPRE1, RCC_HCLK_DIV16);

}

if (((RCC_ClkInitStruct->ClockType) & RCC_CLOCKTYPE_PCLK2) == RCC_CLOCKTYPE_PCLK2)

{

MODIFY_REG(RCC->CFGR, RCC_CFGR_PPRE2, (RCC_HCLK_DIV16 << 3));

}

/* Set the new HCLK clock divider */

assert_param(IS_RCC_HCLK(RCC_ClkInitStruct->AHBCLKDivider));

MODIFY_REG(RCC->CFGR, RCC_CFGR_HPRE, RCC_ClkInitStruct->AHBCLKDivider);

}

/*------------------------- SYSCLK Configuration ---------------------------*/

if (((RCC_ClkInitStruct->ClockType) & RCC_CLOCKTYPE_SYSCLK) == RCC_CLOCKTYPE_SYSCLK)

{

assert_param(IS_RCC_SYSCLKSOURCE(RCC_ClkInitStruct->SYSCLKSource));

/* HSE is selected as System Clock Source */

if (RCC_ClkInitStruct->SYSCLKSource == RCC_SYSCLKSOURCE_HSE)

{

/* Check the HSE ready flag */

if (__HAL_RCC_GET_FLAG(RCC_FLAG_HSERDY) == RESET)

{

return HAL_ERROR;

}

}

/* PLL is selected as System Clock Source */

else if (RCC_ClkInitStruct->SYSCLKSource == RCC_SYSCLKSOURCE_PLLCLK)

{

/* Check the PLL ready flag */

if (__HAL_RCC_GET_FLAG(RCC_FLAG_PLLRDY) == RESET)

{

return HAL_ERROR;

}

}

/* HSI is selected as System Clock Source */

else

{

/* Check the HSI ready flag */

if (__HAL_RCC_GET_FLAG(RCC_FLAG_HSIRDY) == RESET)

{

return HAL_ERROR;

}

}

__HAL_RCC_SYSCLK_CONFIG(RCC_ClkInitStruct->SYSCLKSource);

/* Get Start Tick*/

tickstart = HAL_GetTick();

while (__HAL_RCC_GET_SYSCLK_SOURCE() != (RCC_ClkInitStruct->SYSCLKSource << RCC_CFGR_SWS_Pos))

{

if ((HAL_GetTick() - tickstart) > CLOCKSWITCH_TIMEOUT_VALUE)

{

return HAL_TIMEOUT;

}

}

}

/* Decreasing the number of wait states because of lower CPU frequency */

if (FLatency < __HAL_FLASH_GET_LATENCY())

{

/* Program the new number of wait states to the LATENCY bits in the FLASH_ACR register */

__HAL_FLASH_SET_LATENCY(FLatency);

/* Check that the new number of wait states is taken into account to access the Flash

memory by reading the FLASH_ACR register */

if (__HAL_FLASH_GET_LATENCY() != FLatency)

{

return HAL_ERROR;

}

}

/*-------------------------- PCLK1 Configuration ---------------------------*/

if (((RCC_ClkInitStruct->ClockType) & RCC_CLOCKTYPE_PCLK1) == RCC_CLOCKTYPE_PCLK1)

{

assert_param(IS_RCC_PCLK(RCC_ClkInitStruct->APB1CLKDivider));

MODIFY_REG(RCC->CFGR, RCC_CFGR_PPRE1, RCC_ClkInitStruct->APB1CLKDivider);

}

/*-------------------------- PCLK2 Configuration ---------------------------*/

if (((RCC_ClkInitStruct->ClockType) & RCC_CLOCKTYPE_PCLK2) == RCC_CLOCKTYPE_PCLK2)

{

assert_param(IS_RCC_PCLK(RCC_ClkInitStruct->APB2CLKDivider));

MODIFY_REG(RCC->CFGR, RCC_CFGR_PPRE2, ((RCC_ClkInitStruct->APB2CLKDivider) << 3));

}

/* Update the SystemCoreClock global variable */

SystemCoreClock = HAL_RCC_GetSysClockFreq() >> AHBPrescTable[(RCC->CFGR & RCC_CFGR_HPRE) >> RCC_CFGR_HPRE_Pos];

/* Configure the source of time base considering new system clocks settings*/

HAL_InitTick(uwTickPrio);

return HAL_OK;

}

HAL_RCC_ClockConfig(RCC_ClkInitTypeDef *RCC_ClkInitStruct, uint32_t FLatency) --> SystemCoreClock --> HAL_InitTick(uwTickPrio)

SystemCoreClock :HCLK

__weak HAL_StatusTypeDef HAL_InitTick(uint32_t TickPriority)

{

/* Configure the SysTick to have interrupt in 1ms time basis*/

if (HAL_SYSTICK_Config(SystemCoreClock / (1000U / uwTickFreq)) > 0U)

{

return HAL_ERROR;

}

/* Configure the SysTick IRQ priority */

if (TickPriority < (1UL << __NVIC_PRIO_BITS))

{

HAL_NVIC_SetPriority(SysTick_IRQn, TickPriority, 0U);

uwTickPrio = TickPriority;

}

else

{

return HAL_ERROR;

}

/* Return function status */

return HAL_OK;

}

HAL_StatusTypeDef HAL_InitTick(uint32_t TickPriority) -->HAL_SYSTICK_Config(SystemCoreClock / (1000U / uwTickFreq))

HAL_TickFreqTypeDef uwTickFreq = HAL_TICK_FREQ_DEFAULT; /* 1KHz */

typedef enum

{

HAL_TICK_FREQ_10HZ = 100U,

HAL_TICK_FREQ_100HZ = 10U,

HAL_TICK_FREQ_1KHZ = 1U,

HAL_TICK_FREQ_DEFAULT = HAL_TICK_FREQ_1KHZ

} HAL_TickFreqTypeDef;

/**

* @brief Initializes the System Timer and its interrupt, and starts the System Tick Timer.

* Counter is in free running mode to generate periodic interrupts.

* @param TicksNumb Specifies the ticks Number of ticks between two interrupts.

* @retval status: - 0 Function succeeded.

* - 1 Function failed.

*/

uint32_t HAL_SYSTICK_Config(uint32_t TicksNumb)

{

return SysTick_Config(TicksNumb);

}

/**

\brief System Tick Configuration

\details Initializes the System Timer and its interrupt, and starts the System Tick Timer.

Counter is in free running mode to generate periodic interrupts.

\param [in] ticks Number of ticks between two interrupts.

\return 0 Function succeeded.

\return 1 Function failed.

\note When the variable <b>__Vendor_SysTickConfig</b> is set to 1, then the

function <b>SysTick_Config</b> is not included. In this case, the file <b><i>device</i>.h</b>

must contain a vendor-specific implementation of this function.

*/

__STATIC_INLINE uint32_t SysTick_Config(uint32_t ticks)

{

if ((ticks - 1UL) > SysTick_LOAD_RELOAD_Msk)

{

return (1UL); /* Reload value impossible */

}

SysTick->LOAD = (uint32_t)(ticks - 1UL); /* set reload register */

NVIC_SetPriority (SysTick_IRQn, (1UL << __NVIC_PRIO_BITS) - 1UL); /* set Priority for Systick Interrupt */

SysTick->VAL = 0UL; /* Load the SysTick Counter Value */

SysTick->CTRL = SysTick_CTRL_CLKSOURCE_Msk |

SysTick_CTRL_TICKINT_Msk |

SysTick_CTRL_ENABLE_Msk; /* Enable SysTick IRQ and SysTick Timer */

return (0UL); /* Function successful */

}

总结:时钟初始化后将SystemCoreClock 设置为当前的HCLK工作频率,将SysTick->LOAD设置为SystemCoreClock / (1000U / uwTickFreq),当SysTick->LOAD倒数为0时产生一个systick中断,uwTickFreq=1时1ms中断一次,uwTickFreq=10时10ms中断一次,uwTickFreq=100时100ms中断一次。

2594

2594

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?