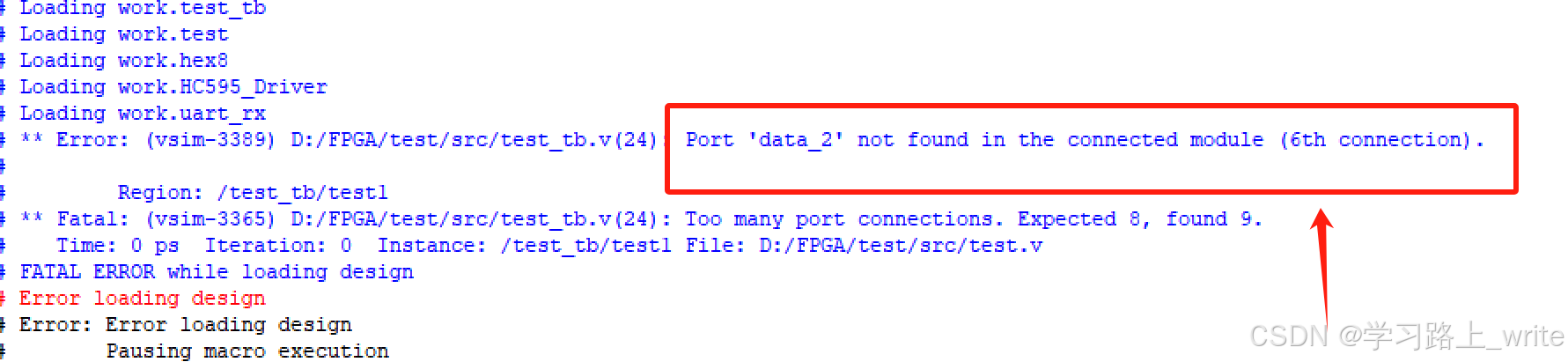

Port 'data 2' not found in the connected module (6th connection).

这个错误,我这里是因为 data 2 这个变量的原因。在模块中定义的端口,和文件中例化端口对不上,检查一下就好。

(下面是我的错误过程~)

Modelsim里面报错:

最开始很纳闷,分析综合一直成功,(亲爱的Successful)

进入Modelsim这个软件,就报错了 ,显示是在 test_b 文件里面

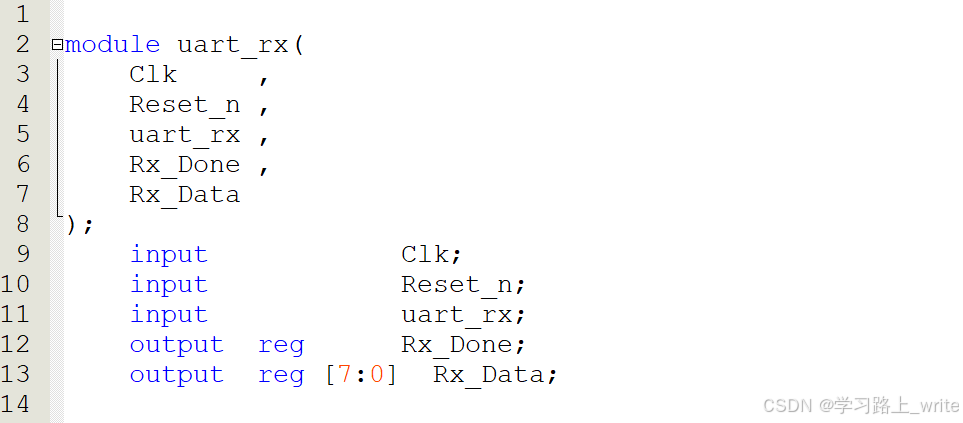

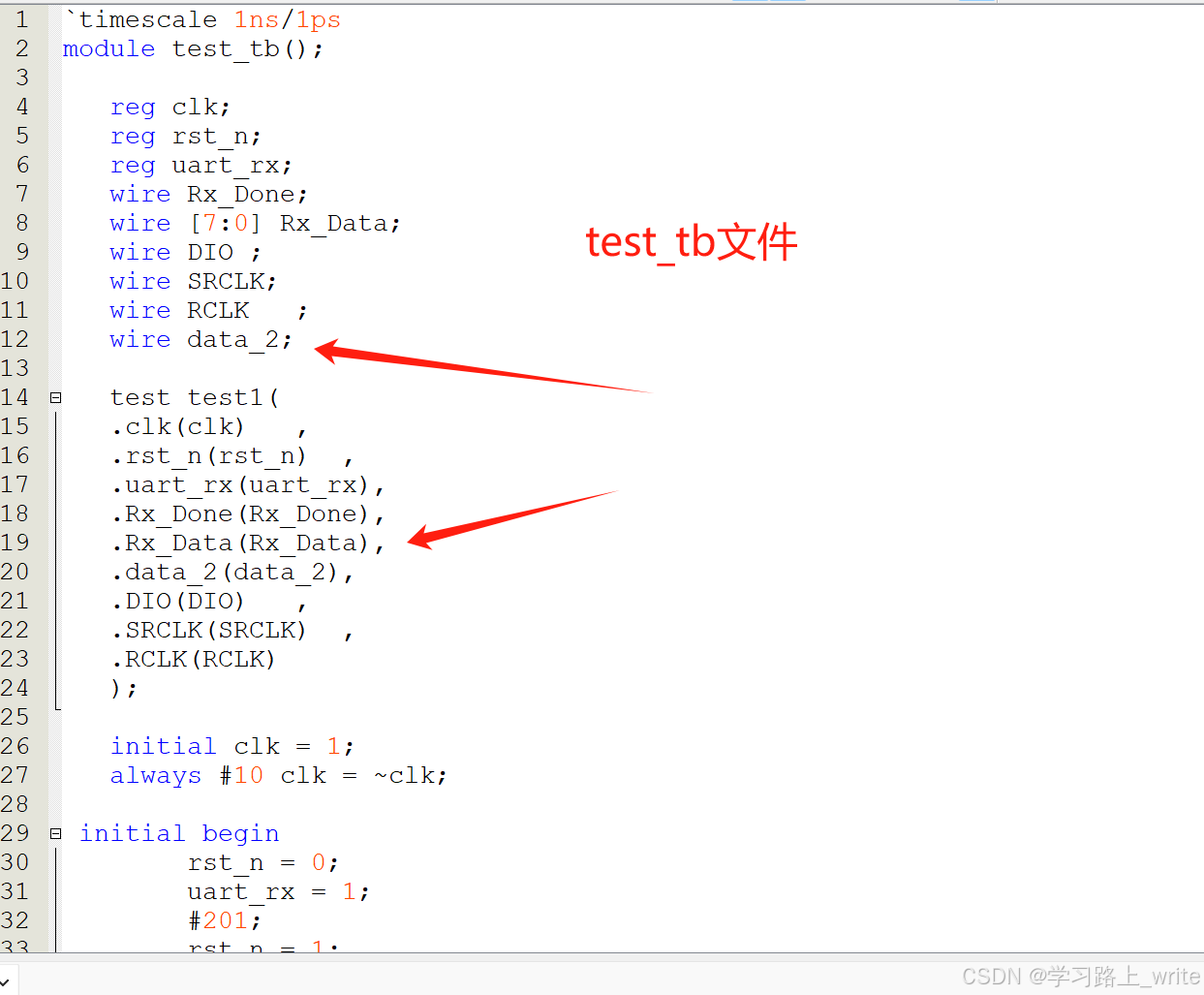

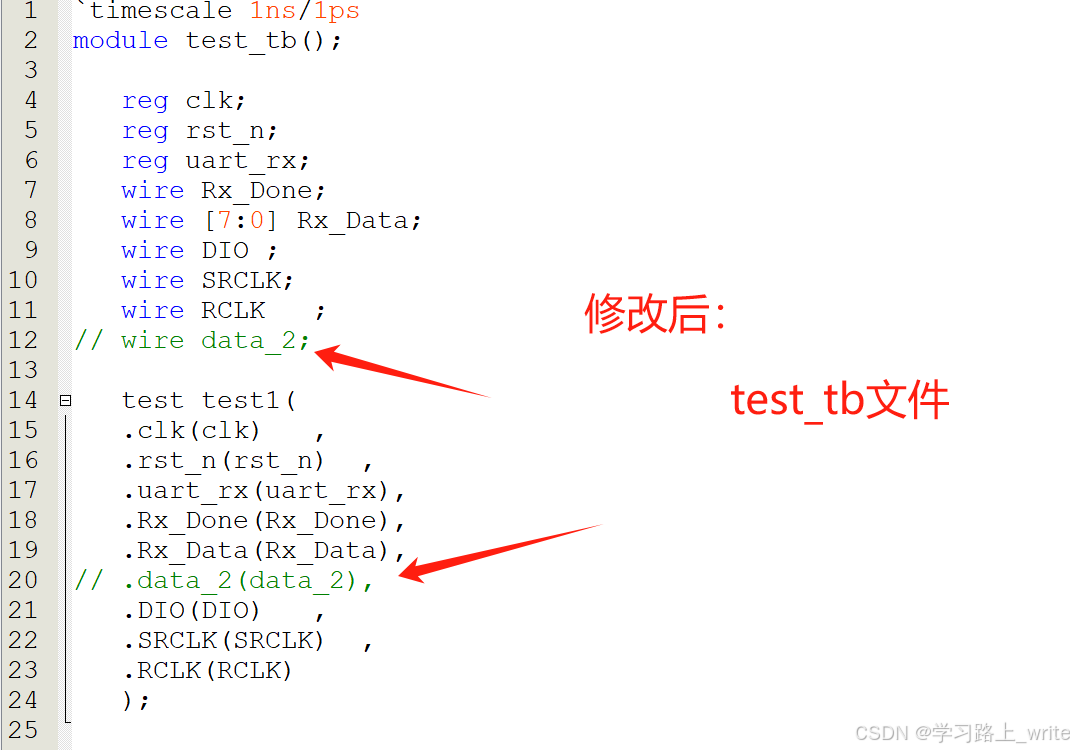

最后找出来是这个,这是我的串口模块 ,最开始写过一个data_2 变量,后面不用,就删掉了,但是测试文件(test_tb)里面并没有删除这个端口,就导致了Modelsim里面报错,(端口接不上端口了,)

左边这个是模块 ,右边这个是测试文件,可以看到data_2端口还在,删掉就好

然后就OK了

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?