前面的文章,我们分享了在考虑不同PVT条件时芯片电源完整性的特征表现,以及常用的一些优化方向(芯片电源完整性在不同芯片Corner下的特征,不同芯片Corner下的功耗特征表现)。不仅是电源跟PVT相关性大,高速信号也会跟不同PVT相关,那在不同的PVT下,信号完整性的特性又将如何变化呢?接下来我们就来分析一下。

首先还是先对PVT进行介绍一下,在芯片设计中,corner通常指的是工艺角,也就是制造过程中工艺参数的变化,比如温度、电压和工艺偏差的组合。不同的corner会影响晶体管的性能,进而影响整个芯片的性能,尤其是高速IO的信号完整性。

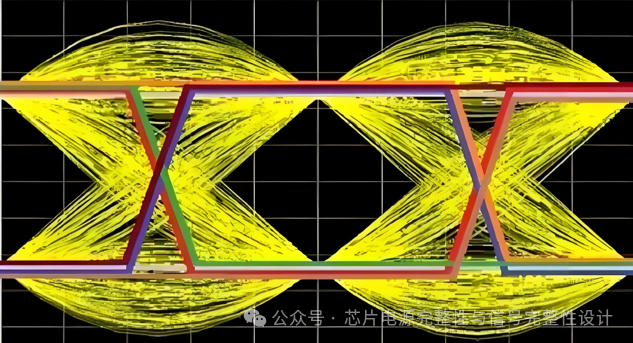

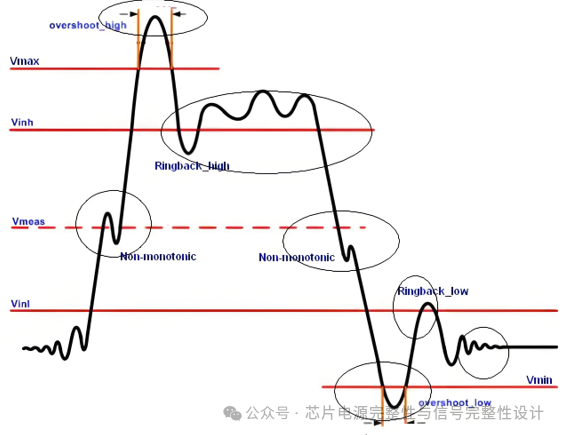

高速IO的信号完整性主要涉及几个方面:时序、电压水平、噪声、阻抗匹配、功耗等。那么在不同的corner下,比如FF(Fast-Fast)、SS(Slow-Slow)、TT(Typical-Typical)、FS(Fast-Slow)、SF(Slow-Fast)等,这些信号的参数会如何变化?

先来说“P”,晶体管的速度在不同的corner下会变化,FF corner下,晶体管速度最快,驱动能力强,可能导致信号上升/下降时间变短,这可能引起过冲或下冲,增加信号反射的风险。而SS corner下,晶体管速度慢,驱动能力弱,可能导致信号边沿变缓,增加时序问题,比如建立时间和保持时间不够,影响数据正确捕获。

再来说“V”,不同corner通常伴随不同的电压条件,比如,在低压情况下(可能

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1051

1051

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?