前言:在研究liberate的过程中,本来是想基于大的模拟wrapper生成ADC和DAC的timing信息,来替换AD/DA vendor提供的timing,就先仔细看了看已有的timing arc是怎么个逻辑。还是很有收获的,记录下来。

-

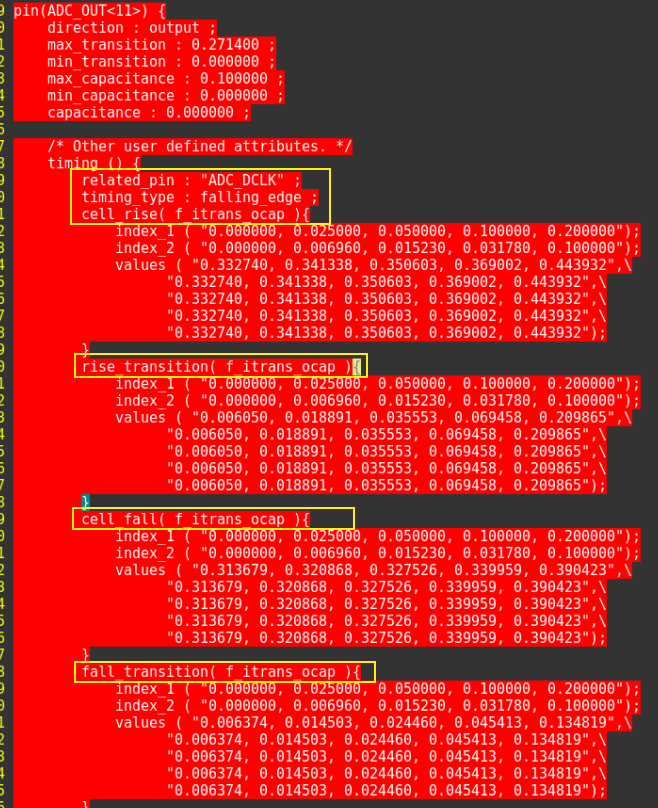

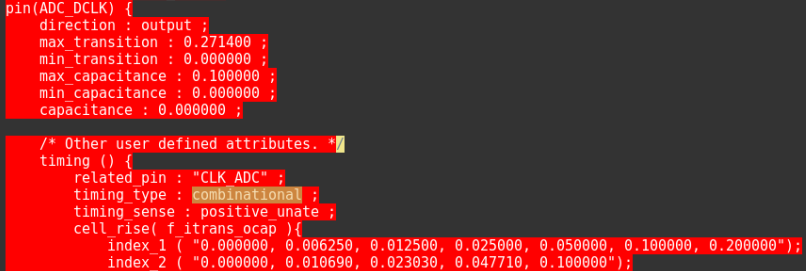

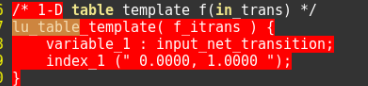

先以ADC为例,timing arc主要在output pin,lib定义如下:

分析:

- timing_type:falling_edge/rising_dege

这是一个定义了基于下降沿或上升沿delay和transition的timing arc。

- cell_rise(f_itrans_ocap)/cell_fall(f_itrans_ocap)

- rise_transition(f_itrans_ocap)/fall_transition(f_itrans_ocap)

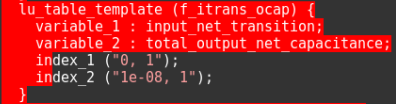

f_itrans_ocap是template名,定义了output pin的自变量input transition和output cap。基于该二维自变量,lib列出了ADC_OUT rise/fall情况下的两个因变量delay和transition。

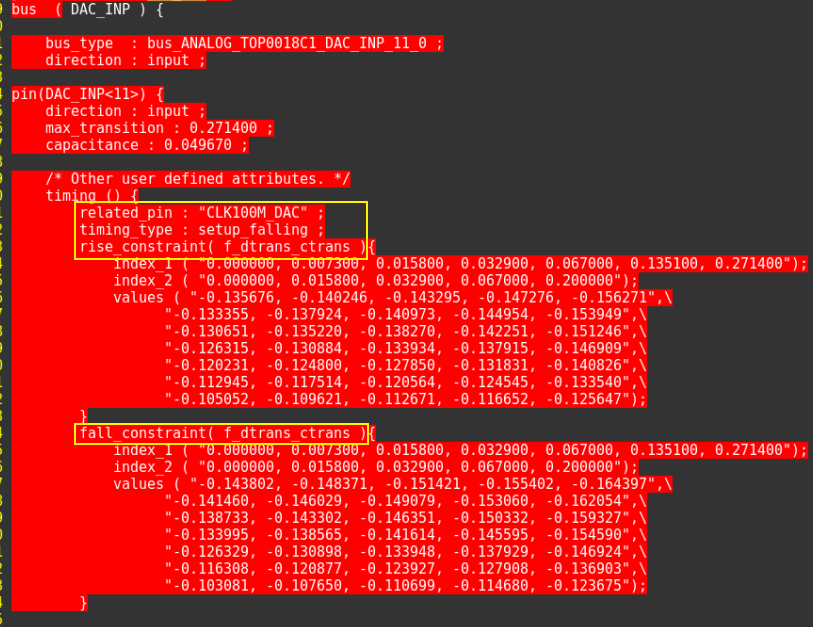

对于DAC,timing arc在input pin,lib内部需要check:

分析:

- timing_type:setup_falling

从timing_type来看就知道这是一个用于检查input setup的arc,属于constraint arc。

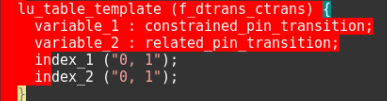

- rise_constraint(f_dtrans_ctrans)/fall_constraint(f_dtrans_ctrans)

f_dtrans_ctrans是template名,定义了input data和related clk的transition。基于该二维自变量,lib列出了DAC_INP rise/fall情况下的一个因变量setup/hold constraint。

除了以上sequential timing arc以外,还有其他timing_type,总结如下:

output timing arc(delay&transition)

1、combinational timing arc

表示相对于related_pin到ADC_DCLK output pin的net delay 和 transition(在下面,没贴出来了,类似上面ADC_OUT)。分positive_unate和negative_unate,表示二者信号变化方向一致或相反。

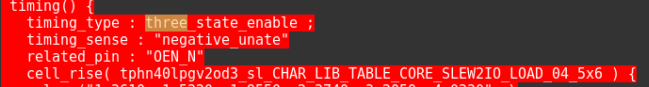

2、three_state_enable timing arc

主要用于三态IO,输出使能OEN到PAD的arc。同样包含delay和transition。

input timing arc(constraint)

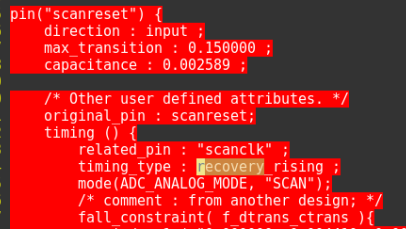

1、recovery/removal timing arc

表示从clk到reset之间的setup/hold timing constraint

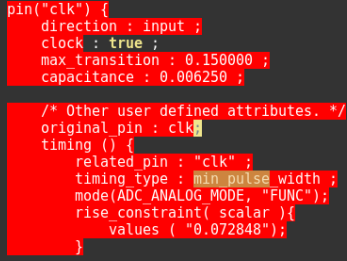

2、min_pulse_width timing arc

表示clk最小脉宽的constraint。自变量只有一个,input transition

1703

1703

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?