本文章大多以提问的形式给出问题,并尝试解答,主要目的是为了帮助自己复习sv基础知识,不足之处还请指正,以便共同学习!

二、过程块与子程序

1、task中continue和break的区别?

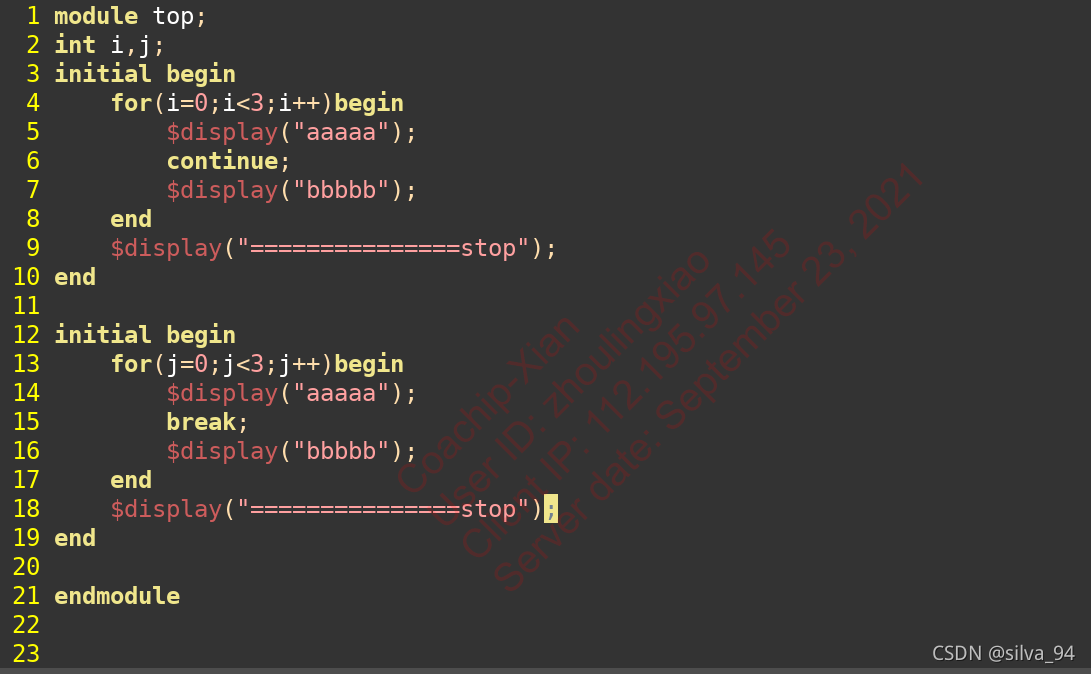

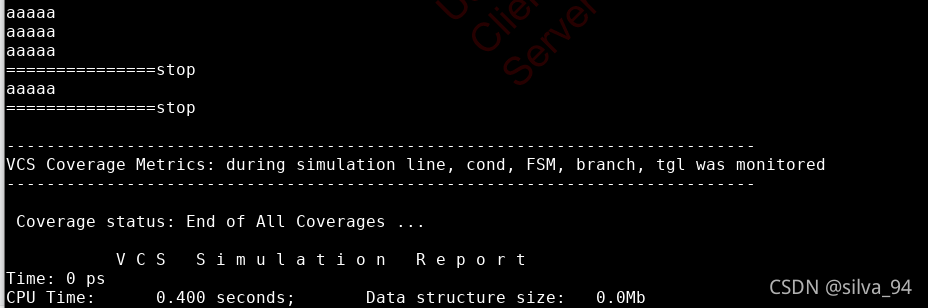

如如下代码及仿真结果所示:

continue: 表示终止本轮循环,进入下一轮循环

break: 跳出整个循环

2、task与function的区别?

function: 不可内置耗时语句

task: 可内置耗时语句(如wait(), @(posedge clk)等)

一般情况下,任务可以调用函数,但是函数不能调用任务。

3、always与initial的区别?

always:在整个仿真阶段一直存在并执行,通常搭配@(*)或者@(posedge clk)

本文总结了System Verilog中过程块与子程序的关键概念,包括task与function的区别,always与initial的使用场景,参数传递方式,以及静态存储与自动存储的区别。详细解释了continue和break在task中的作用,以及ref传递与值传递的影响。同时阐述了变量的生命周期,特别是static和automatic变量在不同情况下的行为。

本文总结了System Verilog中过程块与子程序的关键概念,包括task与function的区别,always与initial的使用场景,参数传递方式,以及静态存储与自动存储的区别。详细解释了continue和break在task中的作用,以及ref传递与值传递的影响。同时阐述了变量的生命周期,特别是static和automatic变量在不同情况下的行为。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2216

2216

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?