提示:本文基于 MIPI Alliance Specification for Display Command Set (DCS) Version 1.2 – 16 June 2014

文章目录

DCS 简介

MIPI DCS(Mobile Industry Processor Interface Display Command Set)是一种专为显示设备设计的命令集,它是 MIPI 协议族的一部分,主要用于控制显示设备的配置和数据传输。DCS 提供了一系列标准化的命令,使得主机(Host)能够通过这些命令与显示模块(Display Module)进行通信,配置显示参数,发送像素数据,以及读取显示模块的状态和数据。

MIPI DCS 定义了多种命令,用于不同的显示模块架构和功耗模式。这些命令集分为用户命令集(User Command Set)和制造商命令集(Manufacturer Command Set)。发送用户命令集需要使用 DCS 方式,而发送制造商命令集需要使用 GEN 方式,即 Data Type 上有所区别。其中用户命令集的命令码范围为 0x00 至 0xAF,而制造商命令集的命令码则用于出厂时的默认设置,一旦设备出厂,这些命令将不可见,被视为无操作(NOP)。

显示模块架构

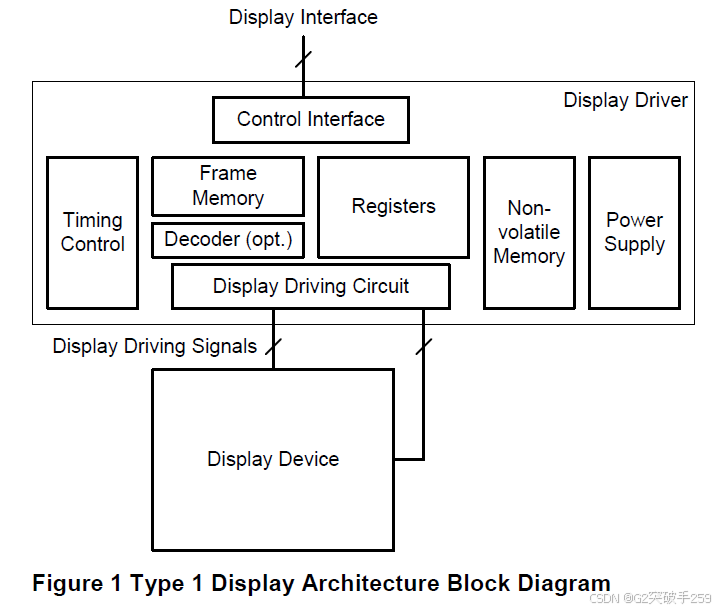

显示模块应基于类型 1、类型 2 或类型 3 的显示架构。

类型 1

第一类显示架构应由以下功能模块组成:

显示设备(Display Device)。显示设备用于显示图像数据。

显示驱动程序(Display Driver)。显示驱动程序可以是用于驱动显示设备的一个或多个设备。

帧存储器(Frame memory)。帧存储器保存压缩或未压缩的图像数据,这取决于显示是否需要压缩。帧存储器可以集成在显示驱动程序中。

寄存器(Registers)。寄存器用于配置显示行为和标识信息。寄存器可以集成在显示驱动程序中。

时序控制器(Timing Controller)。时序控制器根据配置信息提供时序信号来控制显示和显示驱动程序。时序控制器可以集成在显示驱动程序中。

非易失性内存(Non-volatile Memory)。非易失性内存用于存储默认寄存器和配置值。非易失性存储器可以集成在显示驱动程序中。

控制接口(Control Interface)。控制接口是主处理器和显示驱动程序之间的接口。控制接口可以集成在显示驱动程序中。

显示驱动电路(Display Driving Circuit)。所述显示驱动电路将时序信号和电压转换为适于驱动所述显示设备的信号。

解码器(Decoder)(可选)。解码器对来自主机处理器的压缩数据进行解码,并生成像素数据以传递给显示设备。解码器是可选的,因为压缩取决于系统要求。解码器可以集成在显示驱动程序中。

电源(Power Supply)。电源将系统电压转换为显示设备和显示驱动程序可用的电平。电源可以集成在显示驱动程序中。

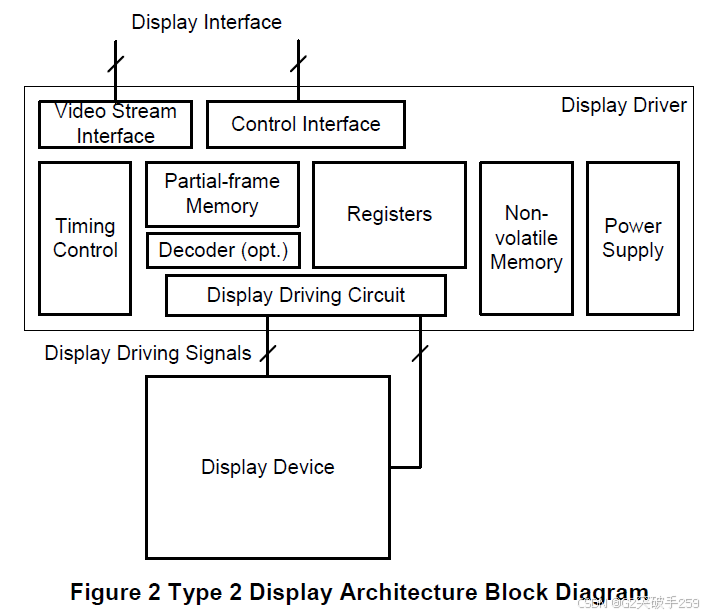

类型 2

第二类显示架构应由以下功能模块组成:

显示设备(Display Device)。显示设备用于显示图像数据。

显示驱动程序(Display Driver)。显示驱动程序可以是用于驱动显示设备的一个或多个设备。

部分帧存储器(Partial-frame Memory)。部分帧存储器根据显示是否需要压缩来保存压缩或未压缩的图像数据。部分帧存储器可以集成在显示驱动程序中。

寄存器(Registers)。寄存器用于配置显示行为和标识信息。寄存器可以集成在显示驱动程序中。

时序控制器(Timing Controller)。时序控制器根据配置信息提供时序信号来控制显示和显示驱动程序。时序控制器可以集成在显示驱动程序中。

非易失性内存(Non-volatile Memory)。非易失性内存用于存储默认寄存器和配置值。非易失性存储器可以集成在显示驱动程序中。

控制接口(Control Interface)。控制接口是主处理器和显示驱动程序之间的接口。控制接口可以集成在显示驱动程序中。

显示驱动电路(Display Driving Circuit)。所述显示驱动电路将时序信号和电压转换为适于驱动所述显示设备的信号。

解码器(Decoder)(可选)。解码器对来自主机处理器的压缩数据进行解码,并生成像素数据以传递给显示设备。解码器是可选的,因为压缩取决于系统要求。解码器可以集成在显示驱动程序中。

电源(Power Supply)。电源将系统电压转换为显示设备和显示驱动程序可用的电平。电源可以集成在显示驱动程序中。

视频流接口(Video Stream Interface)。视频流接口接收来自主机处理器的视频图像数据和时序信号。

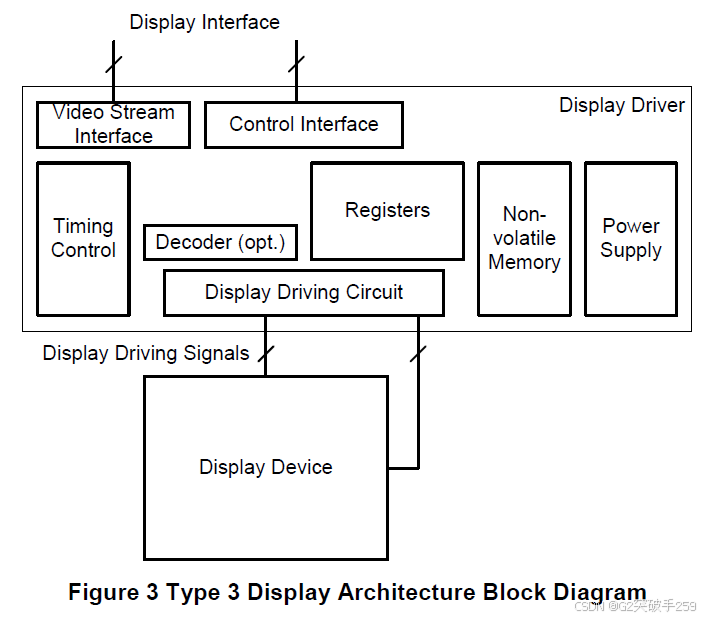

类型 3

第三类显示架构应由以下功能模块组成:

显示设备(Display Device)。显示设备用于显示图像数据。

显示驱动程序(Display Driver)。显示驱动程序可以是用于驱动显示设备的一个或多个设备。

寄存器(Registers)。寄存器用于配置显示行为和标识信息。寄存器可以集成在显示驱动程序中。

时序控制器(Timing Controller)。时序控制器根据配置信息提供时序信号来控制显示和显示驱动程序。时序控制器可以集成在显示驱动程序中。

非易失性内存(Non-volatile Memory)。非易失性内存用于存储默认寄存器和配置值。非易失性存储器可以集成在显示驱动程序中。

控制接口(Control Interface)。控制接口是主处理器和显示驱动程序之间的接口。控制接口可以集成在显示驱动程序中。

显示驱动电路(Display Driving Circuit)。所述显示驱动电路将时序信号和电压转换为适于驱动所述显示设备的信号。

解码器(Decoder)(可选)。解码器对来自主机处理器的压缩数据进行解码,并生成像素数据以传递给显示设备。解码器是可选的,因为压缩取决于系统要求。解码器可以集成在显示驱动程序中。

电源(Power Supply)。电源将系统电压转换为显示设备和显示驱动程序可用的电平。电源可以集成在显示驱动程序中。

视频流接口(Video Stream Interface)。视频流接口接收来自主机处理器的视频图像数据和时序信号。

在所有架构类型中,都假定电源在显示驱动程序的控制之下。

显示命令集是通过上述控制接口使用的。

三种类型的显示架构的区别是,类型 1 仅支持 Command Mode,类型 2 既可以支持 Command Mode,也可以支持 Video Mode,类型 3 仅支持 Video Mode。

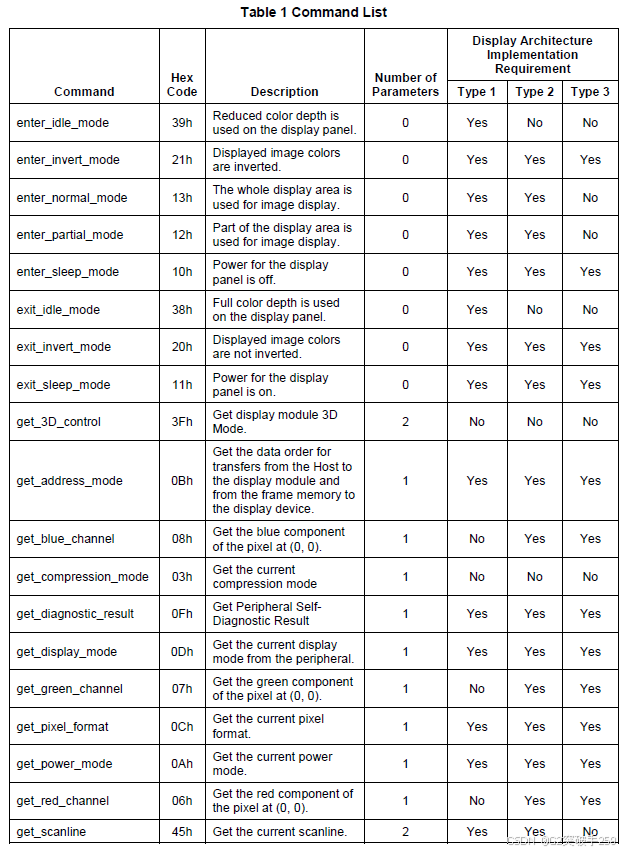

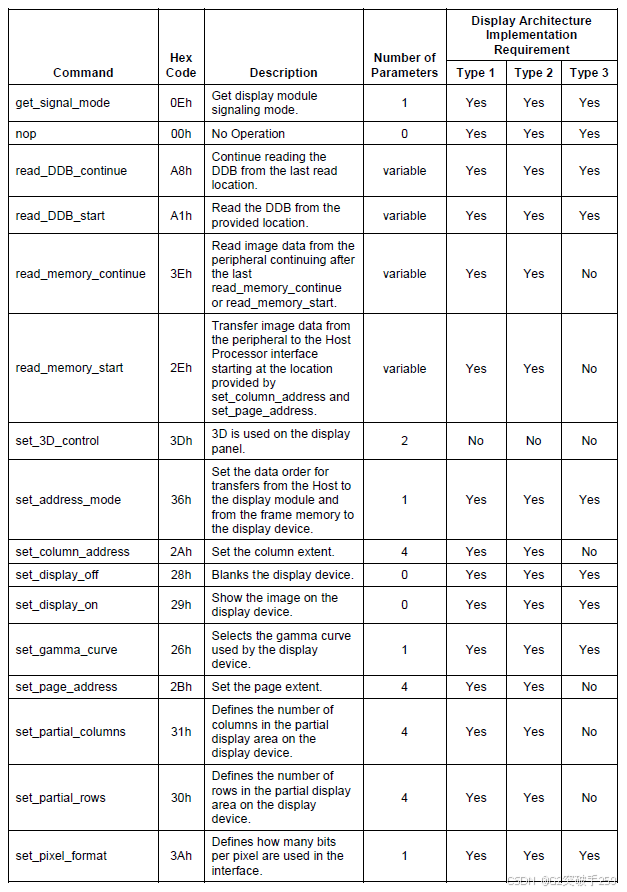

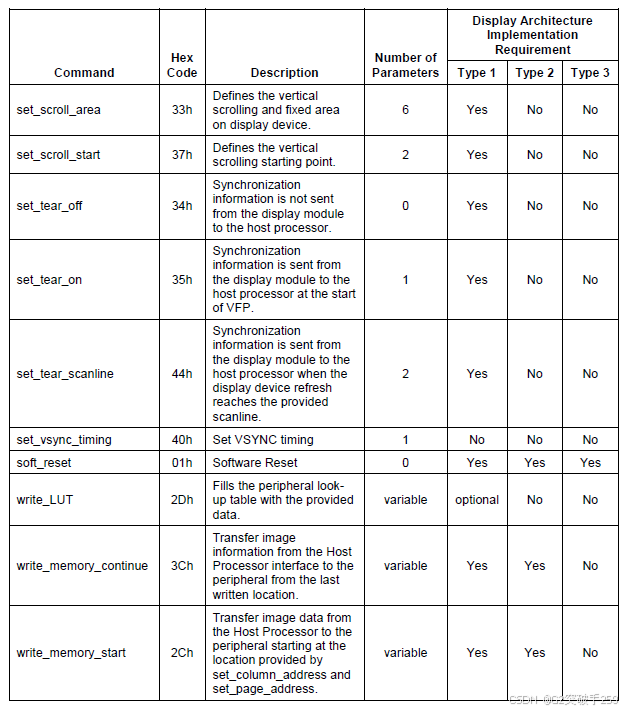

DCS 命令列表

图像数据压缩

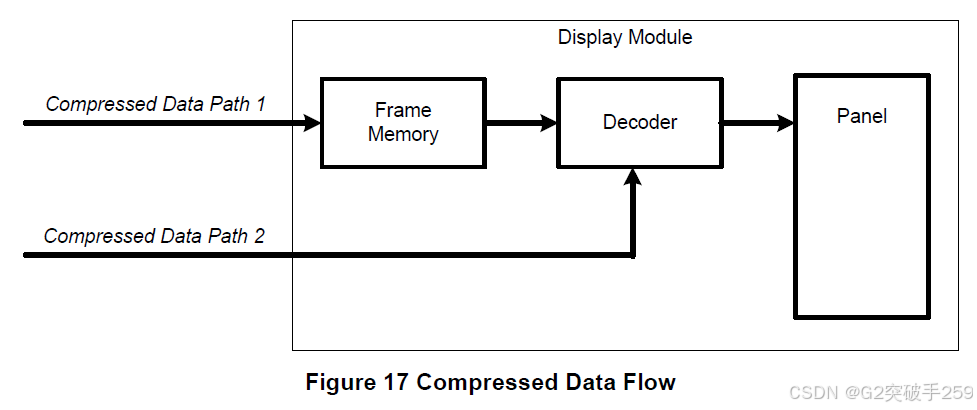

如果解码器在显示器上实现,则具有帧存储器的 Command Mode 显示器可以任选地支持显示流压缩。当使用压缩模式命令短数据包启用压缩方案时,显示器将把所有传入的像素数据视为压缩的比特流。

图 1 显示了当压缩模式被设置为 “启用” 时可能的数据流路径。如果特定的显示驱动程序使用数据路径 1 或数据路径 2,这是一个实现选择。如果没有帧内存存在,数据路径 2 是唯一的选择。

在图 17 中,设计为使用架构类型 1 或类型 2 的显示器,实现了解码器,可以使用路径 1 接收压缩图像数据并将其存储到帧存储器中。然后,解码器可以从帧存储器中解压缩图像数据以更新面板。如果还支持视频流,具有帧存储器的显示器可能能够支持路径 1 和路径 2 之间的切换。

在图 17 中,设计为使用架构类型 3 的显示器,实现了解码器,可以使用路径 2 接收压缩图像数据。模式之间的切换不应导致面板上的任何异常行为或视觉缺陷。

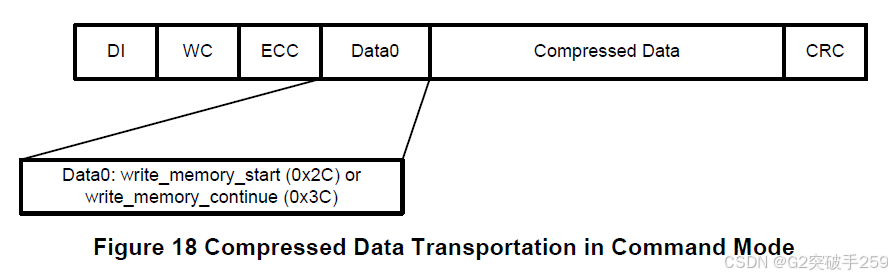

在 Command Mode 下显示流压缩传输

当在命令模式下将压缩模式状态设置为 “启用” 时,压缩方案将被激活,压缩后的像素数据将以长数据包格式传输到显示器。在这种情况下,载荷的第一个字节应该是 write_memory_start 或 write_memory_continue 命令,并且显示将把后面的所有图像数据视为压缩数据。在长数据包类型的任何其他命令之后的数据字节将不被视为压缩数据。

图 18 显示了使用 Command Mode 的架构类型 1 或类型 2 显示在协议级别上的压缩数据传输。

在图 18 中,长包数据类型 0x39 用于通过 DSI 系统传送压缩图像数据。

常用命令描述

介绍实现 MIPI 联盟显示接口规范的显示模块支持的命令。本节仅介绍部分常用命令。

所有命令都由单个 8 位字节组成,在某些情况下,还伴随着为正确执行命令提供必要信息的参数。通常,命令和伴随的参数字节使用显示接口的串行或并行位 0 到 7 进行传输,而不考虑物理接口的宽度和架构。唯一的例外是 DBI 系统中的 read_memory_continue、read_memory_start、write_memory_continue 和 write_memory_start 命令。这些命令可以使用显示接口的全宽度。

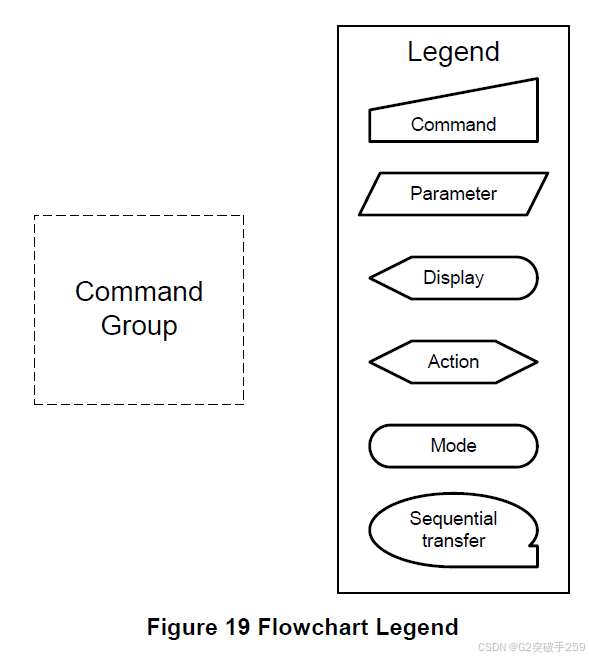

本节中的命令流程图使用图 19 中定义的符号。

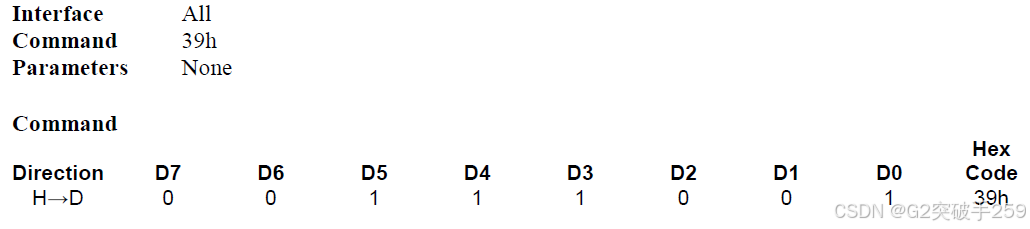

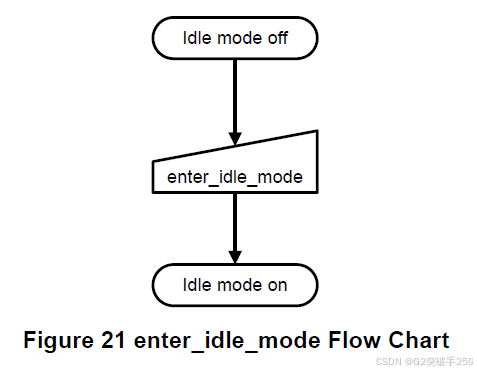

enter_idle_mode

描述

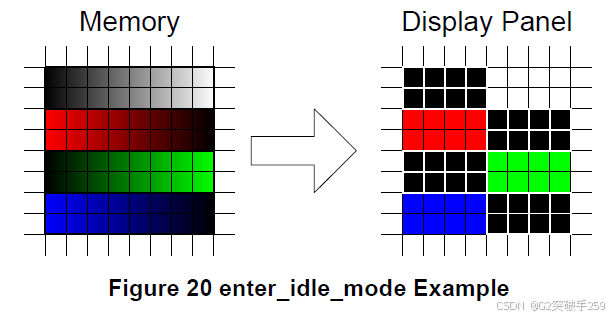

该命令使显示模块进入 IDLE 模式。

在 IDLE 模式下,颜色表达减少。使用帧存储器中每个 R, G 和 B 颜色组件的 MSB 在显示设备上显示颜色。

流程图

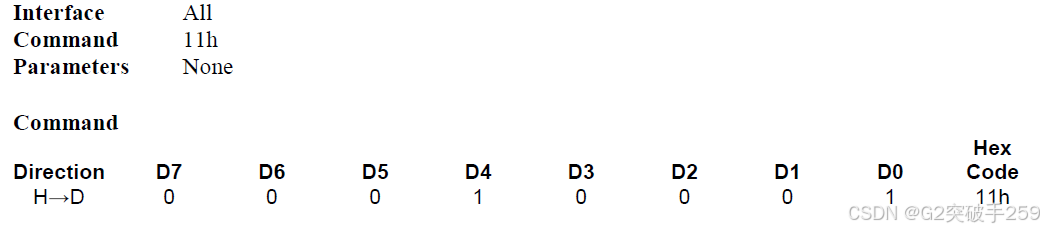

enter_normal_mode

描述

该命令使显示模块进入 Normal 模式。

Normal 模式定义为部分显示模式和滚动模式关闭。

当显示模块处于部分显示模式时,主机处理器在发送此命令前两帧将 PCLK、HS 和 VS 信息发送给 Type 2 显示模块。

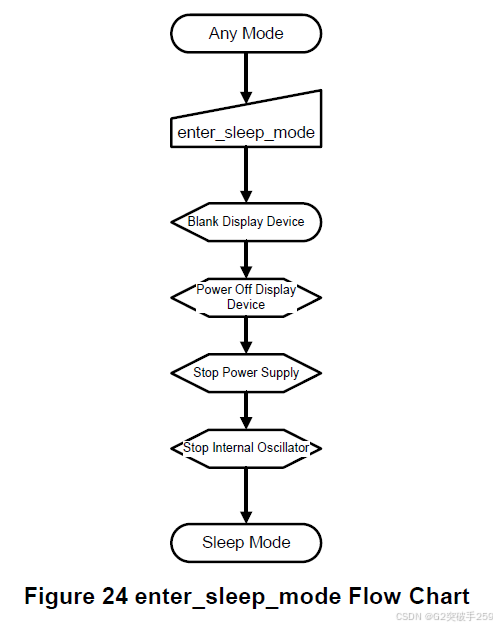

enter_sleep_mode

描述

该命令将使显示模块进入休眠模式。

在该模式下,显示模块内部除接口通信外,所有不必要的模块都将被关闭。这是显示模块支持的最低功耗模式。

DBI 或 DSI Command Mode 保持运行,帧存储器保持其内容。当显示模块处于 Normal 模式时,发送此命令后,主机处理器继续向 Type 2 和 Type 3 显示模块发送 PCLK、HS 和 VS 信息两帧。

限制

当显示模块已进入休眠模式时,此命令无效。

主处理器在向显示模块发送任何新命令之前必须等待5毫秒,以允许电源电压和时钟电路稳定下来。

流程图

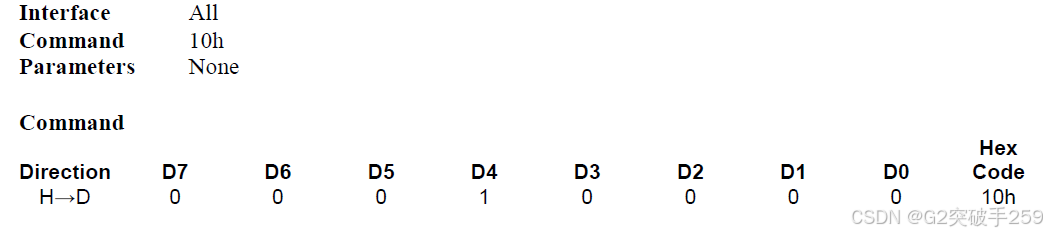

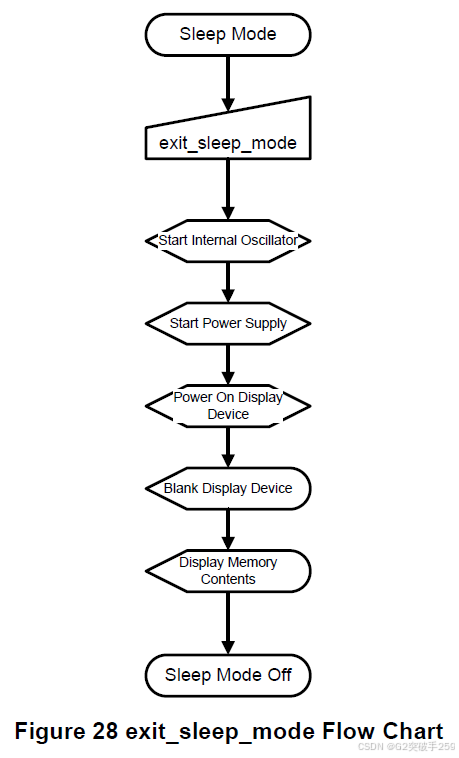

exit_sleep_mode

描述

该命令将使显示模块退出休眠模式。显示模块内的所有模块都是启用的。

当显示模块处于正常模式时,主机处理器在发送此命令前两帧将 PCLK、HS 和 VS 信息发送给 Type 2 和 Type 3 显示模块。

限制

当显示模块处于非休眠模式时,此命令不会对显示设备产生任何可见的影响。

主机处理器在发送此命令后必须等待 5 毫秒才能发送另一条命令。这种延迟允许电源电压和时钟电路稳定。

主机处理器在发送 exit_sleep_mode 命令后必须等待 120 毫秒才能发送 enter_sleep_mode 命令。

当退出休眠模式时,显示模块将显示模块的默认值加载到寄存器中。在加载寄存器时,如果出厂默认值和寄存器值相同或显示模块未处于休眠模式,则显示设备上不应有任何异常的视觉效果。

显示模块收到该命令后,将启动自诊断功能。有关自诊断功能的描述,请参见第 5.3 节。

流程图

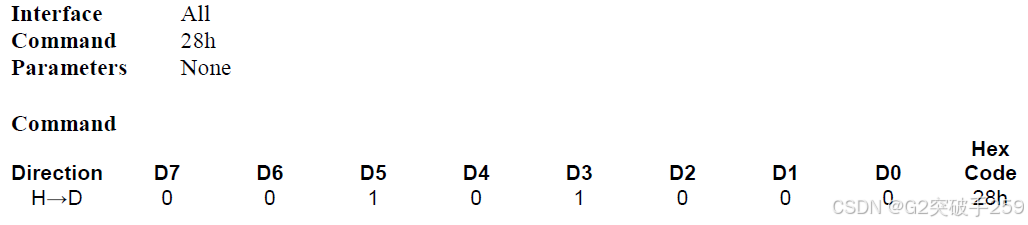

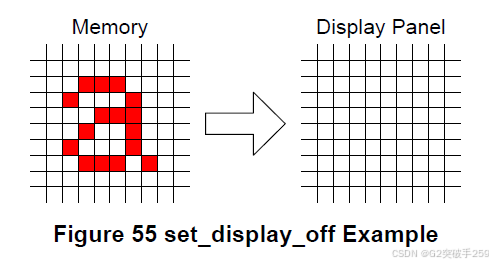

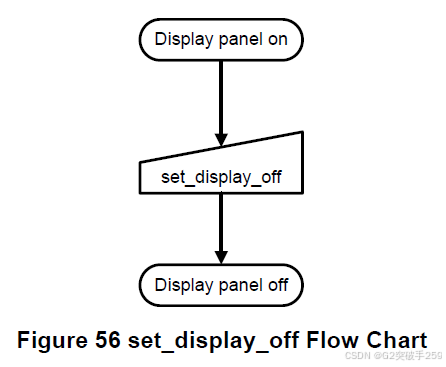

set_display_off

描述

该命令将导致显示模块停止在显示设备上显示图像数据。帧内存内容保持不变。不改变状态位。

流程图

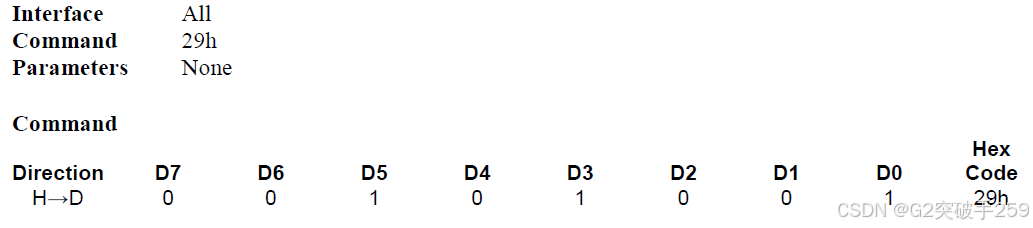

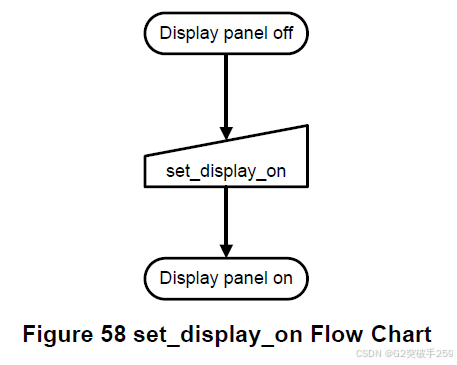

set_display_on

描述

该命令使显示模块开始在显示设备上显示图像数据。帧内存内容保持不变。不改变状态位。

流程图

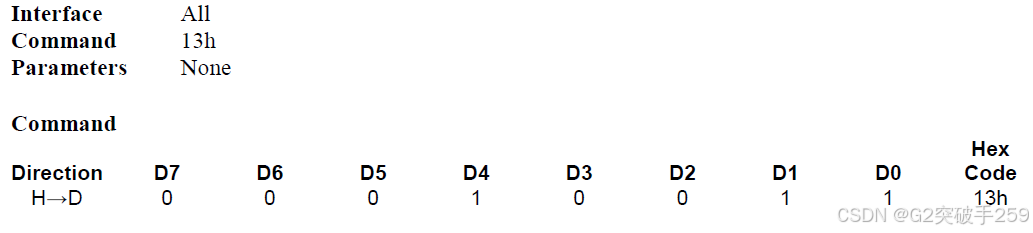

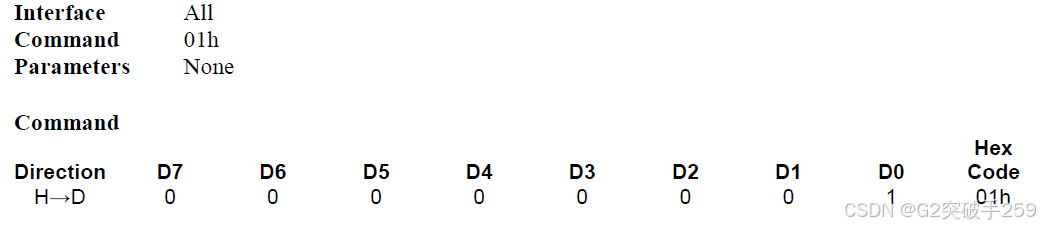

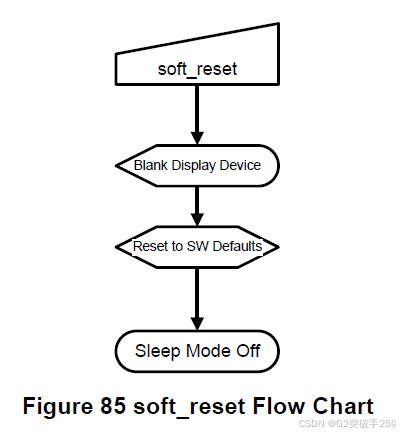

soft_reset

描述

显示模块执行软件复位。寄存器是用它们的 Sw Reset 默认值写的。有关复位值的列表,请参见第 5.7 节。

帧内存内容不受此命令影响。

限制

主机处理器必须等待 5 毫秒才能将任何新命令发送到该命令之后的显示模块。显示模块在此期间更新寄存器。

如果在显示模块处于休眠模式时发送软件复位,则主机处理器必须等待 120 毫秒才能发送 exit_sleep_mode 命令。

当显示模块不处于休眠模式时,不应该发送软件复位。

流程图

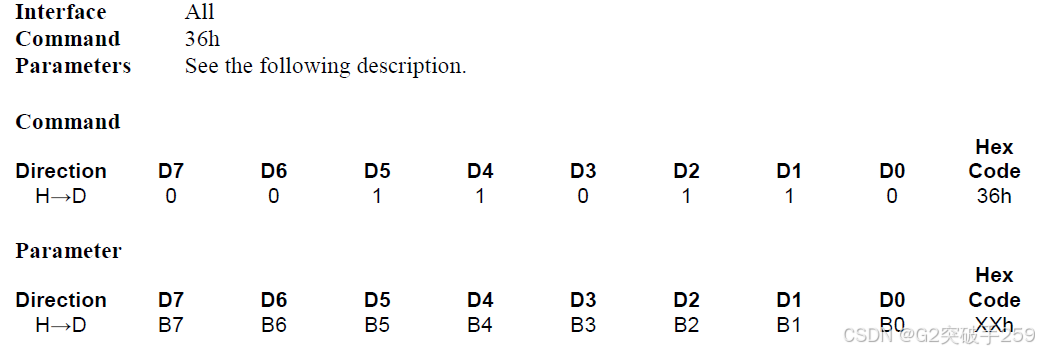

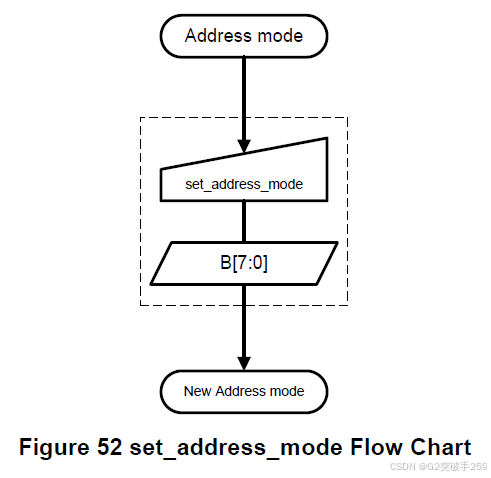

set_address_mode

描述

该命令设置从主机处理器传输到显示模块的帧内存 bits B[7:5],以及从显示模块的帧内存传输到显示设备 bits B[4:0] 的数据顺序。

在 2D 模式下,设备应按照规定使用 B7 到 B0 的参数位定义。

在 3D 模式下,设备应将不适用位设置为 “0”。哪些位与 3D 模式相关是具体实现的。设备制造商应在产品数据表中描述任何此类特定于实现的行为。

如果设备支持压缩,并且选择 [VESA01] 参考的编码系统(参见 5.8 节)作为压缩模式算法,则无法保证部分比特的功能。因此,所有不适用的位都被设置为 “0”。如果设备支持供应商特定的算法,设备制造商应定义当压缩模式状态为 “启用” 时应支持哪些位。

所有位对于在 Command Mode 下运行的基于 Type 2 显示体系结构的外设或基于 Type 1 显示体系结构的外设都有效。比特 B5、B4、B2、B1 和 B0 对运行在 Video Mode 下的 Type 2 显示架构的外设或 Type 3 显示架构的外设没有影响。

不改变状态位。

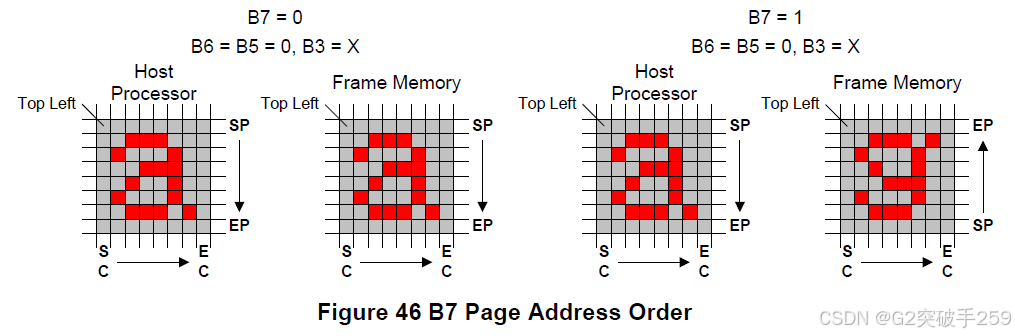

B7 - 页地址顺序

这个位控制数据页从主机处理器传输到外设帧内存的顺序,用于在 Command Mode 下运行的 Type 1 或 Type 2 显示架构。该位还控制主机处理器显示在 Video Mode 下运行的 Type 2 或 Type 3 显示架构的设备数据锁存顺序。

如果选择 VESA DSC Standard 1.0 [VESA01] 作为主动压缩算法,则该位设置为 “0”。

“0” = 从上到下,页面从 SP 转到 EP。

“1” = 从下到上,页面从 EP 转到 SP。

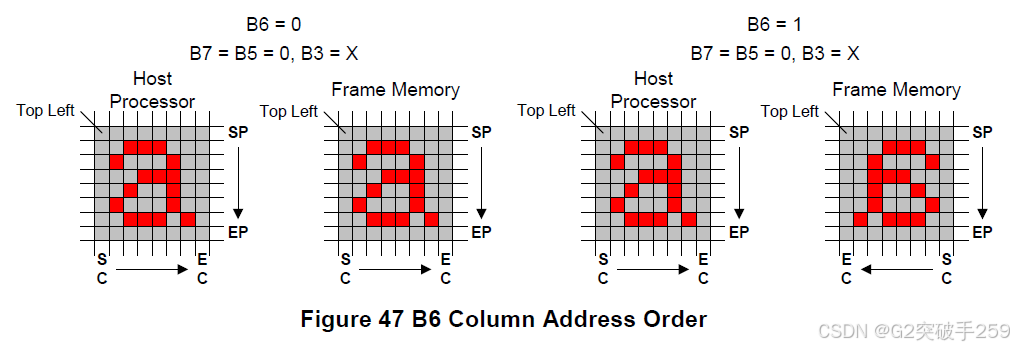

B6 - 列地址顺序

这个位控制数据列从主机处理器传输到外设的帧内存的顺序,用于在 Command Mode 下运行的 Type 1 或 Type 2 显示体系结构。该位还控制主机处理器显示在 Video Mode 下运行的 Type 2 或 Type 3 显示架构的设备数据锁存顺序。

如果选择 VESA DSC Standard 1.0 [VESA01] 作为主动压缩算法,则该位设置为 “0”。

“0” = 从左到右,列从 SC 转到 EC。

“1” = 从右到左,列从 EC 转到 SC。

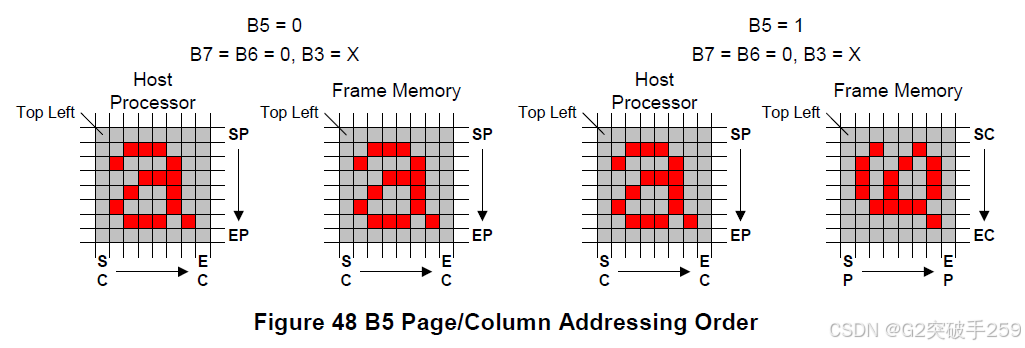

B5 - 页/列寻址顺序

这个位控制数据列从主机处理器传输到外设帧内存的顺序。

如果选择 VESA DSC Standard 1.0 [VESA01] 作为主动压缩算法,则该位设置为 “0”。

“0” = Normal Mode。

参见第 6.45 节(B5 = 0)了解正常模式操作的描述。

“1” = Reverse Mode。

参见第 6.45 节(B5 = 1)了解反向模式操作的描述。

B4 - 显示设备线刷新顺序

这个位控制显示设备的水平线刷新顺序。无论位设置如何,显示设备上显示的图像都不受影响。

“0” = 显示设备从上到下刷新。

“1” = 显示设备从下到上刷新。

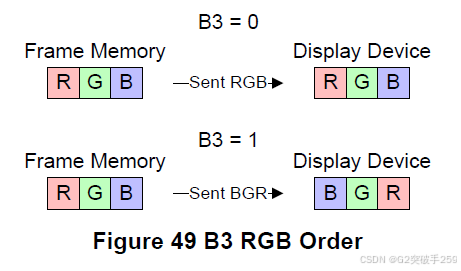

B3 - RGB/BGR 顺序

这个位控制 RGB 数据锁存顺序从外设的帧内存传输到在 Command Mode 下运行的 Type 1 或 Type 2 显示架构的显示设备。该位还控制 RGB 数据锁存顺序从主机处理器传输到在 Video Mode 下运行的 Type 2 或 Type 3 显示架构的显示设备。

“0” = 按 RGB 顺序发送像素。

“1” = 按 BGR 顺序发送像素。

B2 - 显示数据锁存数据顺序

这个位控制显示设备的垂直线数据锁存顺序。无论位设置如何,显示设备上显示的图像都不受影响。

“0” = 显示设备从左侧向右侧刷新。

“1” = 显示设备从右侧向左侧刷新。

注意:如果显示设备逐行刷新,则此位没有视觉效果。

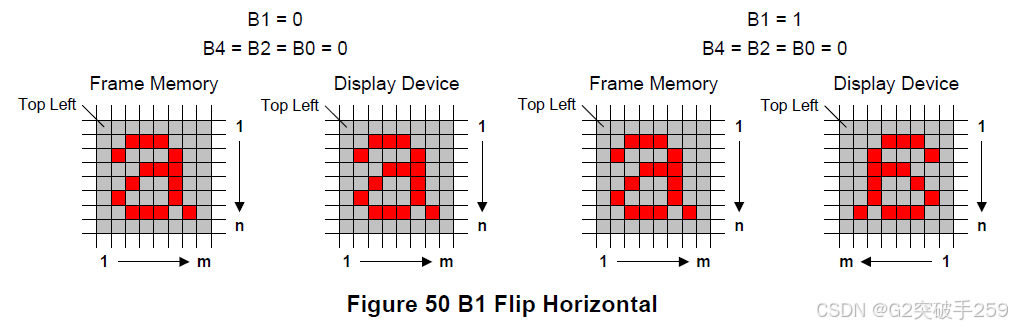

B1 - 水平翻转

这个比特将显示设备上显示的图像从左向右翻转。不改变帧内存。

“0” = 正常。

“1” = 翻转。

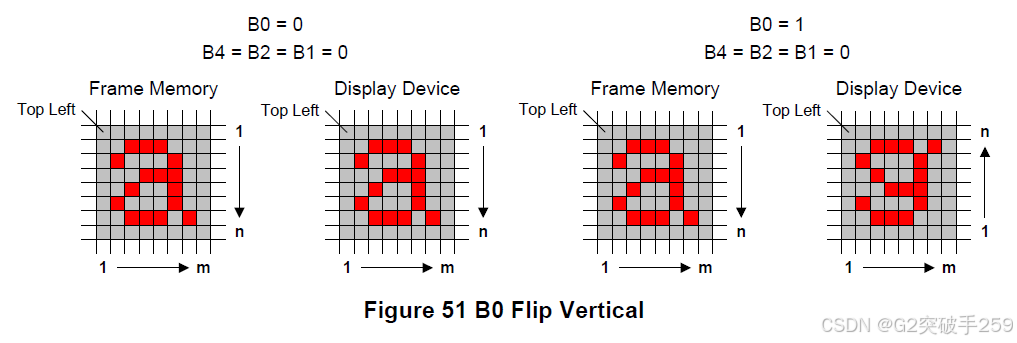

B0 - 垂直翻转

该位通过改变栅极扫描顺序将显示设备上显示的图像从上到下翻转。既不改变从帧内存读取的帧内存内容,也不改变从帧内存读取的顺序数据。

“0” = 正常。

“1” = 翻转。

流程图

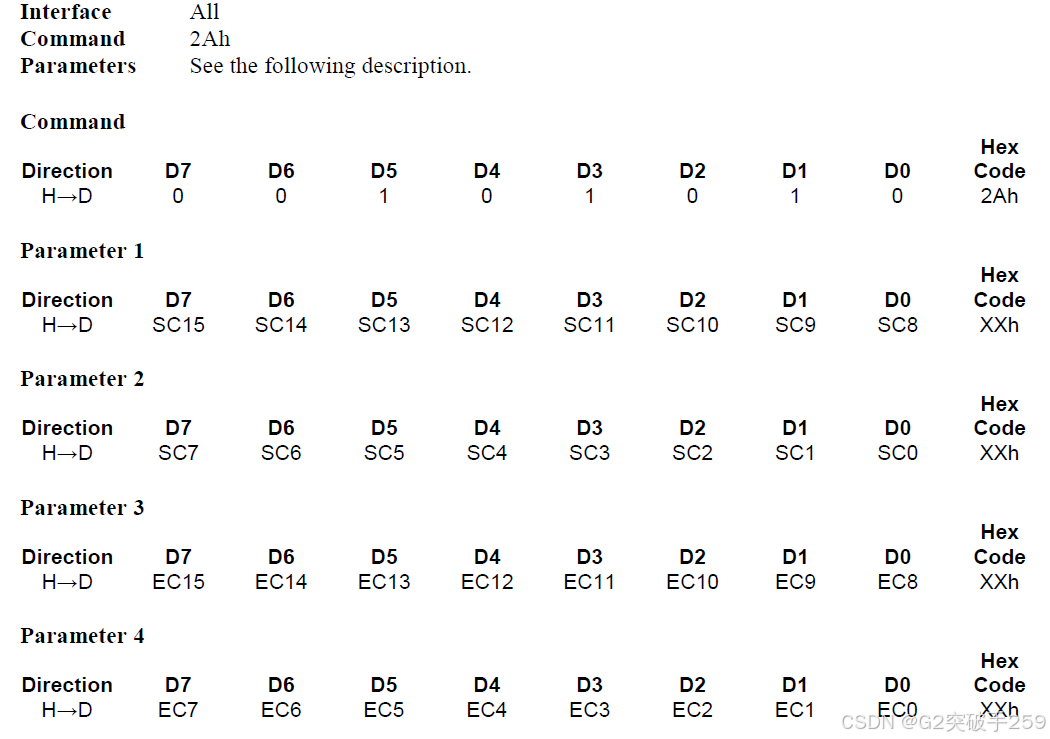

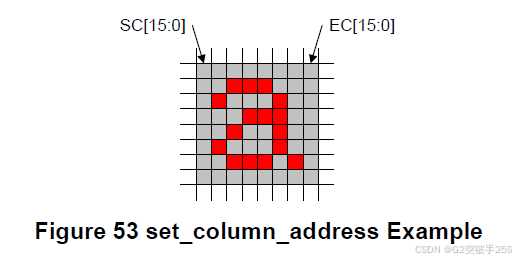

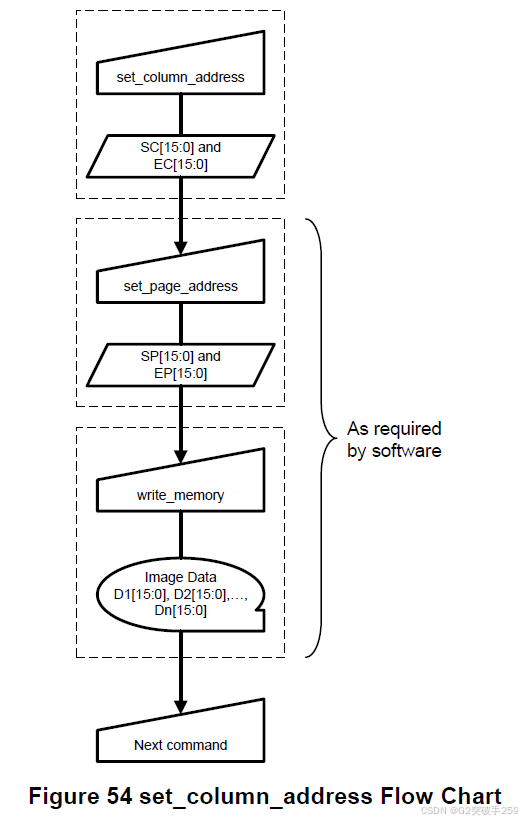

set_column_address

描述

该命令定义主机处理器使用 read_memory_continue 和 write_memory_continue 命令访问的帧内存的列范围。不改变状态位。显示模块不应该在 3D 模式下实现 set_column_address。如果显示模块在 3D 模式下执行此命令,则制造商应在产品数据表中指定操作。

限制

SC[15:0] 必须总是等于或小于 EC[15:0]。

如果 SC[15:0] 或 EC[15:0] 大于可用的帧内存,则不更新参数。

流程图

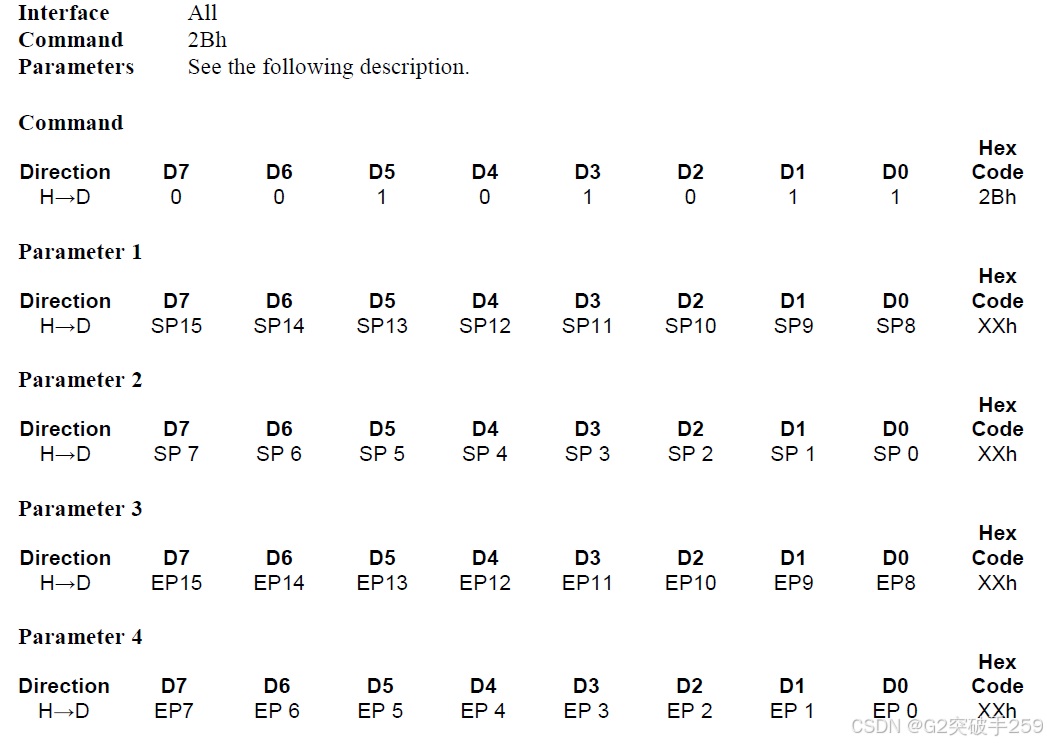

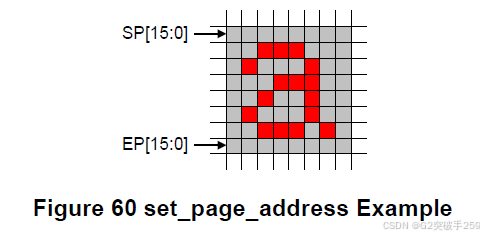

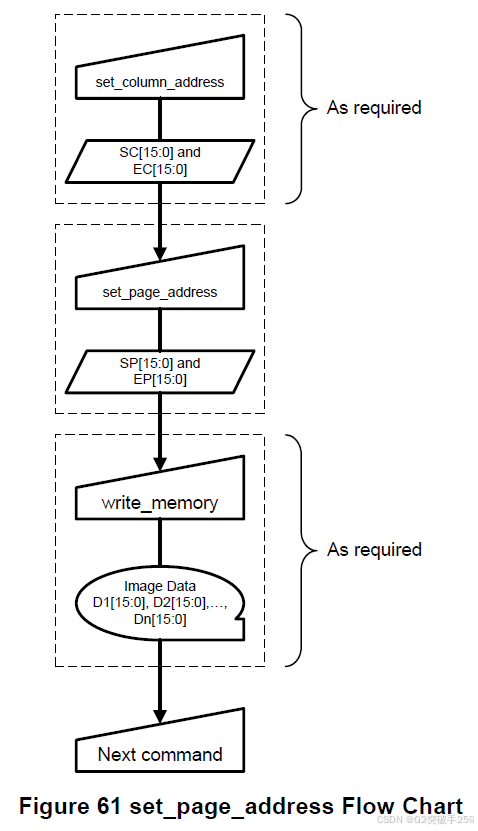

set_page_address

描述

该命令定义主机处理器使用 write_memory_continue 和 read_memory_continue 命令访问的帧内存的页范围。不改变状态位。显示模块不应该在 3D 模式下实现设置页面地址。如果显示模块在 3D 模式下执行此命令,则制造商应在产品数据表中指定操作。

限制

SP[15:0] 必须始终等于或小于 EP[15:0]。

如果 SP[15:0] 或 EP[15:0] 大于可用的帧内存,则不更新该参数。

流程图

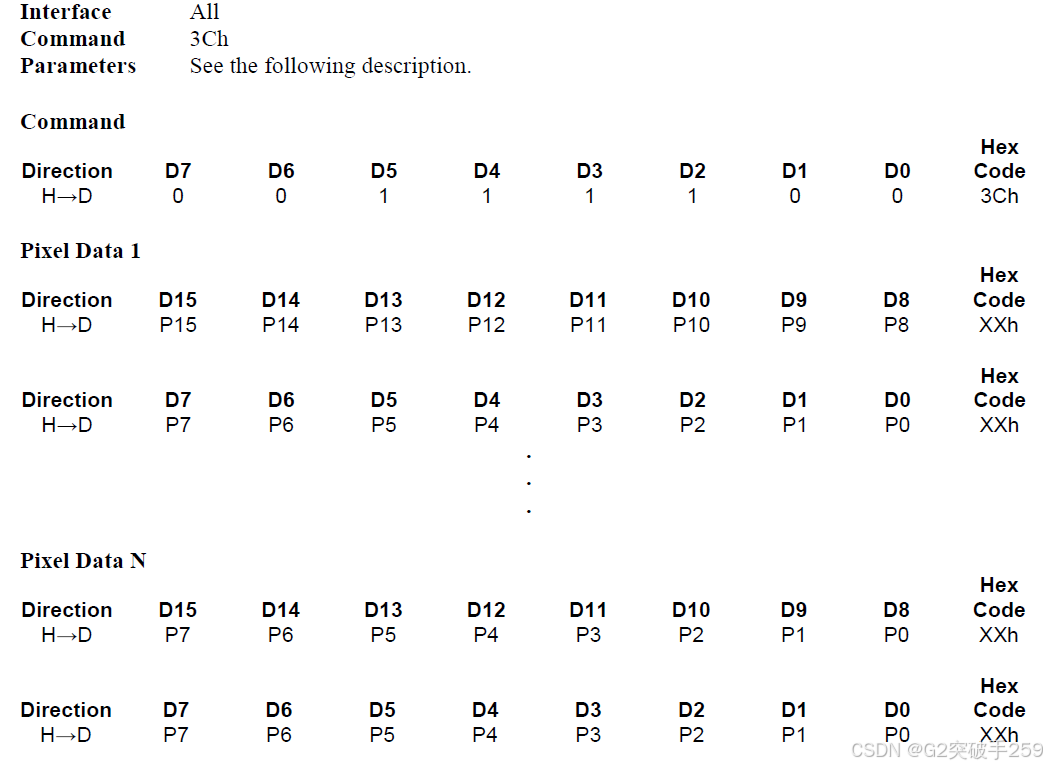

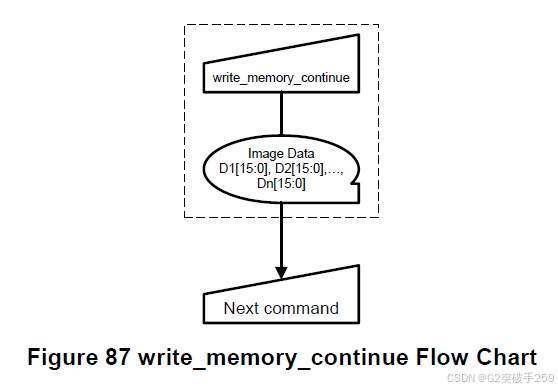

write_memory_continue

描述

该命令将图像数据从主机处理器传输到显示模块的帧内存,该帧内存从前面的 write_memory_continue 或 write_memory_start 命令之后的像素位置继续传输。

如果 set_address_mode B5 = 0:

数据从前一个 write_memory_start 或 write_memory_continue 写入范围之后的像素位置继续写入。然后增加列寄存器,并将像素写入帧内存,直到列寄存器等于结束列(EC)值。然后将列寄存器重置为 SC,并增加页寄存器。像素被写入帧内存,直到页寄存器等于结束页(EP)值,列寄存器等于 EC 值,或者主机处理器发送另一个命令。如果像素数超过 (EC - SC + 1) * (EP - SP + 1),则忽略额外的像素。

如果 set_address_mode B5 = 1:

数据从前一个 write_memory_start 或 write_memory_continue 写入范围之后的像素位置继续写入。然后增加页寄存器,并将像素写入帧内存,直到页寄存器等于结束页(EP)值。然后将页寄存器重置为 SP,并增加列寄存器。像素被写入帧内存,直到列寄存器等于结束列(EC)值,页寄存器等于 EP 值,或者主机处理器发送另一个命令。如果像素数超过 (EC - SC + 1) * (EP - SP + 1),则忽略额外的像素。

在 DSI 系统中,如果压缩模式位 CMODE = 1,显示器应将所有接收到的像素数据视为压缩图像数据。

关于开始列和结束列值的描述请参见 6.28 节。

关于开始页和结束页值的描述请参见 6.32 节。

限制

write memory_start 应该遵循 set_column_address、set_page_address 或 set_address_mode 来定义写地址。否则,使用 write_memory_continue 写入的数据将被写入未定义的地址。

流程图

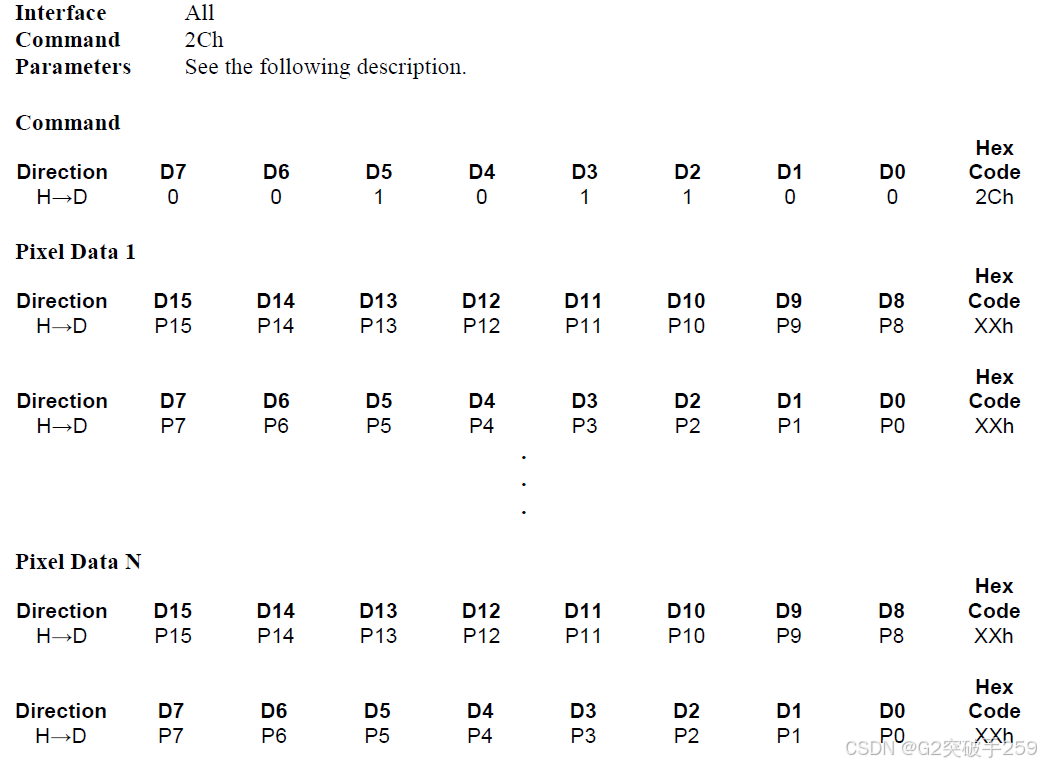

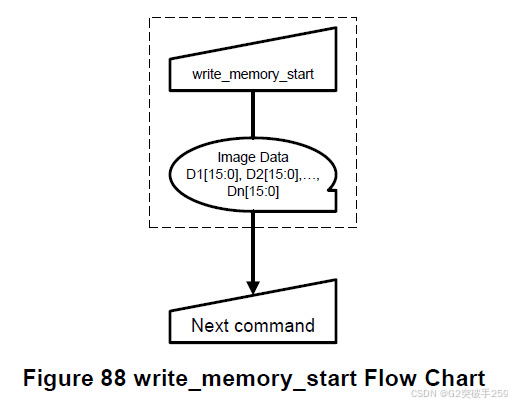

write_memory_start

描述

这个命令将图像数据从主机处理器传输到显示模块的帧内存,从前面 set_column_address 和 set_page_address 命令指定的像素位置开始(参见第 6.28 节和第 6.32 节)。

如果 set_address_mode B5 = 0:

列寄存器和页寄存器分别重置为 SC(Start column)和 SP(Start page)。

像素数据 1 存储在帧内存(SC,SP)。然后增加列寄存器,并将像素写入帧内存,直到列寄存器等于结束列(EC)值。然后将列寄存器重置为 SC,并增加页寄存器。像素被写入帧内存,直到页寄存器等于结束页(EP)值,列寄存器等于 EC 值,或者主机处理器发送另一个命令。如果像素数超过 (EC - SC + 1) * (EP - SP + 1),则忽略额外的像素。

如果 set_address_mode B5 = 1:

列寄存器和页寄存器分别重置为 SC(Start column)和 SP(Start page)。

像素数据 1 存储在帧内存(SC,SP)。然后增加页寄存器,并将像素写入帧内存,直到页寄存器等于结束页(EP)值。然后将页寄存器重置为 SP,并增加列寄存器。像素被写入帧内存,直到列寄存器等于结束列(EC)值,页寄存器等于 EP 值,或者主机处理器发送另一个命令。如果像素数超过 (EC - SC + 1) * (EP - SP + 1),则忽略额外的像素。

在 DSI 系统中,如果压缩模式位 CMODE = 1,显示器应将所有接收到的像素数据视为压缩图像数据。

关于开始列和结束列值的描述请参见 6.28 节。

关于开始页和结束页值的描述请参见 6.32 节。

限制

write_memory_start 应该跟随 set_column_address、set_page_address 或 set_address_mode 来定义写位置。否则,使用 write_memory start 和任何后续 write_memory_continue 命令写入的数据将被写入未定义的位置。

流程图

5121

5121

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?