文章目录

- 简介

- Avalon Clock and Reset Interfaces

- Avalon Memory-Mapped Interfaces

- Avalon Interrupt Interface

- Avalon Streaming Interface

- Avalon Conduit Interface

- Avalon Tri-State Conduit Interface

- 参考文献

简介

Avalon 接口允许您轻松连接英特尔 FPGA 中的组件,从而简化系统设计。Avalon 接口家族定义了适合流高速数据、读写寄存器和存储器以及控制片外设备的接口。Platform Designer 中可用的组件包含这些标准接口。此外,您可以在自定义组件中合并 Avalon 接口,从而增强设计的互连操作性。

Avalon 接口规范定义了以下七个接口:

- Avalon Streaming Interface (Avalon-ST):一种支持单向数据流的接口,包括多路复用数据流、数据包和 DSP 数据。

- Avalon Memory Mapped Interface (Avalon-MM):一种基于地址的读/写接口,典型的 Host-Agent 连接。

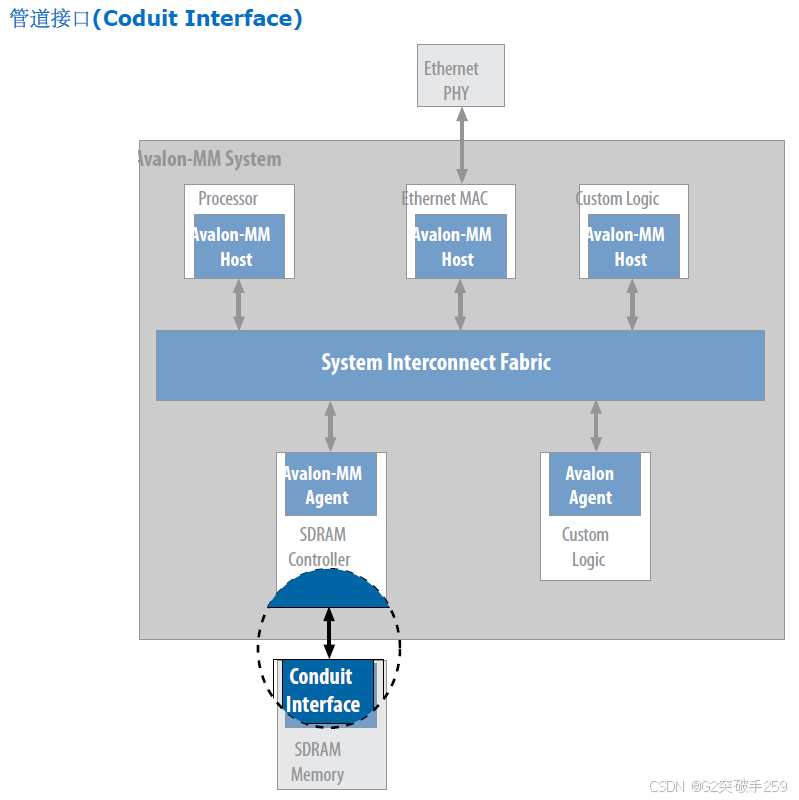

- Avalon Conduit Interface:适用于不适配任何其他 Avalon 类型的单个信号或信号组的接口类型。您可以在 Platform Designer 系统内部连接管道接口(conduit interface)。或者,可以将它们导出以连接到设计中的其他模块或者连接到 FPGA 管脚。

- Avalon Tri-State Conduit Interface (Avalon-TC):一种支持连接片外外设的接口。多个外设可以通过信号复用共享引脚,减少 FPGA 的引脚数和 PCB 上的走线数。

- Avalon Interrupt Interface:一种允许组件向其他组件发送事件信号的接口。

- Avalon Clock Interface:一种驱动或接收时钟的接口。

- Avalon Reset Interface:一种提供复位连接的接口。

一个组件可以包括任意数量的这些接口,并且还可以包括相同接口类型的多个实例。

Avalon Clock and Reset Interfaces

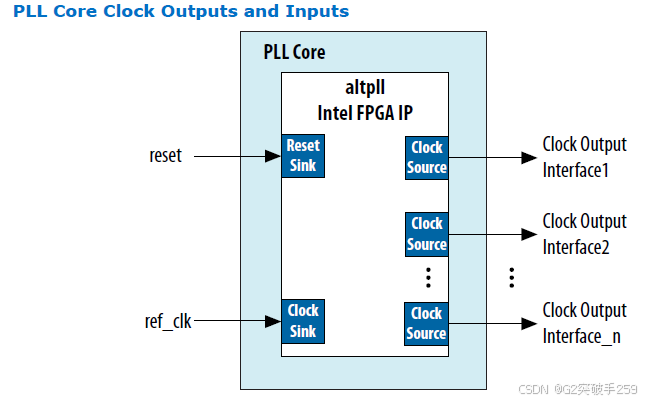

Avalon Clock 接口定义组件使用的一个或多个时钟。组件可以有时钟输入,时钟输出,或者两者都有。例如锁相环(PLL)就是同时具有时钟输入和时钟输出的组件。

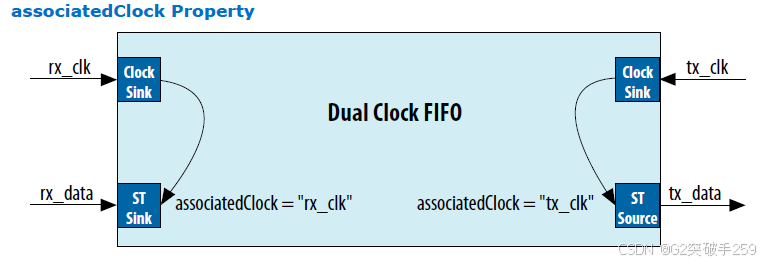

所有同步接口都有一个关联时钟(associatedClock)属性,该属性指定组件上的哪个时钟源用作接口的同步时钟。该属性如下图所示。

Clock Sink 属性

clockRate:合法值:0–232–1。表示 clock sink 接口的频率(Hz)。如果为 0,那么时钟速率支持任何频

率。如果为非 0,那么当连接的 clock source 不是指定的频率时 Platform Designer 会发出一个警告消息。

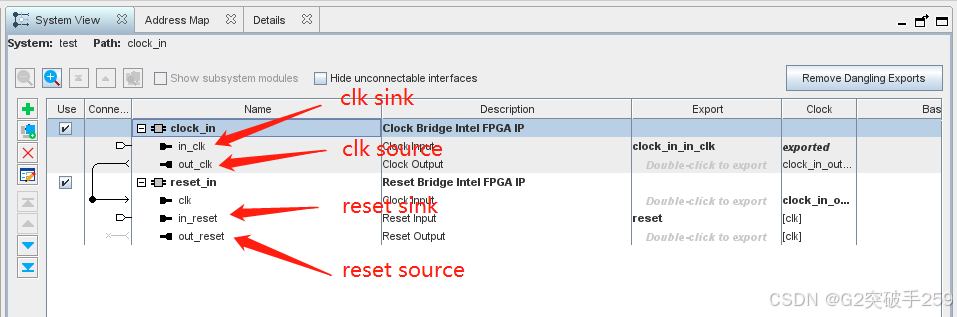

以下为 Platform Designer 中的 clock sink,clock source,reset sink,reset source 接口:

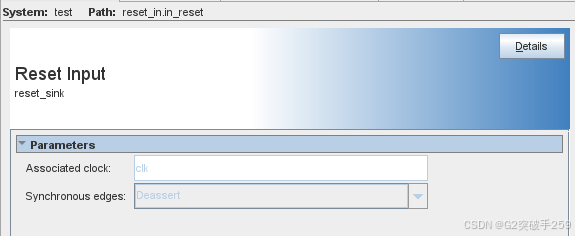

reset sink 接口属性

- associatedClock:接口同步时钟名称,与此接口同步的时钟的名称。如果 synchronousEdges 的值为 DEASSERT 或者 BOTH,那么需要使用此属性。

- synchronous-Edges:表明复位输入所需要的同步类型。以下值定义为:NONE-不需要同步,DEASSERT-异步复位同步释放,BOTH-同步复位同步释放。

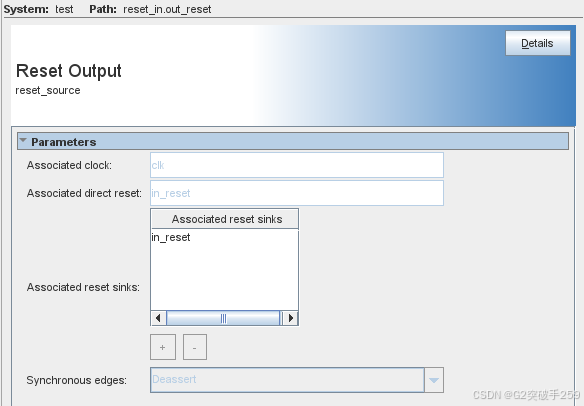

reset source 接口属性

- associatedClock:与此接口同步的时钟的名称。如果 synchronousEdges 的值为 DEASSERT 或者 BOTH,那么需要使用此属性。

- associatedDirectReset:复位输入的名称,此复位输入通过 one-to-one 链路直接驱动此复位源(reset source)。

- associatedResetSinks:指定复位输入,使复位源置位复位。例如,reset synchronizer,执行与多个复位输入的 OR 操作来生成一个复位输出。

- synchronous-Edges:表示复位输出的同步。以下值定义为:NONE-不需要同步,DEASSERT-异步复位同步释放,BOTH-同步复位同步释放。

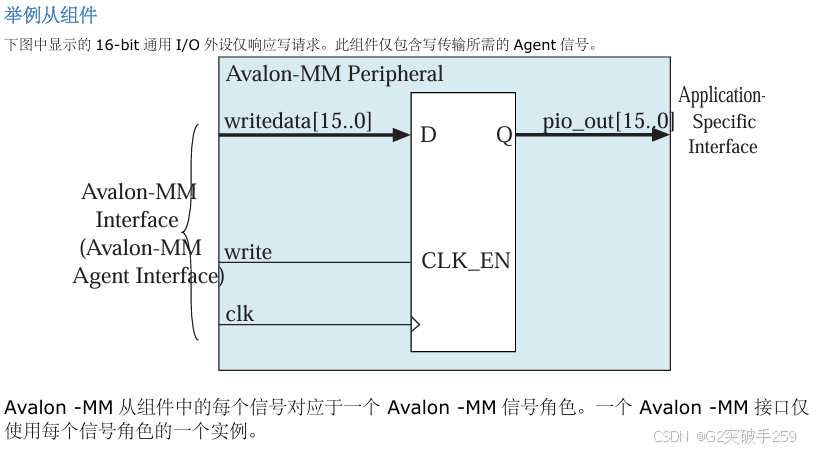

Avalon Memory-Mapped Interfaces

您可以使用 Avalon Memory-Mapped(Avalon -MM)接口实现主从组件的读写接口。以下是通常包含存储器映射接口的组件示例:

- 微处理器

- 储存器

- UART

- DMA

- 计时器(Timer)

Avalon -MM 接口,有的简单有的复杂。例如,SRAM 接口有固定周期的读写传输,具有简单的 Avalon -MM 接口。能够进行突发传输的流水线接口(pipelined interface)很复杂。

传输

本节在介绍传输类型之前定义了两个基本概念:

- 传输(Transfer)— 传输是一个字或者数据的一个或多个符号的读或写操作。传输发生在 Avalon-MM 接口与互连之间。传输需要一个或多个时钟周期才能完成。

host 和 agent 都是传输的一部分。Avalon -MM host 启动传输,Avalon -MM agent 作出响应。 - Host - Agent pair — 此术语是指一个传输中涉及的 host 接口和 agent 接口。在一个传输过程中,host 接口控制和数据信号遍布互连架构,并与 agent 接口进行交互。

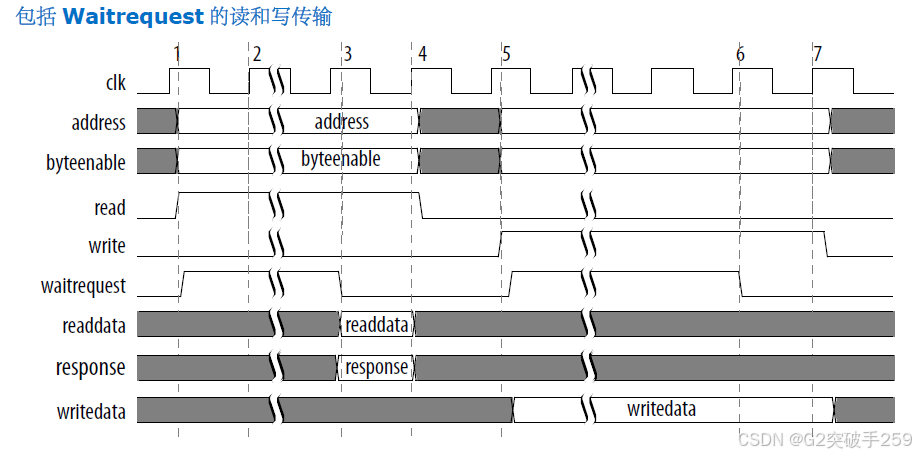

典型的读传输和写传输

本节介绍了一个典型的 Avalon -MM 接口,通过 agent 控制的 waitrequest 来支持读写传输。通过置位 waitrequest 信号,agent 能够将互连暂停所需的周期。如果一 个 agent 将 waitrequest 用于读传输或者写传输,那么该 agent 必须对两者都使用 waitrequest。

agent 通常在时钟的上升沿之后接收 address,byteenable,read 或者 write 和 writedata。在上升时钟沿之前,agent 置位 waitrequest 来暂停传输。当 agent 置位 waitrequest 时,传输延迟。waitrequest 置位期间,地址和其他控制信号保持不变。agent 接口解除置位 waitrequest 之后,第一个 clk 上升沿上的传输完成。

对 agent 接口暂停的时间长短没有限制。因此,您必须确保 agent 接口不要无限期置位 waitrequest。下图显示了使用 waitrequest 的 read 和 write 传输。

注意:waitrequest 能够从 read 和 write 请求信号中解耦。可在空闲周期置位 waitrequest。当 waitrequest 置位时,Avalon -MM host 可以启动一个事务,并等待此信号解除置位。将 waitrequest 从 read 和 write 请求进行解耦可以提高系统时序。解耦消除了包含 read,write 和 waitrequest 信号的组合环路(combinational loop)。如果要求更多的解耦,那么使用 waitrequestAllowance 属 性。从 Quartus® Prime Pro v17.1 Stratix® 10 ES 版本发布起包含 waitrequestAllowance 属性。

此时序图中的数字标记以下转换:

- address,byteenable 和 read 在 clk 的上升沿后置位。agent 置位 waitrequest,暂停传输。

- waitrequest 被采样。由于 waitrequest 置位,因此周期变成一个等待状态(waitstate)。address,read,write 和 byteenable 保持不变。

- agent 在clk 的上升沿之后解除置位 waitrequest。agent 置位 readdata 和 response。

- host 对 readdata,response 和解除置位的 waitrequest(完成传输)进行采样。

- address,writedata,byteenable 和 write 信号在 clk 的上升沿之后置位。agent 置位 waitrequest,暂停传输。

- agent 在 clk 的上升沿之后解除置位 waitrequest。

- agent 采样写数据结束传输。

关于使用 waitrequestAllowance 属性进行传输的相关内容,请查看手册,这里不再过多介绍。

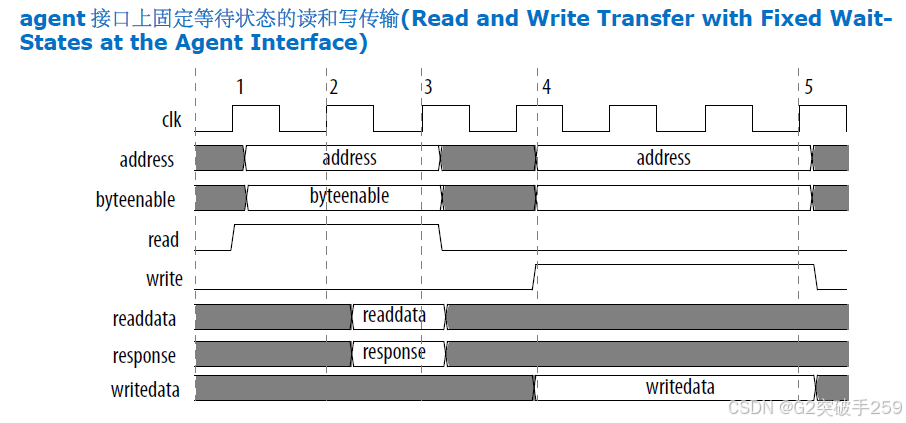

固定等待状态的读和写传输(Read and Write Transfers with Fixed Wait-States)

agent 可以使用 readWaitTime 和 writeWaitTime 属性来指定固定等待状态。使用固定等待状态是使用 waitrequest 来停止传输的一个替代方法。地址和控制信号(byteenable,read 和 write)在传输期间保持不变。将 readWaitTime 或 writeWaitTime 设置为 相当于将 waitrequest 置位 个周期每传输。

下图中,agent 有 writeWaitTime = 2 和 readWaitTime = 1。

此图中的编号标识了以下转换:

- host 在 clk 的上升沿置位 address 和 read。

- clk 的下一个上升沿标记第一个也是唯一一个等待状态(wait-state)周期的结束。readWaitTime 为 1。

- agent 在 clk 的上升沿置位 readdata 和 response。读传输结束。

- agent 可使用 writedata,address,byteenable 和 write 信号。

- 写传输在 2 个等待状态(wait-state)周期后结束。

单一等待状态的传输通常用于多周期片外(off-chip)外设。外设在 clk 的上升沿采集地址和控制信号。外设有一个完整的周期来返回数据。

允许组件的零等待状态。然而,零等待状态的组件可能会降低可实现的频率。零等待状态要求组件在出现请求的同一周期中生成响应。

流水线传输(Pipelined Transfers)

Avalon -MM 流水线读传输增加同步从器件的吞吐量,这些同步从器件需要几个周期才能返回第一次访问的数据。这样的器件通常可以在一段时间后每个周期返回一个数据值。新流水线读传输可以在先前传输的readdata 返回之前启动。

流水线读传输有一个地址阶段(address phase)和一个数据阶段(data phase)。host 通过在地址阶段期间提供地址来启动一个传输。agent 通过在数据阶段期间传送数据来完成传输。一个新传输(或者多个传输)的地址阶段可以在先前传输的数据阶段完成之前开始。此延迟称为流水线延迟(pipeline latency)。流水线延迟是从地址阶段结束到数据阶段开始的持续时间。

等待状态和流水线延迟的传输时序有以下主要差异:

- 等待状态(wait-states)— 等待状态决定地址阶段的长度。等待状态限制一个端口的最大吞吐量。如果 agent 需要一个等待状态来响应一个传输请求,那么端口需要每传输两个时钟周期。

- 流水线延迟(Pipeline Latency)— 流水线延迟决定独立于地址阶段数据返回的时间。无等待状态的流水线 agent 可以维持每周期一个传输。但是,agent 可能需要几个周期的延迟才能返回数据的第一个单元。

可以同时支持等待状态和流水线读取。流水线延迟可以是固定的也可以是可变的。

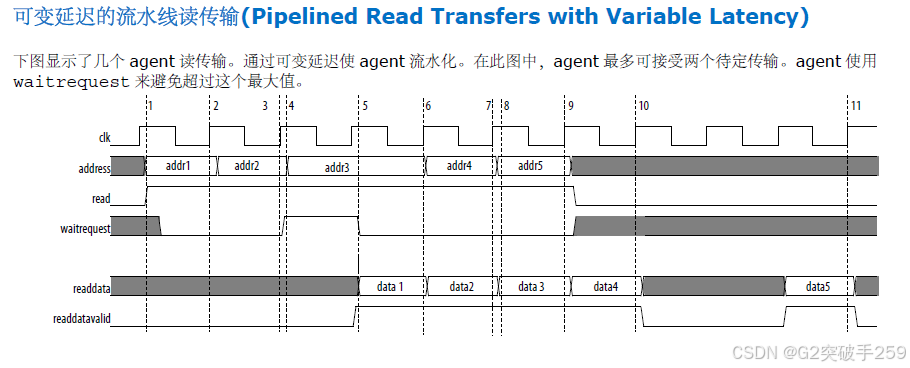

可变延迟的流水线读传输(Pipelined Read Transfer with Variable Latency)

采集地址和控制信号后, Avalon -MM 流水线 agent 需要一个或多个周期来生成数据。流水线 agent 可以在任何给定时间有多个待定读传输。

可变延迟流水线读传输:

- 需要一个额外信号,readdatavalid,指示读数据何时有效。

- 包括与非流水线读传输相同的一组信号。

在可变延迟流水线读传输中,使用 readdatavalid 的 agent 外设被认为是通过可变延迟进行流水线化的。对应于一个读命令的 readdata 和 readdatavalid 信号最早可以在此读命令置位后的周期中置位。

agent 必须按照接受读命令的相同顺序返回 readdata。具有可变延迟的流水线 agent 端口必须使用 waitrequest。agent 可以通过置位 waitrequest 来停止传输,以保持一个可接受数量的待定传输。agent 可以通过置位 readdatavalid 将数据传输到 host,而不用考虑 agent 是否通过 waitrequest 来暂停一个新命令。

注意:待定传输的最大数量是从接口(agent interface)的一个属性。互连架构使用此数量来构建逻辑,将 readdata 布线到请求的 host。从接口(而非互连架构)必须跟踪待定读取的数量。agent 必须置位 waitrequest 以防止待定读取的数量超过最大数量。如果 agent 有 waitrequestAllowance > 0,那么 agent 必须尽早地置位 waitrequest,以便待定传输总数(包括在 waitrequest 置位期间接受的那些数量)不超过指定的待定传输的最大数量。

此图中的编号标识了以下转换:

- host 置位 address 和 read,启动一个读传输。

- agent 捕获 addr1。

- agent 捕获 addr2。

- 由于 agent 已经接受最多 2 个待定读取,因此 agent 置位 waitrequest,从而导致第三个传输停止。

- agent 置位 data1,即对 addr1 的响应。agent 解除置位 waitrequest。

- agent 捕获 addr4。互连捕获 data2。

- agent 捕获 addr4。互连捕获 data2。

- agent 驱动 readdatavalid 和 readdata 以响应第三次读传输。

- agent 驱动 addr5。互连捕获 data3。read 信号被解除置位。waitrequest 的值不再相关。

- interconnect 采集data4。

- agent 驱动 data5,并置位 readdatavalid,完成最后待定读传输的数据阶段。

如果 agent 在处理待定读传输时无法处理写传输,那么 agent 必须置位 waitrequest,并且停止写操作,直到完成待定读传输。在 agent 接受对与当前待定读传输相同地址的写传输的情况下,Avalon -MM 规范没有定义 readdata 的值。

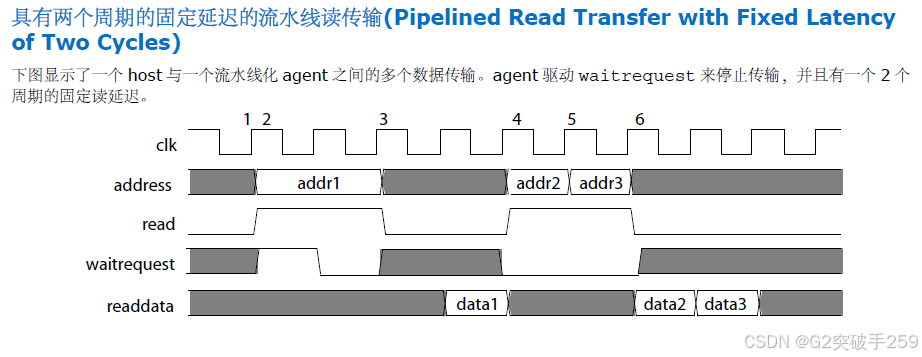

固定延迟的流水线读传输(Pipelined Read Transfer with Fixed Latency)

固定延迟读传输的地址阶段与可变延迟情况相同。在地址阶段之后,具有固定读延迟的流水线 agent 需要固定数量的时钟周期才能返回有效的 readdata。readWaitTime 属性指定返回有效 readdata 的时钟周期数。互连在相应的上升时钟边沿捕获 readdata,结束数据阶段。

在地址阶段,agent 通过置位 waitrequest 来阻止传输。或者,agent 对固定数量的等待状态指定 readWaitTime。在等待状态(如有)之后,地址阶段在 clk 的下一个上升沿结束。

在数据阶段,agent 在一个固定延迟后驱动 readdata。对于一个值为 的读延迟,agent 在地址阶段结束后必须在 clk 的 上升沿呈现有效的 readdata。

此时序图中的编号标识了以下转换:

- host 通过置位 read 和 addr1 启动一个读传输。

- 置位 waitrequest 以使传输暂停一个周期。

- agent 在 clk 的上升沿捕获 addr1。地址阶段在此结束。

- agent 在 2 个周期后呈现有效的 readdata,传输结束。

- 对一个新的读传输置位 addr2 和 read。

- 在返回先前传输的数据之前,host 在下一个周期内启动第三次读传输。

突发传输(Burst Transfers)

突发(burst)将多个传输作为一个单元进行执行,而不是独立地处理每个字。突发可以增加 agent 端口的吞吐量,从而在一次处理多个字时实现更高的效率,例如 SDRAM。突发的净效应是锁定突发持续时间的仲裁。支持读写操作的突发 Avalon -MM 接口一定支持读写突发。

突发 Avalon -MM 接口包含一个 burstcount 输出信号。如果 agent 有一个 burstcount 输入,那么 agent 具有突发能力。

burstcount 信号的行为如下:

- 在突发的开始,burstcount 表示突发中有序传输的数量。

- 对于 burstcount 的宽度 ,最大突发长度为 2(-1)。最小法定突发长度为 1。

如要支持 agent 读突发,agent 也必须支持:

- 使用 waitrequest 信号的等待状态。

- 使用 readdatavalid 信号的可变延迟的流水线传输。

在突发的开始,agent 看到 address 和 burstcount 上的突发长度值。对于一个地址为 a 和 burstcount 值为 b 的突发,agent 必须从地址 a 开始执行 b 个连续传输。在agent 接收(写)或返回(读)b th 字的数据后完成突发。突发 agent 必须对每个突发采集一次 address 和 burstcount。agent 逻辑必须对突发中的所有传输(但不包括第一个传输)推断地址。agent 也可以使用输入信号 beginbursttransfer,互连在每个突发的第一个周期对此信号进行置位。

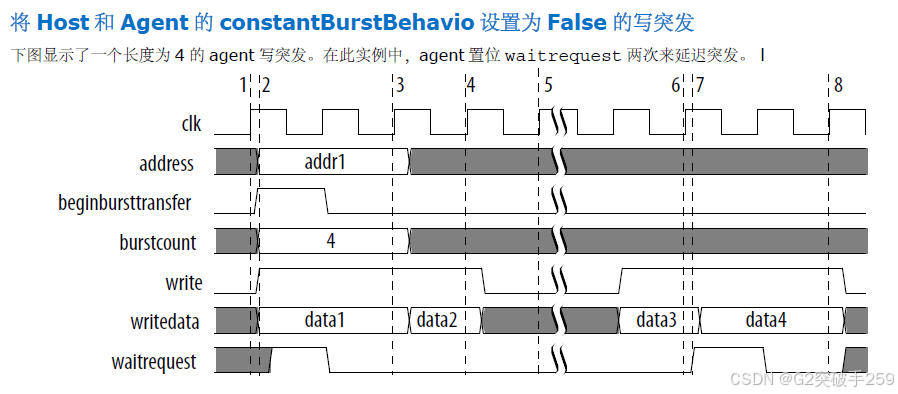

写突发(Write Bursts)

这些规则应用于一个写突发开始于大于 1 的 burstcount 的情况:

- 当值为 的 burstcount 出现在突发的开始时,agent 必须接受 个连续单元的 writedata 以完成突发。host-agent 对之间的仲裁保持锁定,直到突发完成。此锁定保证在写突发完成之前没有其他 host 能够在 agent 上执行事务。

- agent 必须在 write 置位时才能捕获 writedata。在突发期间,host 通过解除 write 置位时才能捕获 writedata。解除置位 write 不会终止突发。write 解除置位会延迟突发,并且没有其他 host 可以访问 agent,从而降低了传输效率。

- agent 通过置位 waitrequest,强制 writedata,write,burstcount 和 byteenable 保持不变来延迟一个传输。

- byteenable 信号的功能对于突发和非突发 agent 是相同的。对一个 64-bit agent 的 32- bit host 突发写操作(burst-writing),从字节地址 4 开始,agent 看到的第一个写传输在它的地址 0 上,byteenable = 8’b11110000。byteenables 可以根据突发的不同字进行改变。

- byteenable 信号不必都置位。突发 host 写局部字能够使用 byteenable 信号识别当前被写入的数据。

- 将全部为 0 的 byteenable 信号的写操作作为有效事务传递到 Avalon -MM agent。

- constantBurstBehavior 属性指定突发信号的行为。

当 constantBurstBehavior 对于一个 host 为 true 时,此 host 在整个突发期间保持 address 和 burstcount 稳定。当对一个 agent 为 true 时,constantBurstBehavior 声明此 agent 期望 address 和 burstcount 在整个突发期间保持稳定。

当 constantBurstBehavior 为 false 时,host 仅对突发的第一个事务保持 address 和 burstcount 稳定。当 constantBurstBehavior 为 false 时,agent 仅在突发的第一个事务上采集 address 和 burstcount。

此时序图中的编号标识了以下转换:

- host 置位 address,burstcount,write 并驱动 writedata 的第一个单元。

- agent 立即置位 waitrequest,表明 agent 尚未准备好继续传输。

- waitrequest 为低电平。agent 捕获 addr1,burstcount 和 writedata 的第一个单元。在随后的传输周期中,address 和 burstcount 被忽略。

- agent 在 clk 的上升沿采集数据的第二个单元。

- write 解除置位期间突发暂停。

- agent 在 clk 的上升沿采集数据的第三个单元。

- agent 置位 waitrequest。作为响应,所有输出在另一个时钟周期内保持不变。

- agent 在 clk 的上升沿采集数据的最后一个单元。agent 写突发结束。

上图中,beginbursttransfer 信号在突发的第一个时钟周期置位,在下一个时钟周期解除置位。即便 agent 置位waitrequest,beginbursttransfer 信号也仅在第一个时钟周期置位。

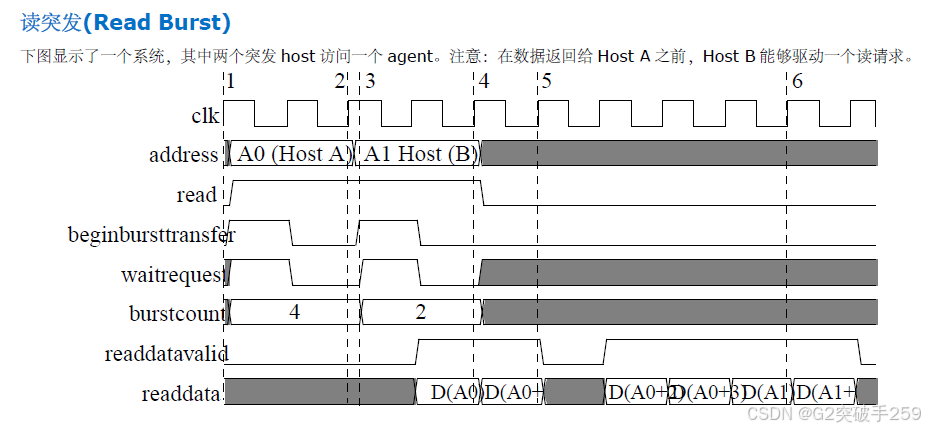

读突发(Read Bursts)

读突发类似于具有可变延迟的流水线读传输。读突发有不同的地址和数据阶段。readdatavalid 会指示 agent 出现有效 readdata。与流水线读传输不同,单个读突发地址会导致多个数据传输。

读突发规则应用如下:

- 当一个 host 直接连接到一个 agent 时,值为 的 burstcount 意味着此 agent 必须返回 个字的 readdata才能完成突发。在互连链接到 host 和 agent 对的情况下,互连可以抑制从 host 发送到 agent 的读命令。例如,如果 host 发送一个读命令,其中 byteenable 的值为 0,那么互连可能会抑制此读操作。因此,agent 不会响应读命令。

- agent 通过提供 readdata 和置位 readdatavalid 一个周期来呈现每个字。解除置位 readdatavalid 会延迟突发数据阶段,但不会终止突发数据阶段。

- 对于 burstcount > 1 的读操作,Intel 建议置位所有 byteenables。

注意:Intel 建议具有可突发的 agent 无读取副作用。(此规范不保证 host 从 agent 读取多少个字节才

满足一个请求。)

此时序图中的编号标识了以下跳变:

- host A 在 clk 的上升沿之后置位 address (A0),burstcount 和 read。agent 置位 waitrequest,导致除了 beginbursttransfer 之外的所有输入在另一个时钟周期内保持不变。

- agent 在 clk 的上升沿捕获 A0 和 burstcount。一个新的传输可能在下个周期开始。

- host B 驱动 address (A1),burstcount 和 read。agent 置位 waitrequest,导致 beginbursttransfer 以外的所有输入保持不变。agent 最早可以在此时从第一个读请求中返回读数据。

- agent 呈现有效的 readdata 并置位 readdatavalid,传输 host A 的数据的第一个字。

- 传输 host A 的第二个字。agent 解除置位 readdatavalid,暂停读突发。agent 端口能够保持 readdatavalid 解除置位任意数量的时钟周期。

- 返回 host B 的第一个字。

读和写响应

对于任何 Avalon-MM agent,必须以无危险的方式处理命令。读和写响应按接受命令的顺序发出。

Avalon-MM 读和写响应的事务顺序(Host 和 Agent)

对于任何 Avalon-MM host:

- Avalon 接口规范保证对同一 agent 发出的命令以命令发出的顺序到达 agent,并且 agent 以 命令发出的顺序进行响应。

- 不同的 agent 可以以 host 发布命令不同的顺序接收和响应命令。成功后 agent 以命令发出的顺序进行响应。

- 响应(如果存在)以命令发出的顺序进行返回,不管读或写命令是针对同一 agent 还是不同的 agent。

- Avalon 接口规范不保证不同主机之间的事务顺序。

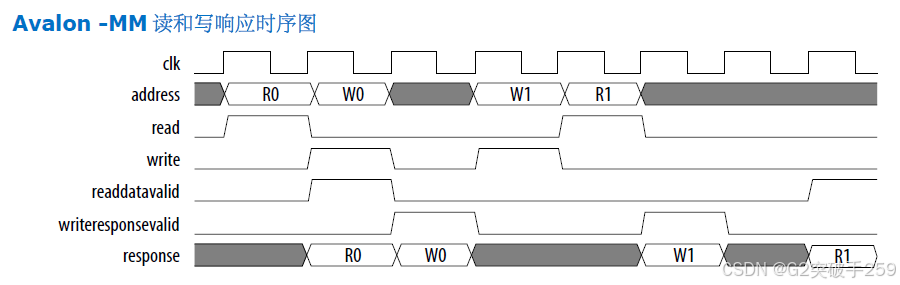

Avalon-MM 读和写响应时序图

下图显示了 Avalon-MM 读和写响应的命令接受和命令发送的顺序。由于读和写接口共享 response 信号,因此一个接口不能够在同一时钟周期中发出或接受一个写响应和一个读响应。

读响应,对每个 readdata 发送一个响应。一个为 的读突发长度会产生 个响应 。

写响应,对每个写命令发送一个响应。一个写突发仅产生一个响应。从接口(agent interface)在接收到突发中的最后写传输后发送响应。当一个接口包括 writeresponsevalid 信号时,所有写命令必须通过写响应来完成。

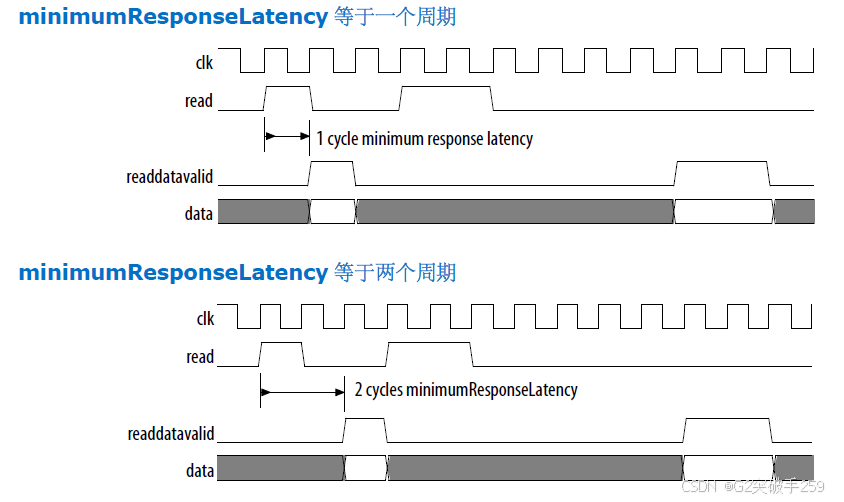

对于 readdatavalid 或者 writeresponsevalid 的接口,默认的一个周期 minimumResponseLatency 能导致 Avalon-MM host 上时序收敛困难。

下面时序图显示了 1 或 2 个周期的 minimumResponseLatency 的行为。请注意:实际的响应延迟也可以大于这些时序图中显示的最小允许值。

Avalon Interrupt Interface

Avalon 中断接口允许从组件(agent components)能够向主组件(host components)发送事件信号。例如,DMA 控制器可以在完成一个 DMA 传输后中断处理器。

中断发送器(Interrupt Sender)

中断发送器将单个中断信号驱动到中断接收器。irq 信号的时序必须与其相关联时钟的上升沿同步。irq 与任何其他接口上的任何传输无关。irq 必须一直置位,直到相关联的 Avalon-MM 从接口上确认接收。

中断是特定于组件的。接收器通常通过读取 Avalon-MM 从接口中中断状态寄存器来确定相应的响应。

中断接收器(Interrupt Receiver)

中断接收器接口接收来自中断发送器接口的中断。具有 Avalon-MM 主接口的组件可以包含一个中断接收器,用于检测由包含中断发送器接口的从组件置位的中断。中断接收器接受来自每个中断发送器(作为一个单独的比特)的中断请求。

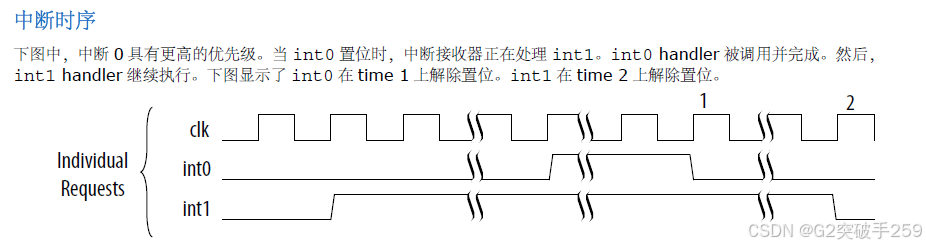

中断时序

Avalon-MM host 先服务优先级 0 中断,再服务优先级 1 中断。

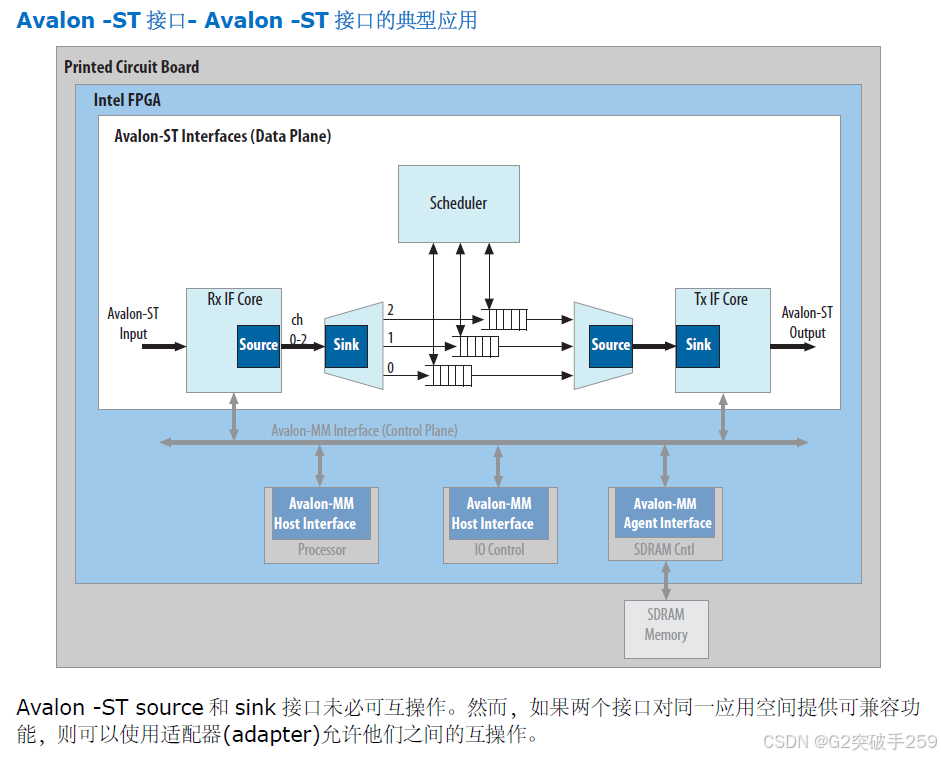

Avalon Streaming Interface

Avalon Streaming(Avalon-ST)接口可用于驱动高带宽,低延迟,单向数据的组件。典型应用包括多路复用流(multiplexed streams),数据包和 DSP 数据。 Avalon-ST 接口信号可以描述支持单个数据流的传统流接口,而无需了解通道或数据包边界。此接口还支持更复杂的协议,能够在多个通道之间进行数据包交错的突发和数据包传输。

Avalon-ST 接口支持要求如下功能的数据通路:

- 低延迟,高吞吐量的点对点数据传输

- 灵活数据包交错的多通道支持

- 通道,错误和数据包描述的开始与结束的边带信号

- 支持数据突发(data bursting)

- 自动接口适配(automatic interface adaptation)

信号详情

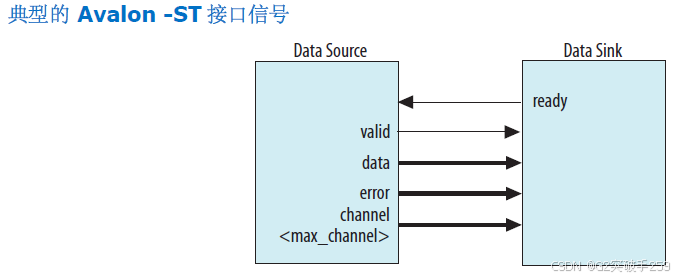

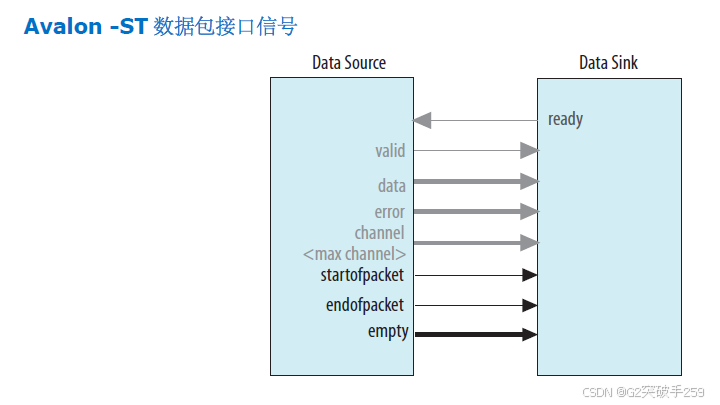

下图显示了 Avalon-ST 接口通常包含的信号。一个典型的 Avalon-ST source 接口将 valid,data,error 和 channel 信号驱动到 sink。sink 可以使用 ready 信号来应用背压(backpressure)。

数据布局(Data Layout)

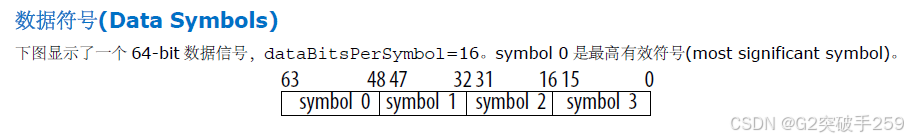

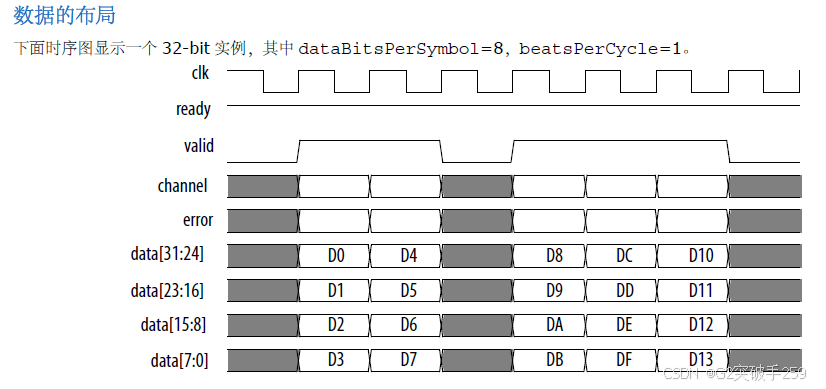

Avalon Streaming 接口支持 big-endian 和 little-endian 模式。下图是 big-endian 模式的实例,其中 Symbol 0 在高位比特。

无背压的数据传输

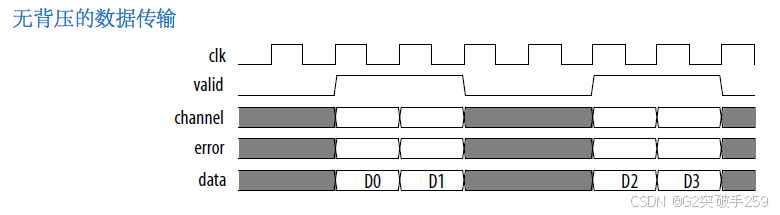

无背压的数据传输是最基本的 Avalon-ST 数据传输。在任何給定的时钟周期上,source 接口驱动 data 和可选的 channel 和 error 信号,并置位 valid。如果 valid 置位,那么 sink 接口在参考时钟的上升沿采样这些信号。

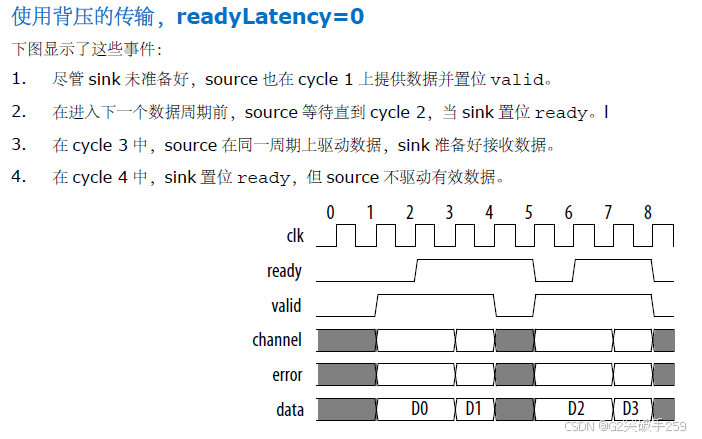

有背压的数据传输

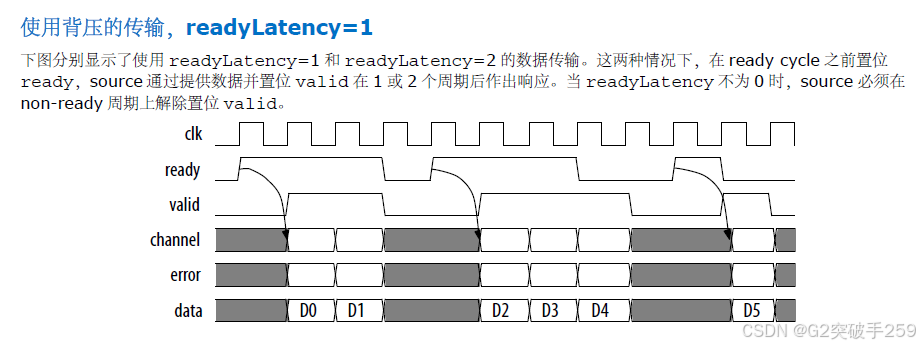

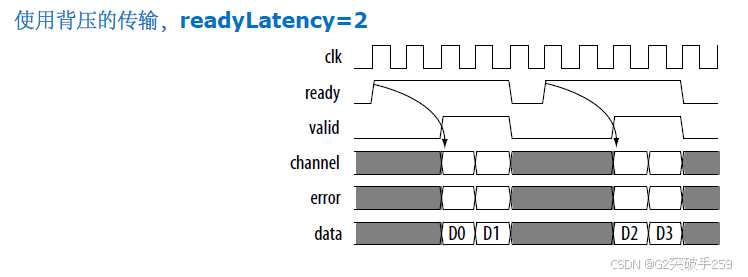

sink 置位 ready 一个时钟周期来表明已对一个活动周期准备就绪。如果 sink 对数据已准备就绪,则该周期就是一个 ready 周期。在一个 ready 周期中,source 可以置位 valid 并提供数据给 sink。如果 source 没有要发送的数据,那么 source 解除置位 valid,并且能够将 data 驱动到任何值。

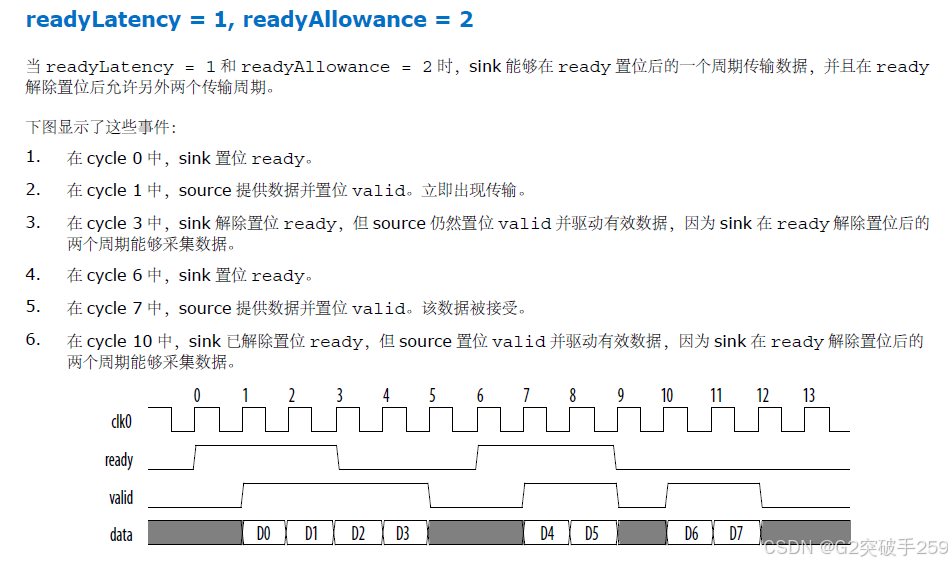

支持背压的接口定义 readyLatency 参数来表示从 ready 置位到能够驱动有效数据的周期数量。如果 readyLatency 为非零值,那么 cycle <n + readyLatency> 是一个 ready cycle(如果 ready 在 cycle 上置位)。

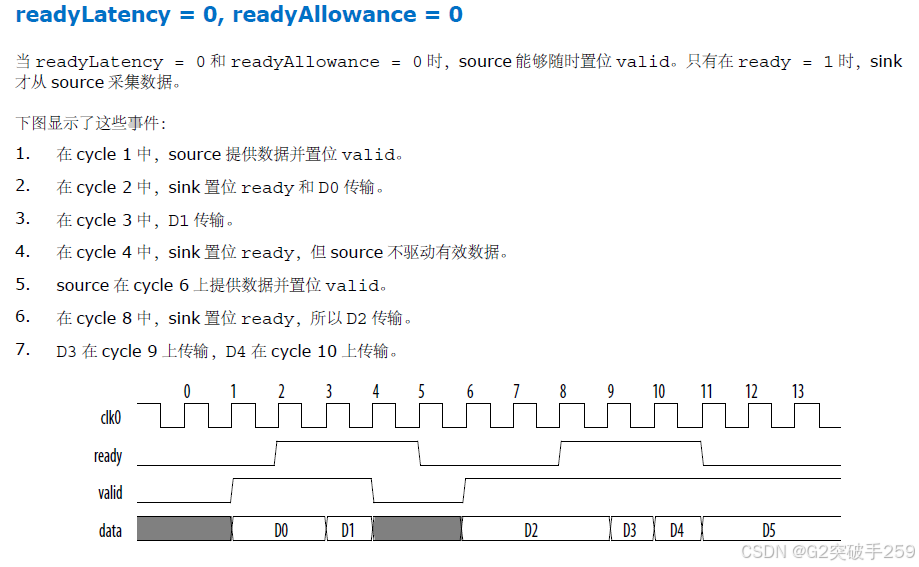

当 readyLatency = 0 时,只有当 ready 和 valid 在同一周期上置位时才会出现数据传输。此模式下,source 在发送有效数据之前不会接收到 sink 的 ready 信号。source 提供数据,只要有有效数据就会置位 valid。source 等待 sink 采集数据并置位 ready。source 可随时改变数据。只有 ready 和 valid 都置位时,sink 才从 source 采集输入数据。

当 readyLatency >= 1 时,sink 在 ready 周期本身之前置位 ready。source 通过置位 valid 在相应的周期中能够作出响应。在非 ready 的周期中,source 可以不置位 valid。

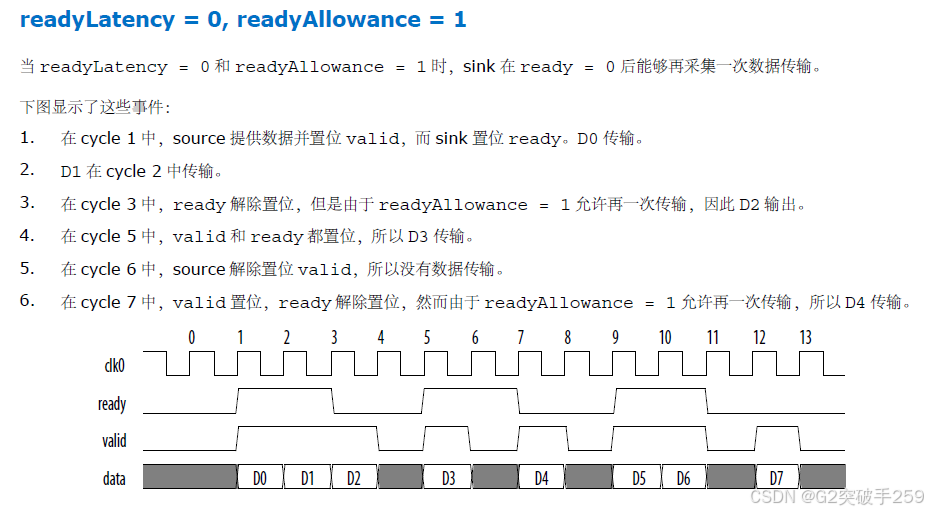

readyAllowance 定义了 ready 解除置位时 sink 能够采集的传输数量。当 readyAllowance = 0 时,sink 在 ready 解除置位后不能接受任何传输。如果 readyAllowance = ,其中 n > 0,那么 sink 在 ready 解除置位后最多能够接受 个传输。

使用 readyLatency 和 readyAllowance 的数据传输

以下规则应用于使用 readyLatency 和 readyAllowance 传输数据时。

- 如果 readyLatency 为 0,那么 readyAllowance 可以大于或等于 0。

- 如果 readyLatency 大于 0,那么 readyAllowance 可大于或等于 readyLatency。

当 readyLatency = 0 和 readyAllowance = 0 时,只有在 ready 和 valid 都置位时数据才会传输。在此情况下,source 在发送有效数据之前不会接收到 sink 的 ready 信号。source 提供数据并尽可能置位 valid。source 等待 sink 采集数据并置位 ready。source 可随时改变数据。只有 ready 和 valid 都置位时,sink 才从 source 采集输入数据。

使用 readyLatency 的数据传输

如果 source 或者 sink 没有指定 readyAllowance 的值,那么 readyAllowance = readyLatency。使用 source 和 sink 的设计不需要添加 readyAllowance,除非需要 source 或者 sink 利用此特性。

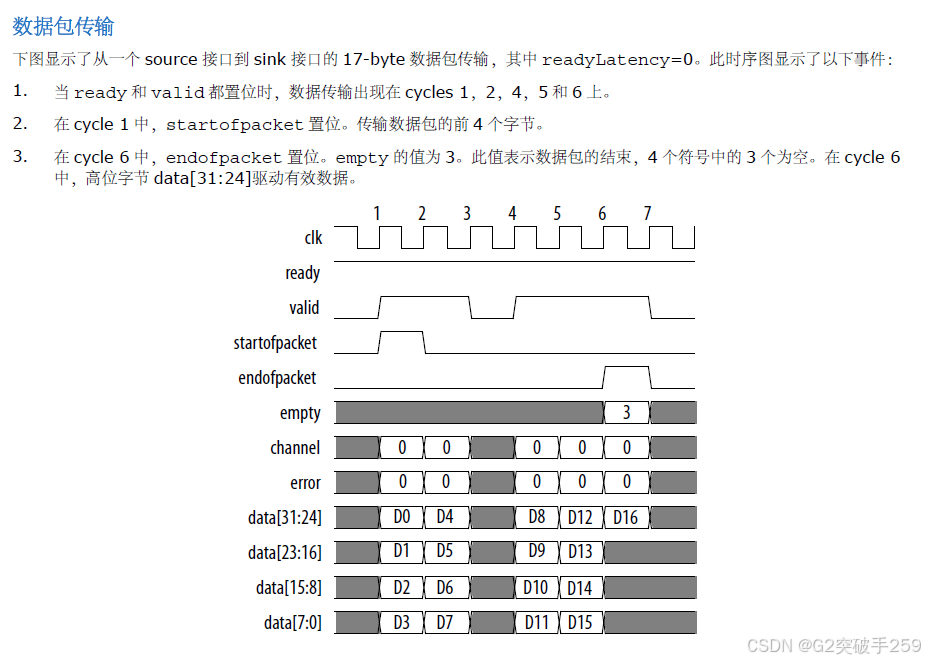

数据包数据传输(Packet Data Transfers)

数据包传输属性增加了从 source 接口到 sink 接口的数据包传输支持。定义了三个附加信号以实现数据包传输。source 接口和 sink 接口都必须包含这些附加信号才能支持数据包。您只能使用匹配的数据包属性来连接 source 接口和 sink 接口。Platform Designer 不自动将 startofpacket,endofpacket 和 empty 信号添加到不包含这些信号的 source 或 sink 接口。

信号详情

- startofpacket — 支持数据包传输的所有接口都需要 startofpacket 信号。 startofpacket 对包含数据包起始部分的活动周期作标记。只有 valid 置位时才会解释此信号。

- endofpacket — 支持数据包传输的所有接口都需要 endofpacket 信号。endofpacket 对包含数据包结束部分的活动周期作标记。只有 valid 置位时才会解释此信号。 endofpacket 可以在同一周期置位。在数据包之间不需要空闲周期。startofpacket 信 号可以紧跟在前一个 endofpacket 信号之后。

- empty — 可选的 empty 信号表示在 endofpacket 周期中空的符号数量。sink 仅在 endofpacket 置位的活动周期中检查 empty 的值。空字符总是 data 中的最后字符,当 firstSymbolInHighOrderBits = true 时由低位比特(low-order bits)表示。在所有 的数据包接口(这些数据包接口的 data 信号承载一个以上的符号数据并具有一个可变长度数据包格式)上都需要 empty 信号。empty 信号的大小(以比特为单位)ceil [log2()]。

协议详情

数据包数据传输遵循与典型数据传输相同的协议,增加了 startofpacket,endofpacket 和 empty。

Avalon Conduit Interface

Avalon Conduit 接口对任意信号集合进行分组。您可以对管道(conduit)信号指定任何角色。然而在连接管道时,角色和宽度必须匹配,方向必须相反。一个 Avalon Conduit 接口可以包括输入,输出和双向信号。一个模块可以有多个 Avalon Conduit 接口以提供逻辑信号分组。Conduit 接口可以声明相关的时钟。当连接的管道接口位于不同的时钟域中时, Platform Designer 生成错误消息。

注意:如果可能,您应该使用标准 Avalon-MM 或 Avalon-ST 接口,而不是创建一个 Avalon Conduit 接口。Platform Designer 对这些接口提供验证和适配(adaptation)。Platform Designer 不能对 Avalon Conduit 接口提供验证或适配(adaptation)。

管道(conduit)接口通常用于驱动片外器件信号,例如 SDRAM 地址,数据和控制信号。

Avalon Tri-State Conduit Interface

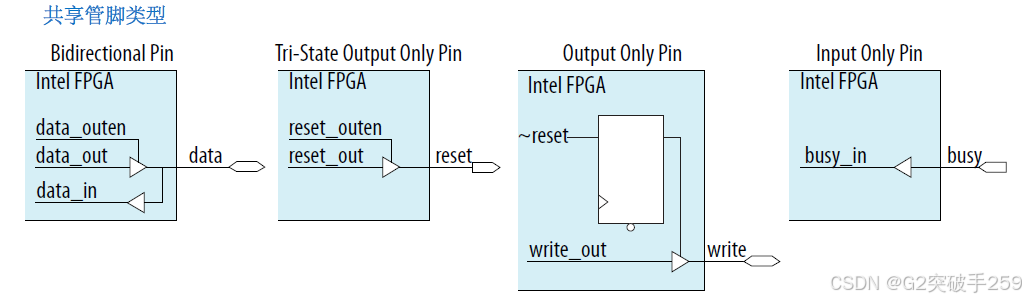

Avalon Tristate Conduit Interface ( Avalon -TC) 是一种点对点接口,专为驱动片外组件的片上控制器而设计。此接口支持在多个三态器件之间共享数据,地址和控制管脚。在包含多个外部存储器件的系统中,共享可以保留管脚。

Avalon-TC 以两种方式对其他常规 Avalon Conduit Interface 进行限制:

- Avalon-TC 需要 request 和 grant 信号。当多个 Tristate Conduit Hosts(TCM)请求访问一条共享总线时,这些信号将使能总线仲裁。

- 必须使用附加到信号角色的后缀来指定信号的管脚类型。三个后缀分别为:_out,_in 和 _outen 。匹配角色前缀识别共享相同 I/O 管脚的信号。以下显示了 Avalon-TC 共享管脚的命名约定。

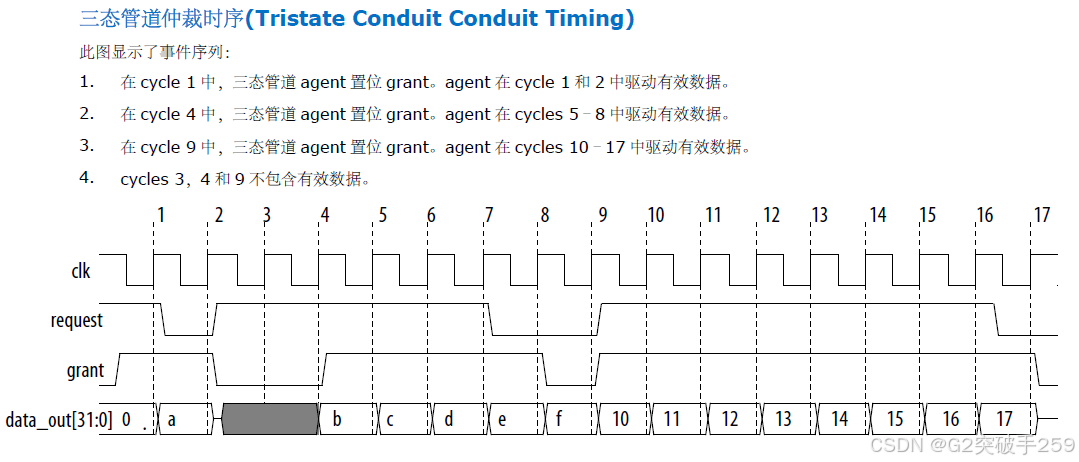

三态管道时序(Tristate Conduit Timing)

下图显示了 Tristate Conduit Pin Sharer 的仲裁时序。请注意,器件能够在授予的周期中驱动或接收有效数据。

1842

1842

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?