知识回顾:

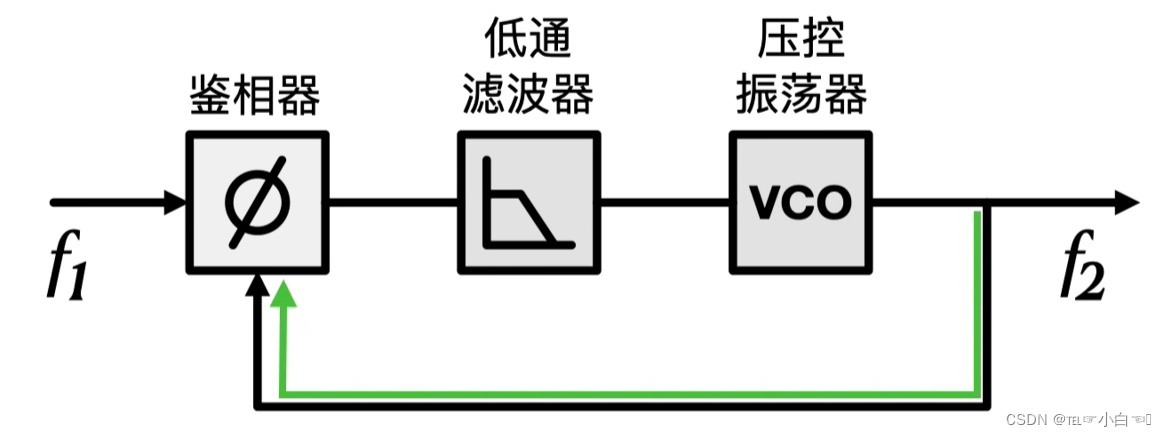

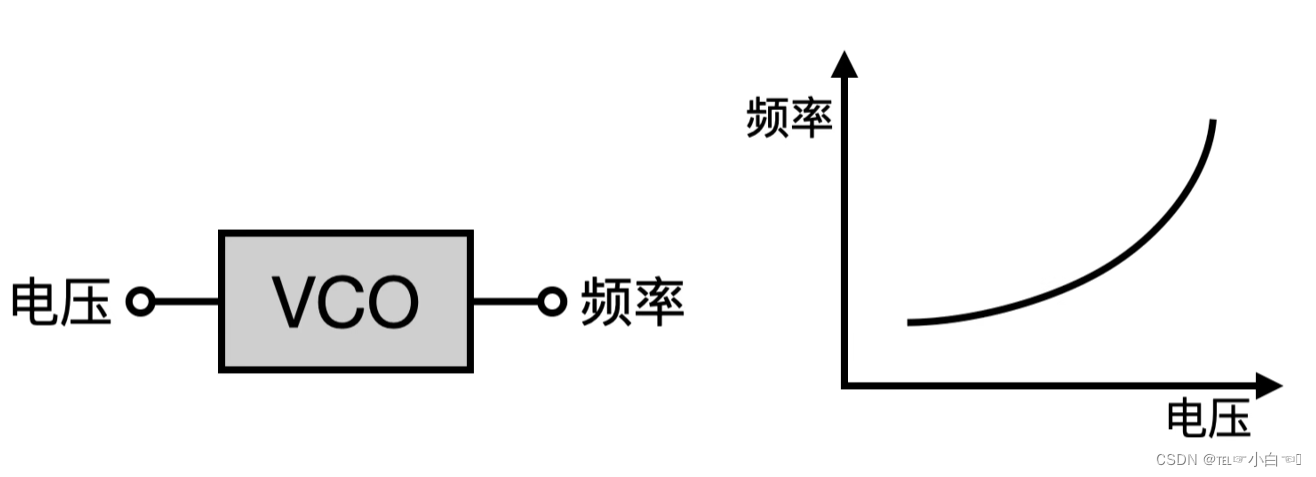

锁相环(Phase-Locked Loop,PLL),是一个能够比较输出与输入相位差的反馈系统,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,使振荡信号同步至参考信号

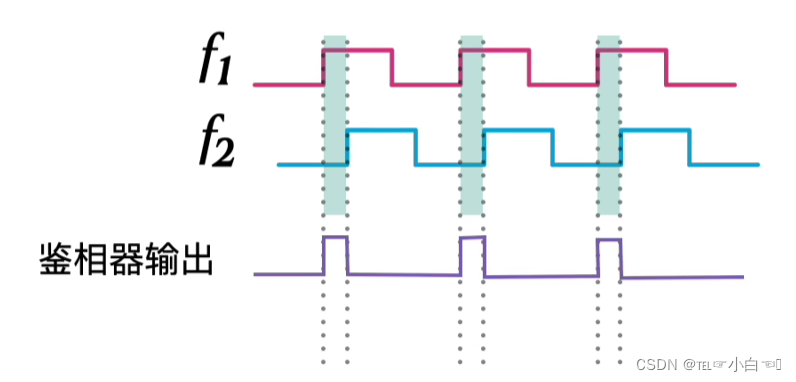

鉴相器有两个输入,分别是晶振信号的输入f1、VCO的输出f2,将两个信号进行比较,如果这两个信号存在相位差异或频率差异,则鉴相器就会在存在差异的这一段进行输出。鉴相器不停的调整输出的电压,使两个相位或频率快速保持一致

由于鉴相器输出的是矩形波,高低电平存在突变,低通滤波器可以让信号变得很平滑。输出的波形如下图所示

本文深入解析了STM32微控制器的时钟系统,包括HSI、HSE、LSI、LSE和PLL等时钟源的工作原理,以及如何配置这些时钟源来满足不同外设的需求。此外,还详细介绍了SysTick定时器的寄存器配置和功能。

本文深入解析了STM32微控制器的时钟系统,包括HSI、HSE、LSI、LSE和PLL等时钟源的工作原理,以及如何配置这些时钟源来满足不同外设的需求。此外,还详细介绍了SysTick定时器的寄存器配置和功能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1209

1209

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?