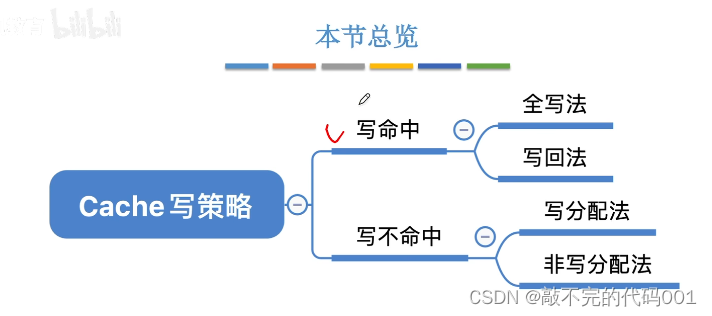

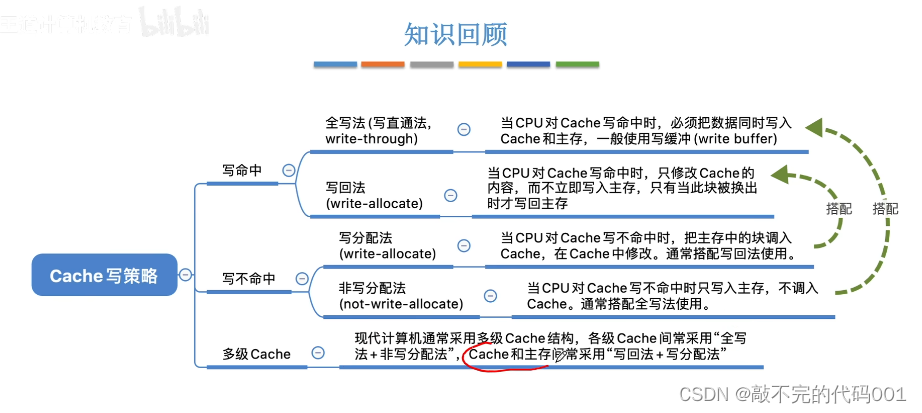

Cache中只是保存了主存中数据的副本,CPU对Cache里的数据进行写操作,修改了里面的数据后,如何保存主存和Cache中数据一致性?——Cache写策略

为什么只探讨写操作?

因为要解决的是Cache和主存数据一致性的问题,如果CPU进行的是读操作而不是写操作,无论是读命中还是读不命中,都不会导致数据不一致的问题。

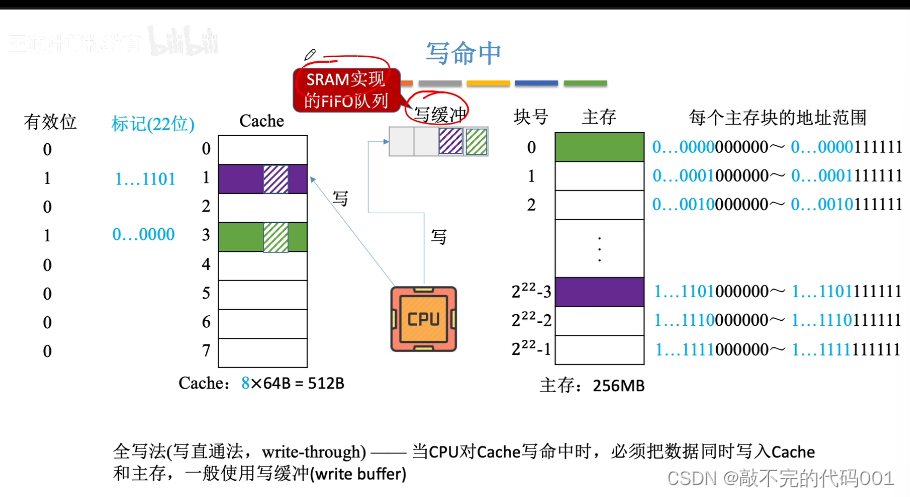

写命中

如果此时CPU要写的那个存储单元被命中,也就是已经存在Cache里面的话,这种情况如何处理?

CPU要对某个地址进行写,而且这个地址所对应的主存块已经被调入Cache中,发生了命中的情况,在这种情况下,有两种方法

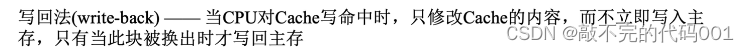

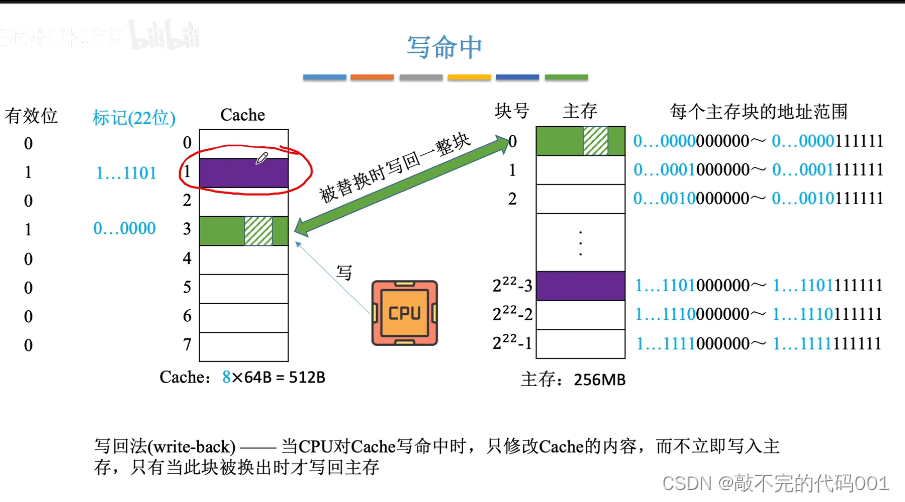

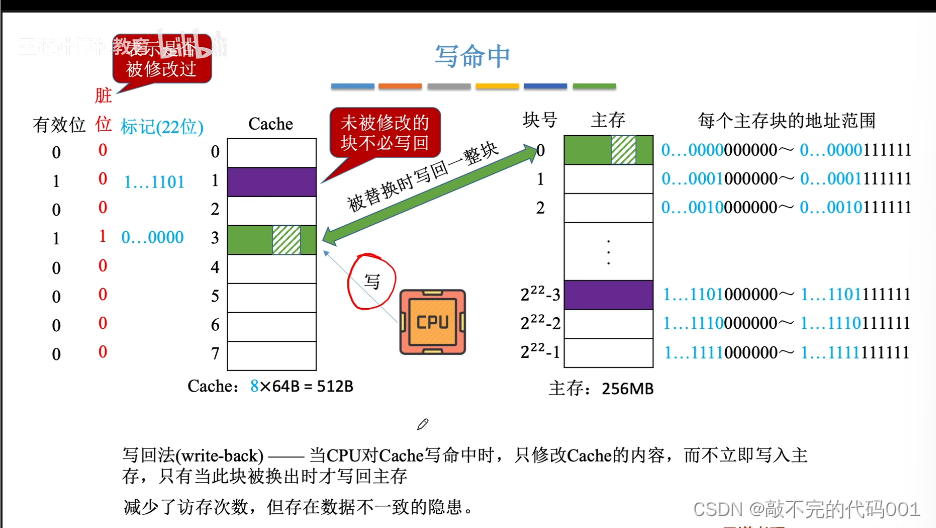

写回法

CPU只写入相应的数据,主存的数据母本和Cache的副本不一致,但是这种不一致只有在这个Cache行下次被替换的时候才会把整个Cache行里一整块的数据全部写回主存

未被修改的Cache行,当这个Cache行被替换的时候就不需要写回,这样就节省了写回的时间

为了区分那个Cache行被修改过那个没有, 所以还需要给每个Cache行增加脏位信息。当数据块被修改后,需要把这个Cache行所对应的脏位设为1,这样的话当我们淘汰某个Cache行的时候,就可以知道这个Cache是否需要写回主存,而到底写回主存那个位置又可以根据标记来判断

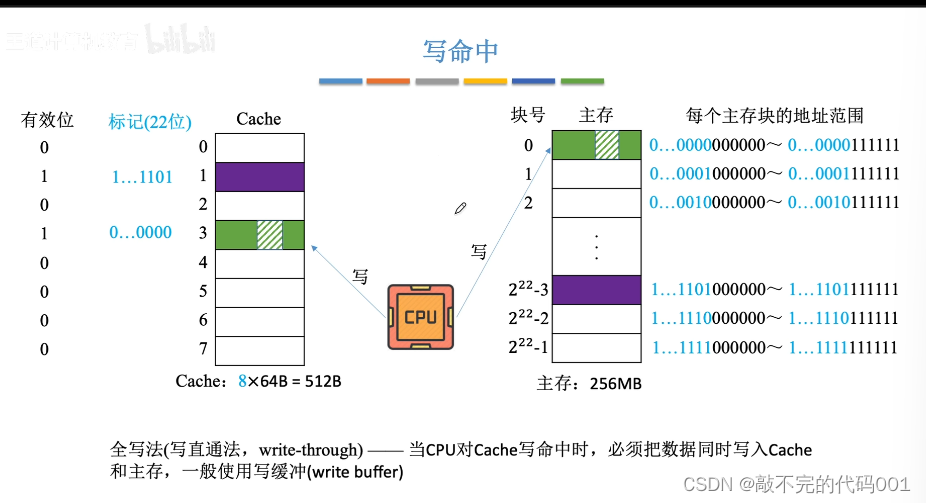

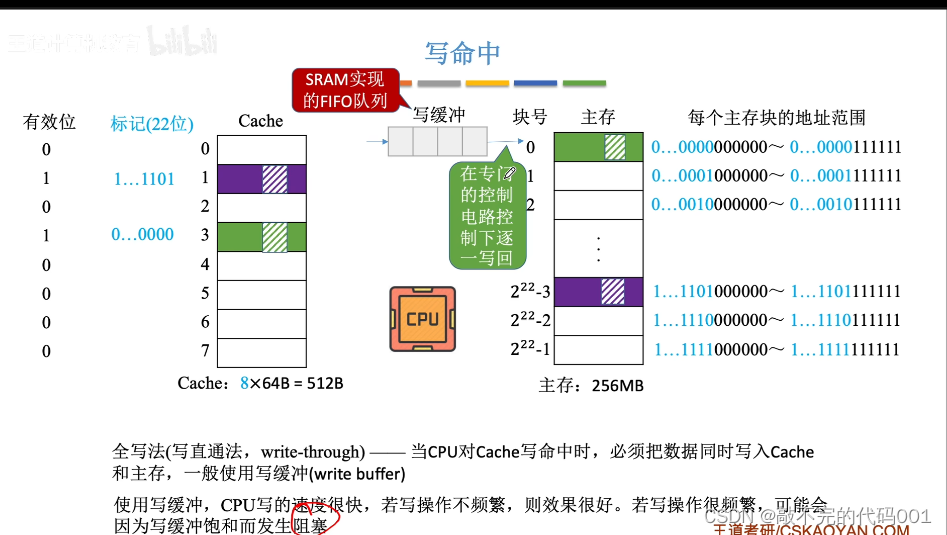

全写法

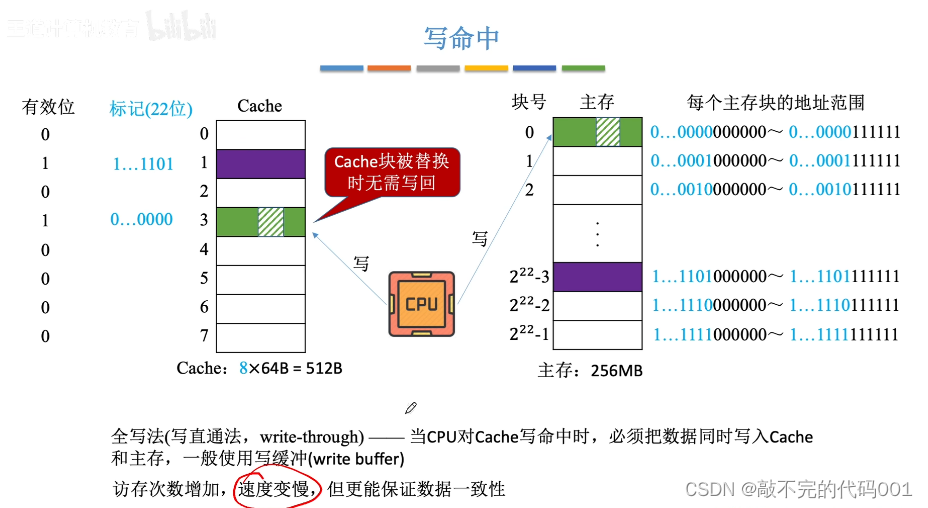

当CPU对Cache写命中时,除了把数据写往Cache外,同时CPU往主存对应的存储单元写入相应的数据,采用这种方法就可以保证Cache和主存的数据基本上都能保存一致,另外当Cache里面的数据被淘汰的时候也不需要写回主存,因为这两边的数据随时都是保持一致的。

采用这种方法表示,每次进行写操作时候,除了访问Cache外也需要进行访存,访存次数增加导致CPU写操作速度变慢

为了减少CPU的访存次数,可以采用这个优化策略

可以增加写缓冲,这个是由SRAM构造的,意味着对写缓冲的读写很快。可以把它看成先进先出的队列

当CPU对某个地址进行写操作并且这个地址命中的时候,首先向Cache写入这个数据,另外也会往写缓冲里写入相应的数据

同理,紫色块也一样

由于写缓冲是由SRAM实现的,所以CPU对写缓冲的写操作比直接往主存里要快得多,然后CPU可以进行其它的操作,比如连续的好几次读操作

在CPU在干其它事情期间,又会有一个专门的控制电路来负责把写缓冲里的写入的数据同步到主存里

采用这种方式,当我们淘汰某个Cache行的时候,也不需要把这个Cache行的数据写回主存。

增加了写缓冲之后,可以使得CPU的写操作/速度变的很快,如果CPU的写操作不频繁的话,采用这种策略效果会很好。如果说写操作很频繁,由于写缓冲容量是有限的所以如果写操作很多就会导致写缓冲饱和,当写缓冲饱和后,CPU就必须阻塞等待

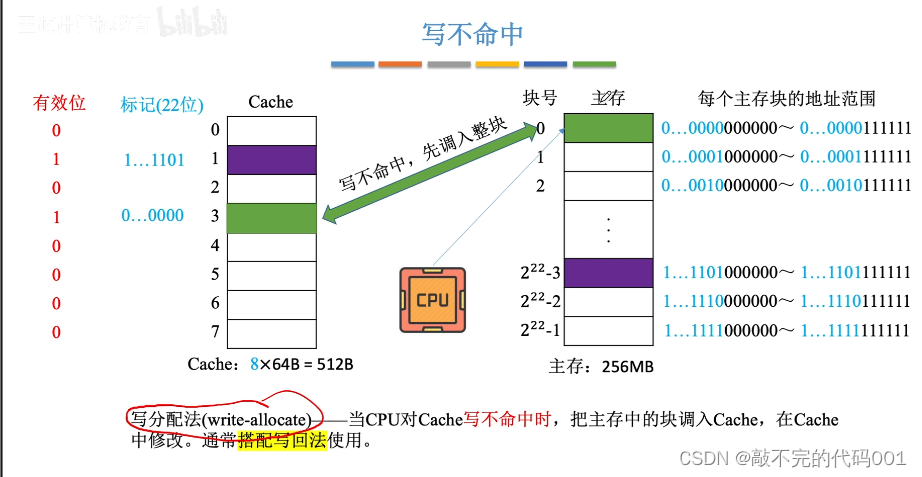

写不命中

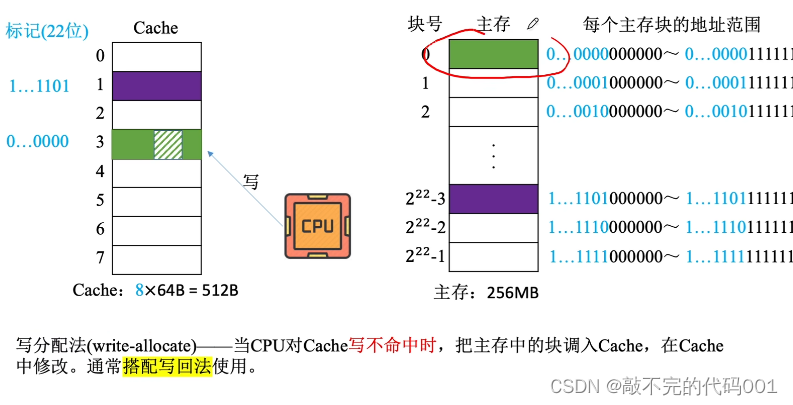

写分配法(搭配写回法)

当CPU要访问的地址没命中,若采用写分配法,就会先把CPU当前要写的这一块数据先调到Cache中,然后CPU对Cache进行写操作,也就是说主存里的数据保持不动,CPU只是修改了其数据副本

这种方式配合“写回法”使用,当Cache被淘汰的时候才把Cache这一整块的内容写回主存里面

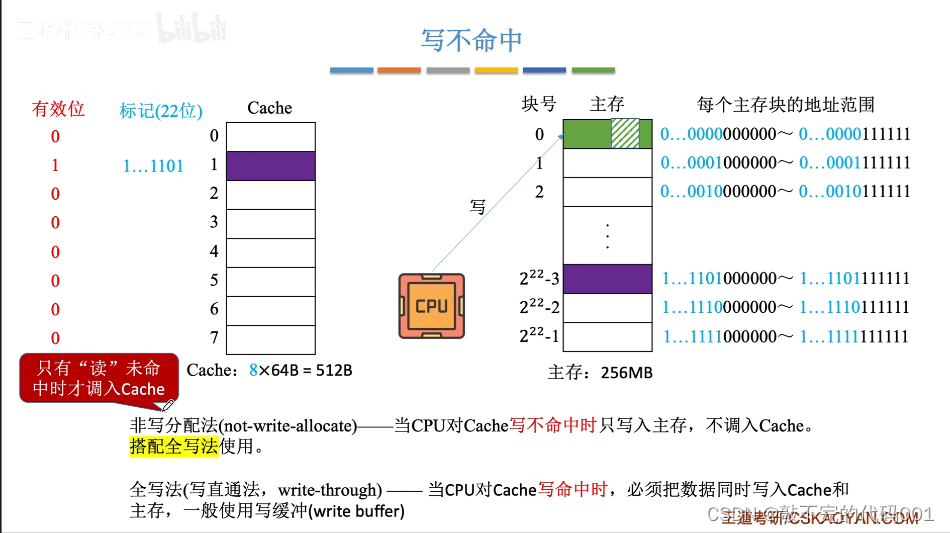

非写分配法(搭配全写法)

当CPU相要写的地址没命中时,此时CPU会直接往主存写数据而不会把这一块的内容调入Cache,所以非写分配法一般搭配之前提到的全写法来使用,采用这种方法的话,意味着只有CPU对某个地址进行读操作,读操作未命中的情况下才会把相应的主存快调入Cache,而写操作未命中, CPU会直接写而不会调入Cache

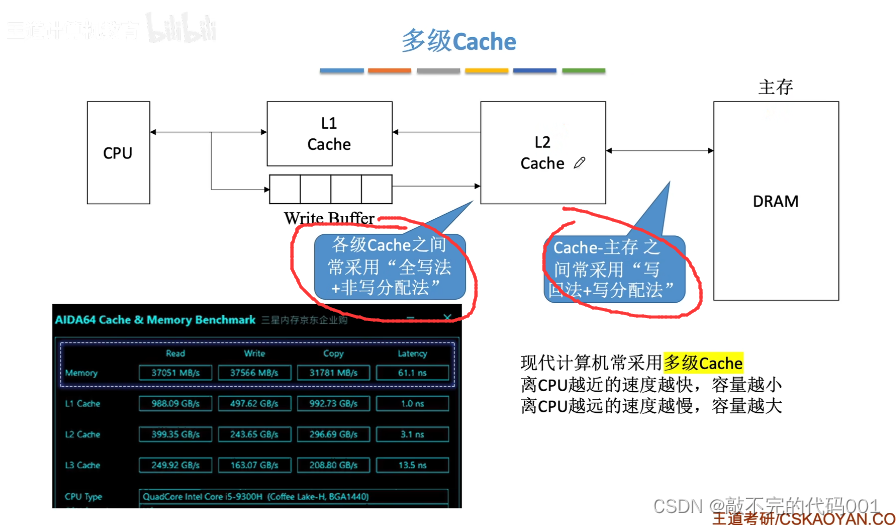

多级Cache

各级Cache之间的作用与Cache与主存之间的作用本质上都是一样的,都是尽可能地降低成本同时提升CPU运行速度

总结

4282

4282

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?