此触发器具有复位信号RSTn,时钟信号CLK,使能信号En,输入信号D,输出信号Q(仅供参考)

工作原理:

初始状态下,触发器处于复位状态,输出为复位信号的稳定状态(通常为0)。使能信号 EN 和输入数据 D 的值不会影响触发器的状态。

当使能信号 EN 为高电平时,D触发器处于使能状态,可以根据时钟信号 CLK 的变化来接收和存储输入数据。

当使能信号 EN 为低电平时,D触发器处于禁止状态,不论时钟信号 CLK 如何变化,都不会对输入数据进行接收或存储。

当时钟 CLK 发生上升沿或下降沿时(取决于D触发器的类型),且使能信号 EN 为高电平时,D触发器根据输入数据 D 来更新其状态。

如果是上升沿触发的D触发器,在时钟上升沿时,输入数据 D 的值将被传递到触发器的输出端 Q 中,即 Q = D。

如果是下降沿触发的D触发器,在时钟下降沿时,输入数据 D 的值将被传递到触发器的输出端 Q 中,即 Q = D。

当复位信号 RESET 为高电平时,无论时钟 CLK 和使能信号 EN 的状态如何,触发器均处于复位状态,输出为复位信号的稳定状态。

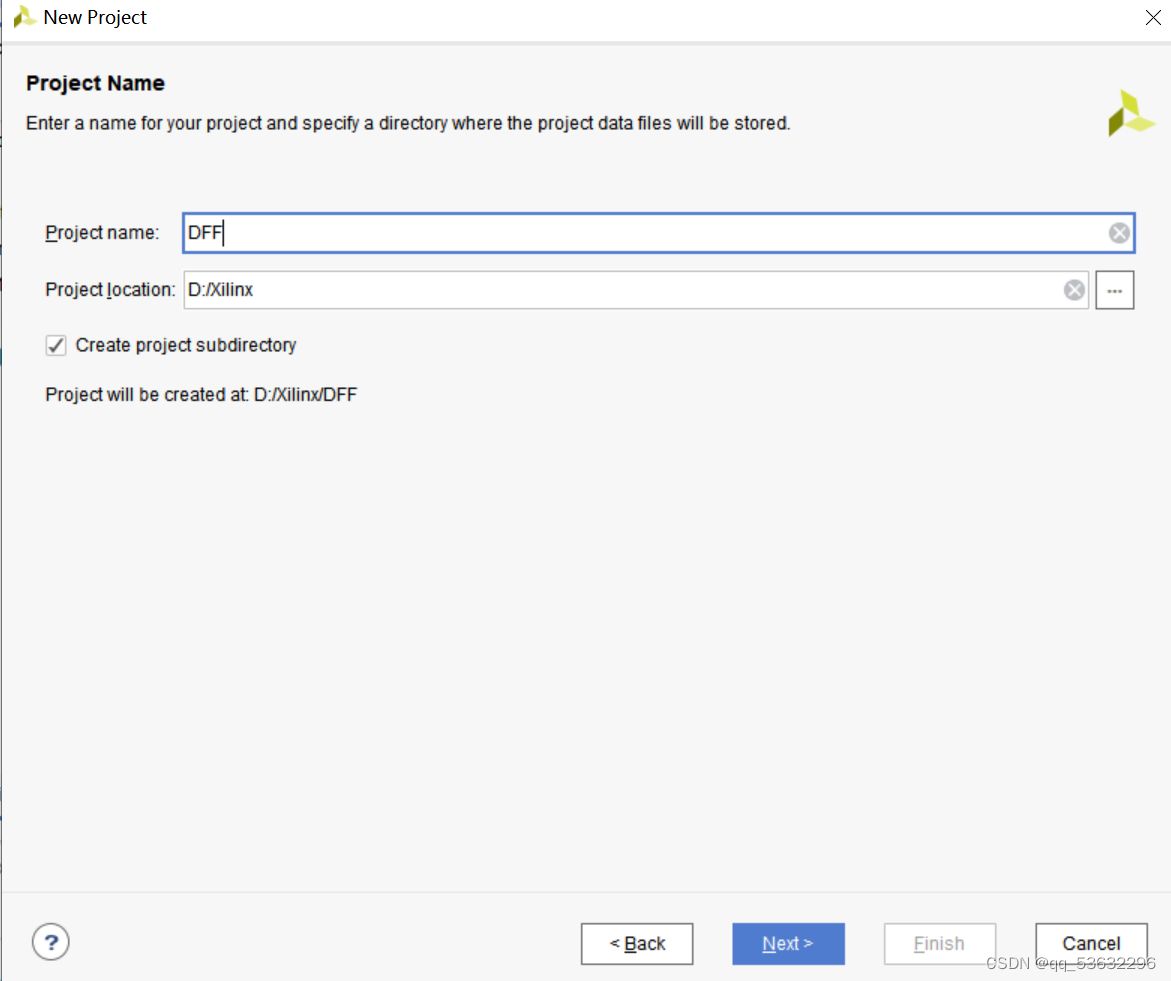

- 建立工程DFF,并新建一个设计文件命名为:DFF

2.打开DFF文件,进行D触发器的模块编码:

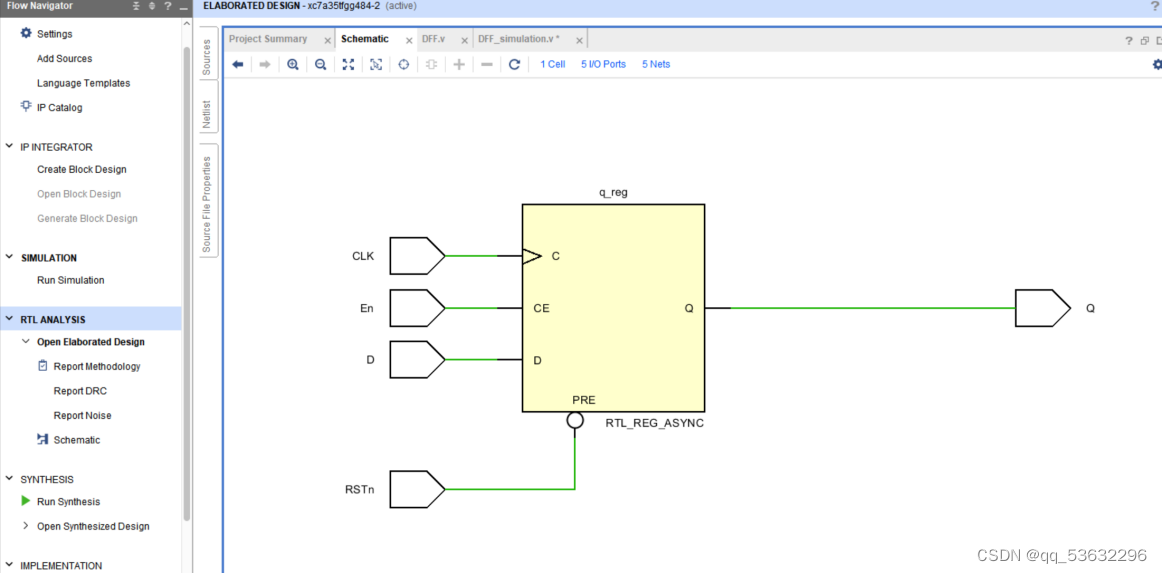

3.点击 RTL ANALYSIS→Open Elaborated Design→Schematic 项,可以查看 RTL 描述后的结构,如下所示:

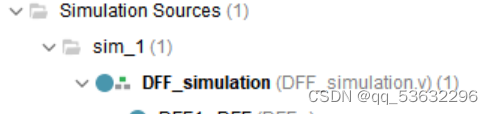

4.新建一个仿真文件命名为DFF_simulation

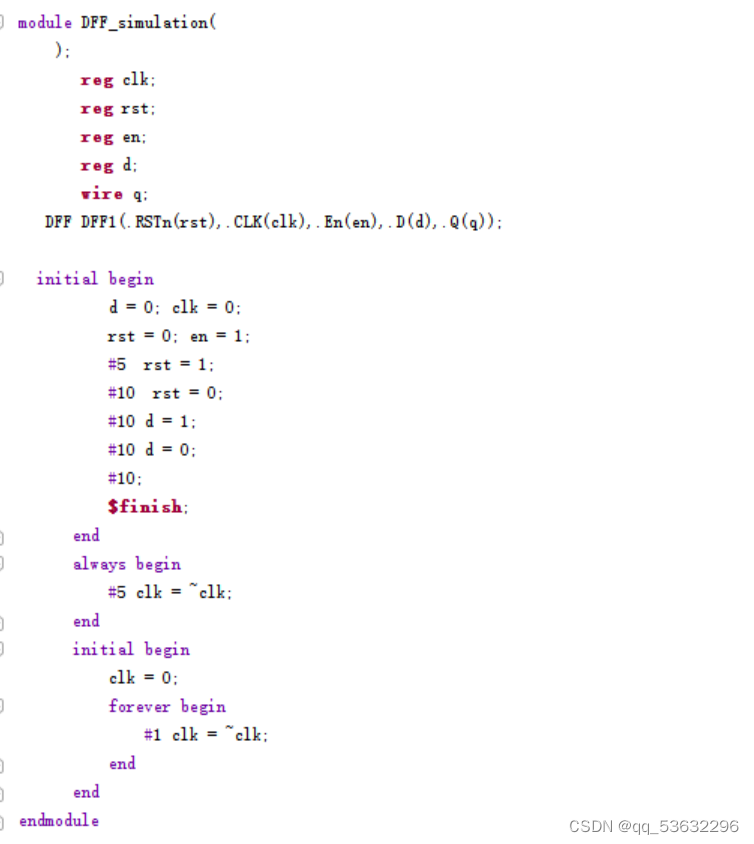

5.点开DFF_simulation进行模块仿真的编码:

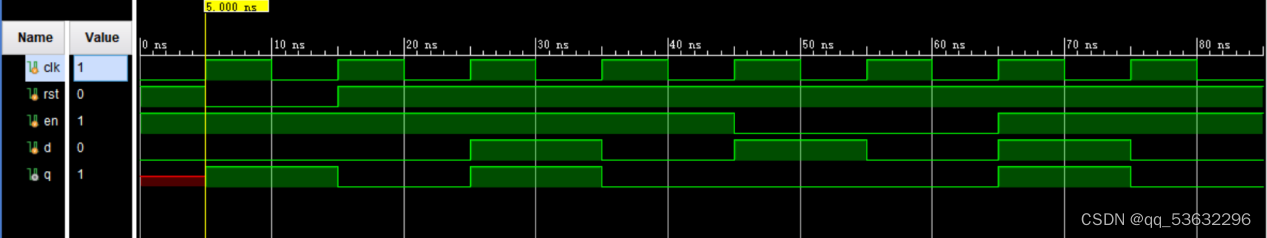

6.点击SIMULATION→Run Simulation→Run Behavioral Simulation进行

仿真,如下所示:

(6)模块设计代码:

module DFF(

input RSTn,

input CLK,

input En,

input D,

output Q

);

wire d,en;

reg q;

assign d=D;

assign Q=q;

assign en=En;

always @(posedge CLK or negedge RSTn) begin

if (!RSTn) begin // 复位有效,将 Q 置为 1

q <= 1;

end else

if (en) begin // 使能有效,将 Q 更新为 D

q <= d;

end else // 否则,Q 保持不变

q <= q;

end

endmodule仿真代码:

module DFF_simulation(

);

reg clk;

reg rst;

reg en;

reg d;

wire q;

DFF DFF1(.RSTn(rst),.CLK(clk),.En(en),.D(d),.Q(q));

initial begin

rst = 1;

clk = 0;

en = 1;

d = 0;

// 等待时钟稳定

#5;

// 激活复位

rst = 0;

#10;

// 取消复位

rst = 1;

// 使能有效,D=1时输入数据

#10; en = 1; d = 1;

#10; en = 1; d = 0;

// 使能无效,数据不更新

#10; en = 0; d = 1;

#10; en = 0; d = 0;

// 使能有效,D=1时输入数据

#10; en = 1; d = 1;

#10; en = 1; d = 0;

// 等待仿真结束

#10; $finish;

end

// 时钟信号生成

always #5 clk = ~clk;

endmodule

本文介绍了D触发器的工作原理,包括复位、使能、时钟信号的作用,以及上升沿和下降沿触发的情况。接着,展示了使用Verilog进行D触发器模块编码和仿真文件的创建过程,包括时钟信号的生成和不同条件下的信号状态变化。

本文介绍了D触发器的工作原理,包括复位、使能、时钟信号的作用,以及上升沿和下降沿触发的情况。接着,展示了使用Verilog进行D触发器模块编码和仿真文件的创建过程,包括时钟信号的生成和不同条件下的信号状态变化。

2187

2187

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?